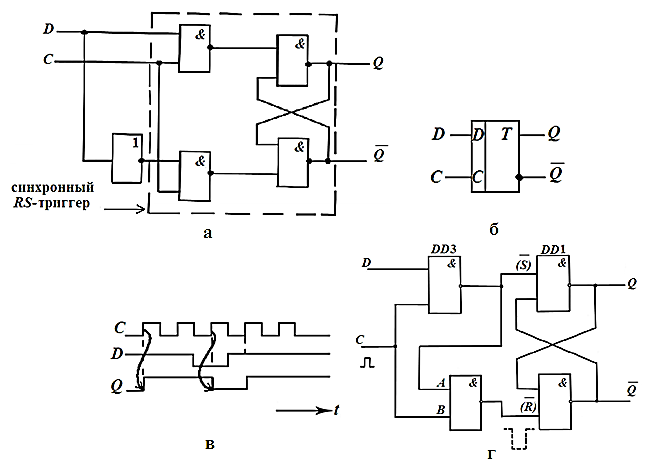

Распространенным вариантом синхронного RS -триггера является D -триггер, схема которого приведена на рисунке 2.12, а.

Она получается из схемы синхронного RS -триггера (рисунок 2.12, а), если на вход S подать сигнал D, а на вход R –

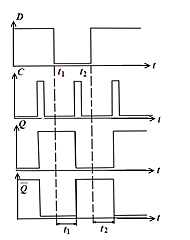

Она получается из схемы синхронного RS -триггера (рисунок 2.12, а), если на вход S подать сигнал D, а на вход R –  введением логического элемента НЕ. Тактовые синхронизирующие импульсы С, разрешающие переключение триггера в строго фиксированные моменты времени выполняют вместе с тем задержку передачи входного сигнала. Временные диаграммы работы D -триггера приведены на рисунке 2.12, б.

введением логического элемента НЕ. Тактовые синхронизирующие импульсы С, разрешающие переключение триггера в строго фиксированные моменты времени выполняют вместе с тем задержку передачи входного сигнала. Временные диаграммы работы D -триггера приведены на рисунке 2.12, б.

| Рисунок 2.12 – Схема (а), условное графическое обозначение (б) и временные диаграммы D -триггера |

Триггер может быть построен с динамическим управлением, когда его переключение происходит в момент изменения управляющего сигнала от «0» к «1» (прямой динамический вход) или от «1» к «0» (инверсный динамический вход). На рисунке 2.12, б приведено условное обозначение D -триггера с прямым динамическим тактовым входом.

| Рисунок 2.13 – D -триггер на логических элементах И-НЕ |

(рисунок 2.13).

Схема D - триггера содержит четыре логических элемента И–НЕ. Здесь элементы DD 1 и DD 2 образуют RS -триггер. Дополнительные элементы DD 3 и DD 4 обращают его в D –триггер. Работает триггер следующим образом. Если D = 1, то при наличии на входе С тактового сигнала С = 1 на выходе DD 3 формируется сигнал, вид которого показан на рисунке 2.13. Сигнал действует на  -триггер подобно сигналу S, и на выходе Q устанавливается напряжение высокого уровня (Q = 1,

-триггер подобно сигналу S, и на выходе Q устанавливается напряжение высокого уровня (Q = 1,  = 0). В этом случае на выходе DD 4 напряжение высокого уровня, поскольку в отсутствие тактового импульса на входе А будет напряжение высокого и на входе В – низкого уровня. С приходом тактового импульса (С = 1) на входе А возникает напряжение низкого, а входе В – высокого уровня.

= 0). В этом случае на выходе DD 4 напряжение высокого уровня, поскольку в отсутствие тактового импульса на входе А будет напряжение высокого и на входе В – низкого уровня. С приходом тактового импульса (С = 1) на входе А возникает напряжение низкого, а входе В – высокого уровня.

Если на вход D подано напряжение низкого уровня на выходе DD 3 будет напряжение высокого уровня, а тактовый импульс (показан на рисунке штрихами), инвертированный логическим элементом DD 4, действует подобно сигналу  . Вследствие этого триггер примет состояние Q = 0 и

. Вследствие этого триггер примет состояние Q = 0 и  = l.

= l.

2015-02-27

2015-02-27 928

928