4.1 Общий вид элемента см. рис З. 082.11ОСБ

4.2 Схема электрическая структурная приведена на рис.2 и

содержит:

МКП - микропроцессор;

СУЗ - схема установки захвата;

ССБР - схема сброса;

САО - схема асинхронного обмена;

ФТИ - формирователь тактовых импульсов;

ШФА - шинный формирователь адресных сигналов;

ШФД - шинный формирователь сигналов данных;

Р/ДС - регистр-дешифратор сигналов состояния микропроцессора;

СВ ЗДМ - схема выдачи запросов доступа к магистрали;

ДША1 - дешифратор сигналов адресных разрядов А7-А0;

ДША2 - - дешифратор сигналов адресных разрядов А15-А12;

СПВС - схема превышения времени связи;

БГШ - блок приоритетного прерывания;

ШФУ - шинный формирователь сигналов управления;

ШФП/В - шинный формирователь сигналов прием-выдача;

ШФП - шинный формирователь вектора прерывания;

D3 - триггер готовности;

D10- триггер прерывания;

D1, D2, D4-D6, DS, D9 - логические схемы "И";

D1 - логическая схема "ИЛИ";

4.3 На схеме приняты следующие условные обозначения и

сокращения:

У ОТВ - управление взведением триггера ответа;

СБР - сброс;

ГТ - готовность;

С - вход синхронизации;

ВПЛ - выполнение (сигнал, стробирующий выдачу сигналов

управления);

ЗАН-занято (сигнал, стробирующий выдачу сигналов адреса

и данных);

ОТВ - ответ со схемы превышения времени связи;

ПЗПР - подтверждение запроса прерывания;

ОТВ 3 - задержанный сигнал ответа;

ГО, Г1 - прямая и инверсная импульсные серии опорной частоты;

Ф1, Ф2 - прямая и инверсная импульсные серии

тактирующей частоты;

Ф1П, Ф2П- прямая и инверсная импульсные серии,

синхронизирующие работу микропроцессора;

ЗХВ - захват;

ПЗХВ - подтверждение захвата;

РЗП - разрешение прерывания;

ВК - выбор кристалла;

УВ - управляющий вход;

П - код уровня прерывания;

СРП - строб разрешения прерывания;

РЗ - разрешение записи байта программного приоритета;

ЗП1-ЗП7 - запрос прерывания 1-7 уровня блока

приоритетного прерывания БПП;

4.4 Микропроцессор осуществляет управление обменом информацией по интерфейсной магистрали, а также вычисляет логические и арифметические операции.

Основные технические характеристики и принцип работы микропроцессора КР580ИК80А (К580ИК80) приведены в приложении 1.

Схема СУЗ предназначена для синхронизации момента поступления сигнала ЗХВ на микропроцессор. Кроме того, по сигналу ОСТ схемой СУЗ осуществляется останов выполнения программы микропроцессором.

Схема ССБР предназначена для синхронизации момента поступления сигнала СБР на микропроцессор.

Синхронизирующей частотой для схем СУЗ и ССБР является Ф2П.

ФТИ предназначен для формирования тактирующих сигналов ГО, Г1, Ф1, Ф2, Ф1П, Ф2П, обеспечивающих синхронизацию работы микропроцессора и внешних схем. Электрическая функциональная схема ФТИ приведена на рис. 3 и состоит из генератора Г, триггера-делителя частоты D1, Инвертора D2, коньюкторов D3-D5и элемента задержки D6. Временные соотношения между сигналами сигналов ГО, Г1, Ф1, Ф2, Ф1П и Ф2П приведены на рис. 4.

Схема САО (см. рис. 5) обеспечивает синхронизацию открывания шинных формирователей ШФА, ШФД, ШФУ и ШФП/В в соответствии с диаграммой работы МКП в режимах ЧТН (ПРМ), ЗАП (ВДЧ), также обеспечивает управление выдачей сигналов ГТ и ЗДМ. Схема электрическая функциональная приведена на рис. 5. Временная диаграмма, поясняющая работу САО приведена на рис. 6. В состав САО входят: триггер занятия шин адреса и данных D1, триггер выполнения установленного режима D2 и вспомогательный триггер задержанного сигнала выполнения D3, триггер фиксации ответного сигнала D5, вспомогательный триггер задержанного сигнала ответа 2)4, триггер, вырабатывающий строб останова по адресу D1, сбросом которого управляет схема ИЛИ (D6). Синхронизирующими частотами для схемы САО являются ГО, Г1, Ф1, Ф2. Сигнал ЗАН, открывающий ШФА, ШФД (см рис. 2), устанавливаются в середине такта Т2; сигнал ВПЛ, открывающий ЩФУ ШФП/В - в конце Т2. Съем сигналов ЗАН и ВПЛ производится в такте ТЗ только при наличии сигнала ответа ОТВ.

ШФА (см. рис. 2) представляет собой выходные усилители с тремя устойчивыми состояниями и предназначен для формирования адресных сигналов А15-А0, выдаваемых в интерфейсную магистраль.

ШФД представляет собой двунаправленные усилители с тремя устойчивыми состояниями, предназначенные для обмена информацией микропроцессора с памятью и элементами ввода-вывода.

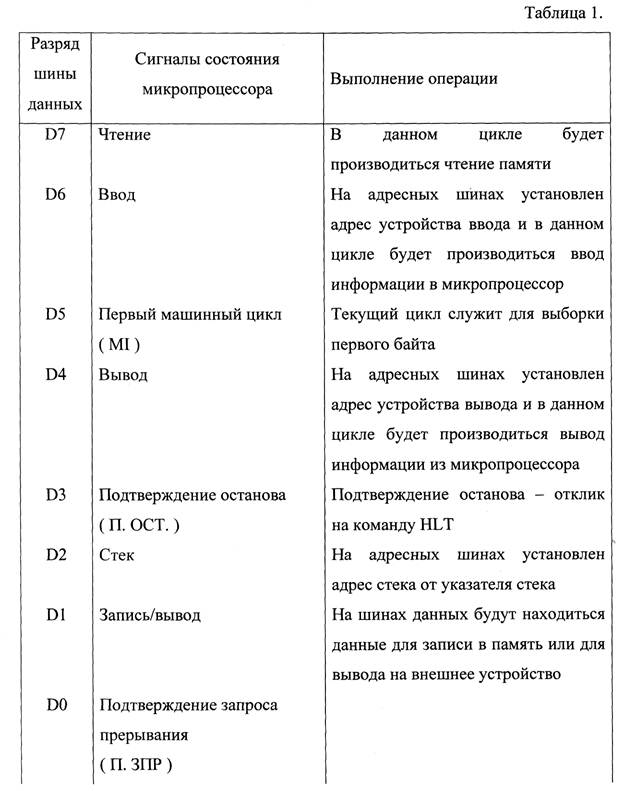

Регистр - дешифратор состояния Р/ДС осуществляет прием, хранение и дешифрацию байта состояния микропроцессора, передаваемого по шинам данных. Сигналы состояния микропроцессора приведены в табл. 1. Синхронизация записи кода в Р/ДС осуществляется сигналами ФШ, СИНХР, поступающими на вход 0. На выходе СВ регистра Р/ДС образуется сигнал ФШСИНХР.

Схема СВ ЗДМ предназначена для формирования сигналов запроса доступа к интерфейсной магистрали. Электрическая функциональная схема СВ ЗДМ представлена на рис. 7 и состоит из синхронизирующего триггера D1, устанавливаемого в состояние "1" сигналом Ф1ПСИНХР и сбрасываемого в "0" положительным фронтом сигнала ОТВЗ. Сигнал запроса (ЗДМ2), получаемый на выходе СВ ЗДМ, образуется при совпадении на схеме "И" (D2) сигналов А15 и сигнала с выхода триггера D\. Сигналы запроса (ЗДМЗ-ЗДМ7) образуются как дизъюнкция сигналов с выходов схем "И" (£>3;£>4).

Адресный сигнал с ДША1 (см. рис. 2) поступает на БПП во время записи в этот блок кода уровня прерывания, при этом адресные разряды А7-А0 закодированы логическими нулями. Стробирует работу ДША1 сигнал ВДЧ. Дешифратор ДТТТА2 устанавливает на своем выходе сигнал логической "1" при обращении микропроцессора к элементам ввода-вывода управляющими сигналами ЗАП, ЧТН. При этом адресные разряды А15-А12 закодированы логической "1". Работу ДША2 блокирует сигнал ПРМ \/ ВДЧ. Схема электрическая функциональная СПВС (рис. 8) формирует сигнал ЗП6 запроса прерывания в БПП при существовании сигнала ВПЛ более 25 мкс, что свидетельствует об отсутствии сигнала ОТВ. В состав схемы входит формирователь Ф (D\), дешифратор вектора прерывания ДС {D2), схема "И" (Z)3); триггеры: превышения времени связи DA и запроса прерывания D5. Временные диаграммы работы СПВС приведена на рис. 9. По положительному фронту сигнала ВПЛ формирователь Ф должен вырабатывать импульс, равный по длительности сигналу ВПЛ (при длительности ВПЛ не превышающей 25мкс) и импульс длительностью 25 мкс при длительности ВПЛ, превышающей 25мкс. Сигнал ВПЛ воздействует на 5-вход триггера D4, а импульс с выхода формирователя D\ через схему "И" (D3) действует на вход С синхронизации этого триггера. На схему "И" (D3) поступает также сигнал блокировки ОСТ. В пределах времени длительности ВПЛ до 25мкс по заднему фронту импульса от формирователя Ф триггер D4 должен установиться в "О", однако одновременно с этим на s-входе триггера DA будет воздействовать нулевой потенциал закончившегося сигнала ВПЛ, запрещающий переброс триггера D4 в ноль. Таким образом, триггер D4 из единичного состояния не выйдет. При превышении времени длительности сигнала ВПЛ более 25мкс по заднему фронту импульса от Ф (D1) триггер D4 установиться в ноль. Сигнал с выхода D4 взведет триггер D5. Сигнал с выхода D5 в качестве запроса прерывания поступит в БПП. После расшифровки запроса прерывания на выходе БПП установится код соответствующего вектора прерывания, который распознается дешифратором ДС (D2) и по сигналу ПЗПР-ВПЛ считывания микропроцессором вектора прерывания в сигнал с выхода D2 установит триггер D5 в ноль. Начальный сброс триггера D5 осуществляется сигналом СБР.

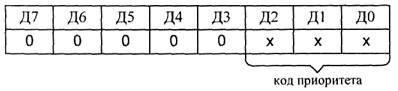

Блок приоритетного прерывания БПП (см. рис. 2) предназначен для анализа запросов связи элементов ввода-вывода, формирования векторов прерывания (команд R S Т) и выдачи сигнала запроса прерывания микропроцессору. БПП обеспечивает возможность программного изменения приоритетов запросов связи. Изменение приоритета осуществляется обращением к ВПП, как к элементу ввода-вывода с адресом 00 и засылкой в него байта программного приоритета.

|

|

Код приоритета 000 - соответствует самому младшему приоритету.

Шинный формирователь сигналов управления ШФУ представляет собой выходные усилители с тремя устойчивыми состояниями и предназначен для формирования сигналов управления из сигналов состояния, помещенных в Р/ДС.

Шинный формирователь сигналов приема-выдачи ШФП/В представляет собой выходные усилители с тремя устойчивыми состояниями и предназначен для ретрансляции сигналов управления ЗАЛ и ЧТН на шины сигналов управления ВДЧ и ПРМ, соответственно; что необходимо при обращении к элементам ввода-вывода, как к ячейкам памяти.

Шинный формирователь сигналов кода вектора прерывания ШФП представляет собой выходные усилители с тремя устойчивыми состояниями и предназначен для выдачи вектора прерывания от БПП в интерфейсную магистраль.

Триггер готовности D3 обеспечивает формирование сигнала ГТ, указывающего на готовность информации к вводу в микропроцессор или готовность элемента ввода-вывода или памяти к приему информации. Сигнал Гт позволяет синхронизировать работу МКП с внешними устройствами различного быстродействия.

Триггер запроса прерывания D10 служит для фиксирования запроса прерывания на время, достаточное для окончания микропроцессором инструкции произвольной длительности и приема вектора прерывания в цикле обработки прерывания.

Логическая схема "И" QD1) обеспечивает блокировку сигналов ответа с выхода схемы "ИЛИ" (D7) сигналом ОСТ.

Логическая схема "И" (D2) обеспечивает блокировку сигнала запроса прерывания сигналом БЛ ПРЕР.

Логическая схема «И» (D4) обеспечивает блокировку сигнала ЗАН сигналом ПЗХВ от микропроцессора.

Логическая схема «И» (D5) обеспечивает блокировку сигнала ЗАН сигналом Б Л АУ.

Логическая схема «И» (D6) обеспечивает конъюнкцию сигналов ВПЛ иВЗППР.

Логическая схема «ИЛИ» (D7) обеспечивает дизъюнкцию: ответных сигналов внешних устройств, ответа при обращении к БПП, ответа при считывании кода вектора прерывания и ответа по превышению времени

связи для осуществления обработки прерывания по превышению времени связи.

4.5.Режим работы элемента.

4.5.1. Программный режим обмена

4.5.1.1. В режиме программного обмена по интерфейсу элемент выполняет следующие операции:

1). Чтение, прием;

2) Запись, выдачу.

Временная диаграмма сигналов при выполнении элементом операции чтение, прием приведена на рис. 10.

В начале каждого машинного цикла в такте Т.1 микропроцессор вырабатывает сигнал СИНХР. Во время действия этого сигнала информация о состоянии микропроцессора выдается на шины данных и записывается в Р/ДС (см. рис. 2) по совпадению сигналов Ф1 и СИНХР, поступающих на входы синхронизации Р/ДС. Сигналом Ф1 СИНХР, получаемым на выходе СВ Р/ДС триггер готовности D3 устанавливается в ноль.

В такте Т2 по окончании сигнала СИНХР - микропроцессор устанавливает сигнал ПРИЕМ. Сигнал ПРИЕМ поступает на вход УВ формирователя ШФД.

Сигналом ПРИЕМ должно производиться переключение ШФД в режим приема информации с интерфейсной магистрали. Сигналом ЗАН с выхода схемы САО, прошедшим схемы «И» (D4,D5), открываются ШФД и ШФА на прием и выдачу, соответственно

Сигнал ВПД, поступающий с выхода схемы САО на схемы «И» (D8, Б9),стробирует выдачу интерфейсного сигнала ЧТН (ПРМ) шифраторами ШФУ и ШФП/В.

По сигналу ПРМ или ЧТН адресованное периферийное устройство или память выдает информационные сигналы по шинам Д7-Д0, сопровождая их сигналом ответа ОТВ.

Сигнал ОТВ, пройдя схему сборки D7 и совпадения D1, поступает в САО на взведение триггера ответа D5 (см рис. 5). Сигнал ОТВ с выхода схемы САО должен установить триггер готовности D3 в единичное состояние.

С выхода D3 на микропроцессор подается сигнал готовности ГТ, по которому микропроцессор принимает данные с шин Д7-Д0 и переходит для работы втакт ТЗ.

В такте ТЗ микропроцессор снимает сигнал прием, схема САО снимает сигналы ВПЛ и ЗАН, что приводит к отключению адресных и информационных шин и управляющих сигналов от интерфейсной магистрали.

При этом адресуемое периферийное устройство или память производит отключение сигналов данных Д7-Д0 и сигнала ОТВ от интерфейсной магистрали. На этом цикл обмена информацией заканчивается.

4.1.2. Работа микропроцессора в такте Т1 при выполнении операции

запись, выдача аналогична работе в такте Т1 при выполнении операции

чтение, прием.

Временная диаграмма сигналов при выполнении элементом операции запись, выдача приведена на рис. 11.

В такте Т2 микропроцессор выдает на шины данных информационные сигналы, предназначенные для записи их во внешнее устройство.

Схема САО как и при выполнении операции чтение, прием вырабатывает сигналы стробировки ЗАН и ВПЛ. Сигналом ЗАН к интерфейсной магистрали подключаются посредством ШФА и ШФД адресные и информационные шины микропроцессора. Сигналом ВПЛ стробируется выдача на интерфейсную магистраль сигналов ЗАП (ВДЧ).

В том же такте Т2 МКП анализирует состояние триггера готовности D3. Но, т.к. триггер D3 находится в нулевом состоянии. То МКП переходит в состояние ожидания Тож.

Адресуемое внешнее устройство (память или элемент ввода-вывода) выдает сигнал ОТВ и осуществляет прием информационных сигналов из интерфейсной магистрали. Сигнал ОТВ, пройдя схему сборки D7 и совпадения D1, поступает в схему САО на взведение триггера ответа D5(cm. рис. 5). Сигнал ОТВ с выхода схемы САО устанавливает триггер готовности D3 в единичное состояние и на микропроцессор поступает сигнал готовности ГТ. По сигналу ГТ микропроцессор переходит в такт ТЗ.

В такте ТЗ схема САО сбрасывает сигналы ЗАН, и ВПЛ, что приводит к отключению адресных и информационных шин и сигнала ЗАП (ВДЧ) от интерфейсной магистрали, что в свою очередь вызывает сброс сигнала ОТВ внешним устройством.

На этом цикл обмена информацией заканчивается.

4. 5. 2. Режим организации связи по прерыванию.

Сигналы запросов прерывания ЗПР1-ЗПР7 поступают на блок приоритетного прерывания Б1111. При наличии сигнала РЗП от микропроцессора и сигнала ЗПР, приоритет которого выше программно установленного, блок БПП выдает сигнал ЗП и формирует код вектора прерывания, соответствующий принятому уровню прерывания.

Сигнал ЗП устанавливает триггер запроса прерывания D 10 в единичное состояние. При отсутствии блокировки прерывания сигнал с выхода D 10 через схему «И» (D2) поступает на вход ЗПР микропроцессора.

Микропроцессор в конце выполнения текущей команды производит анализ сигнала ЗПР и при наличии разрешения прерывания организует связь с БПП для приема вектора прерывания.

Временная диаграмма сигналов при работе элемента в режиме организации связи по прерыванию приведена на рис.12.

В такте Т1 микропроцессор выдает на шины данных код состояния, в котором присутствует сигнал ПЗПР (подтверждение запроса прерывания).

Сигналом Ф1П- СИНХР код состояния микропроцессора заносится в Р\ДС. При этом схема «И» (D6) подготавливается по одному из входов сигналом ПЗПР.

В такте Т2 схема САО вырабатывает сигнал ВПЛ. При совпадении сигналов ПЗПР и ВПЛ на выходе схемы «И» (D6) формируется сигнал,

открывающий ШФП, тем самым осуществляется подключение к интерфейсной магистрали вектора прерывания. Кроме того, с выхода D6 выдается сигнал ответа на схему «ИЛИ» (D7) и управляющий сигнал в схему

спвс.

Сигнал ответа из интерфейсной магистрали поступает в схему САО, которая вырабатывает сигнал ОТВ на взведение триггера готовности D3.

После анализа сигнала ГТ микропроцессор принимает вектор прерывания и переходит в такт ТЗ.

В такте ТЗ схема САО снимает сигнал ВПЛ. Это вызывает переключение D6, в результате чего происходит отключение вектора прерывания от интерфейсной магистрали (ШФП переходит в состояние с высоким выходным импедансом) и сброс триггера запроса прерывания D10 в нулевое состояние.

После приема вектора прерывания микропроцессор осуществляет переход на выполнение программы прерывания.

Запрос прерывания может быть выдан в БПП также схемой превышения времени связи СПВС, если сигнал ответа ОТВ не поступит по какой-либо причине в течение 25 мкс после выдачи схемой САО сигнала ВПЛ.

4.5.3. Элемент обеспечивает возможность доступа к внутриблочной магистрали в режиме захвата микропроцессора и в режиме разделения времени связи.

4.5 3hi В режиме захвата микропроцессора элемент обеспечивает возможность (без применения дополнительных аппаратных средств) организовывать непосредственный доступ к внутриблочной магистрали одного дополнительного активного устройства (выполняющего функции задатчика).В этом случае подключаемое активное устройство для организации доступа использует сигналы ЗДМ1, РДМ1 интерфейсной магистрали. Запрос доступа к магистрали (ЗДМ1), выдаваемый активным устройством поступает на схему СУЗ элемента. СУЗ формирует сигнал захвата ЗХВ микропроцессора. Микропроцессор анализирует сигнал ЗХВ и после завершения очередного цикла обращения к памяти или элементам ввода-вывода входит в режим захвата, устанавливая при этом сигнал подтверждения захвата ПЗХВ. После этого микропроцессор не выполняет никаких операций, пока присутствует сигнал ЗХВ.

Сигналом ПЗХВ осуществляется блокировка включения шинных формирователей ШФА и ШФД. Кроме, того, ПЗХВ ретранслируется в интерфейсный сигнал разрешения доступа к магистрали РДМ1, по которому активное устройство начинает производить операции по обмену информацией.

После завершения обмена информацией активное устройство снимает сигнал ЗДМ1, что в свою очередь вызовет съем сигнала ЗХВ. После окончания действия этого сигнала микропроцессор продолжит свою работу.

Режим захвата микропроцессора используется при подключении панели контроля и отладки KB 95.03 (или аналогичных устройств, например, прибора контроля и отладки KB 95. 04).

4.5.3.2. В режиме с разделением времени элемент использует интерфейсную магистраль только на время цикла обмена информацией. В течение времени выполнения операций непосредственно в самом микропроцессоре интерфейсная магистраль свободна и в это время может быть использована другими активными устройствами (в том числе элементами управления) для организации обмена информацией.

Элемент в этом режиме получает доступ к интерфейсной магистрали на тех же основаниях, что и другие активные устройства.

Каждое обращение элемента к интерфейсной магистрали сопровождается выдачей сигнала ЗДМ (см. рис. 7), формируемого схемой СВЗДМ, и только по получению соответствующего РДМ, запускается схема асинхронного обмена С АО.

Если элемент требует доступа к магистрали, а она занята другим активным устройством, то микропроцессор входит в режим ожидания. При этом все сигналы (адреса, данные, управляющие) для обмена подготовлены, и как только магистраль освободится, будет произведен цикл обмена.

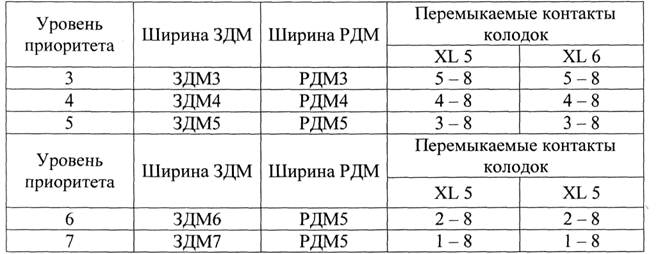

Задание элементу требуемого приоритета осуществляется перемычками согласно табл. 2.

Таблица 2.

Примечания: 1. Шины ЗДМ1, РДМ1 используются для подключения панели контроля и отладки KB 95. 03.

2. Шины ЗДМ2, РДМ2 используются для организации межблочного обмена.

2015-03-07

2015-03-07 797

797