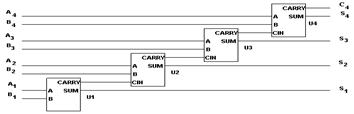

Арифметические сумматоры – составная часть арифметико-логических устройств (АЛУ) микропроцессоров (МП). Арифметический сумматор состоит из двух устройств: полусумматора и n полных сумматоров. Полный сумматор имеет три входа: A, B – входы суммируемых операндов, Ci – вход переноса из предыдущего разряда сумматора и два выхода: S – выход полного сумматора и C 0 – выход переноса. Полусумматор отличается от полного тем, что у него нет входа переноса из предыдущего разряда. Полусумматор используется в качестве первого разряда арифметического сумматора, а в качестве остальных разрядов – полные сумматоры (рис. 14). Полусумматор – одна из простейших комбинационных логических схем.

Рис. 15. Четырехразрядный арифметический сумматор

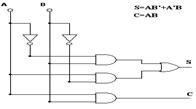

Рассматривая таблицу истинности полусумматора (табл. 12) можно заметить, что выход S полусумматора выполняет функции элемента «ИСКЛЮЧАЮЩЕЕ ИЛИ», а выход переноса С полусумматора – элемента «И». Таким образом, логические выражения для функций S и C равны:

S=AB ′ +A ′ B, C=AB.

Т а б л и ц а 12

| Входы | Выходы | ||

| А | В | S | C |

Схема полусумматора представлена на рис. 15.

Рис. 16. Структура полусумматора

2015-03-22

2015-03-22 458

458