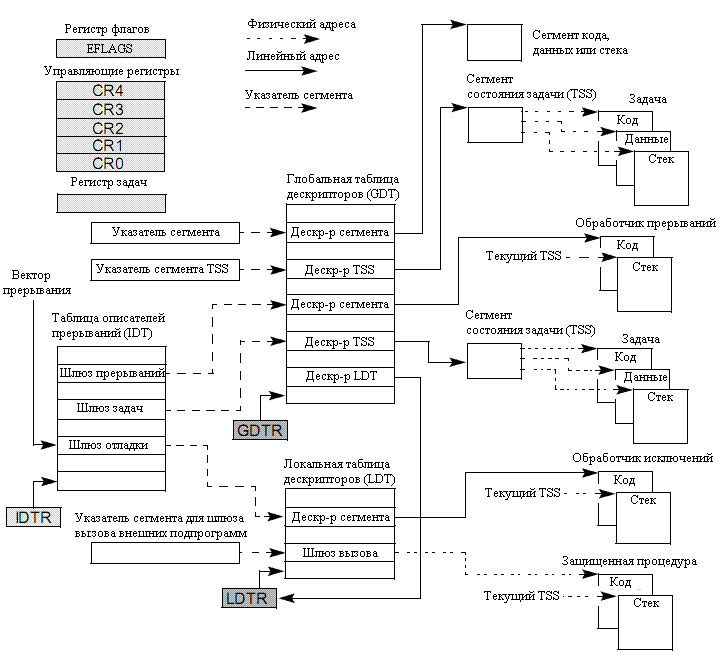

Аппаратные средства микропроцессоров семейства IA-32, относящиеся к системному уровню, представлены на рисунке 26.

При работе в защищенном режиме доступ к памяти осуществляется либо с помощью глобальной таблицы дескрипторов, либо с помощью локальной таблицы дескрипторов. Эти таблицы содержат описатели (дескрипторы) сегментов, которые представляют собой структуру данных, содержащую базовые адреса сегментов, права доступа, тип и иную информацию.

Каждый описатель сегмента имеет соответствующий селектор сегмента, который обеспечивает использующее его программное обеспечение указателем на дескриптор сегмента, флаг типа таблицы (локальная или глобальная) дескрипторов, информацию о правах доступа.

Для доступа к ячейке памяти используется селектор сегмента и смещение. Селектор сегмента обеспечивает доступ к описателю сегмента, в котором содержится базовый адрес сегмента в линейном адресном пространстве. Смещение определяет расположение ячейки памяти относительно базового адреса.

Необходимо отметить, что селектор сегмента, сам по себе, определяет смещение описателя сегмента относительно базового адреса таблицы дескрипторов. Базовый адрес глобальной таблицы дескрипторов находится в регистре GDTR, а локальной таблицы дескрипторов - LDTR.

Кроме кода, данных и сегмента стека, формирующих исполнительную среду программы или процедуры, определены ещё 2 системных сегмента: сегмент состояния задачи (Task-State Segment, TSS) и локальная таблица дескрипторов. Глобальная таблица дескрипторов не рассматривается в качестве сегмента, поскольку к ней не осуществляется доступа с помощью селектора сегмента и описателя сегмента. В отличие от глобальной таблицы дескрипторов, локальная таблица дескрипторов и сегмент состояния задачи имеют соответствующие описатели сегментов. Кроме них, архитектура процессора IA-32 определяет еще и набор специальных описателей, называемых шлюзами (шлюз вызова процедур, шлюз прерываний, шлюз отладки и шлюз задачи). Они обеспечивают защищенное обращение к системным процедурам и обработчикам, которые могут выполняться на уровне привилегий, отличном от того, на котором выполняется вызывающее их приложение. Например, команда CALL через шлюз вызова может обеспечить доступ к процедуре, выполняющейся на более привилегированном уровне. Если доступ к данной функции приложению разрешен, то процессор считывает селектор сегмента кода и смещение внутри этого сегмента вызываемой процедуры из шлюза вызова. При этом при необходимости процессор переключается в иной уровень привилегий.

Рисунок 5 - Архитектура IA-32 системного уровня Рисунок 5 - Архитектура IA-32 системного уровня |

Сегмент состояния задачи определяет состояние исполнительной среды для задачи. Он включает в себя состояние РОНов, сегментных регистров, регистра флагов EFLAGS, состояние счетчика команд (EIP) и селектор сегмента с указателями стеков для трех сегментов стека (по одному стеку на каждый уровень привилегий). TSS также включает в себя селектор сегмента для LDT, соответствующий данной задаче и базовый адрес таблицы страниц.

Все программы, выполняемые в защищенном режиме, связаны с контекстом задачи. Селектор сегмента для TSS текущей задачи хранится в регистре задачи. Простейший способ переключиться на другую задачу заключается в вызове или переходе на новую задачу. Для этого, в качестве параметра, команде CALL или JMP передается селектор сегмента новой задачи. При переключении задач, процессор выполняет следующие действия:

1. Сохраняет состояние текущей задачи в текущий TSS.

2. Загружает в регистр задачи селектор сегмента новой задачи.

3. Осуществляется доступ к новому TSS посредством описателя сегмента в GDT (на него указывает селектор сегмента).

4. Загружается состояние новой задачи из нового TSS в РОНы, сегментные регистры, LDTR, управляющий регистр CR3 (в нем хранится базовый адрес таблицы страниц), регистр флагов EFLAGS и счетчик команд EIP.

5. Начинается выполнение новой задачи.

Задачу можно вызвать и через шлюз задач. При этом процедура аналогична, с тем лишь исключением, что шлюз задач обеспечивает доступ к TSS раньше, чем к сегменту кода (посредством селектора сегмента, находящегося в составе шлюза задачи).

Внешние прерывания, прерывания и исключения, формируемые программным обеспечением идентифицируются с помощью таблицы дескрипторов прерываний (или таблицы векторов прерываний, Interrupt Descriptor Table, IDT). IDT хранит набор шлюзов, которые обеспечивают доступ к обработчикам прерываний и исключений. Как и GDT, таблица дескрипторов прерываний не является сегментом. Линейный базовый адрес IDT находится в регистре IDTR. Смещением относительно базового адреса служит номер (вектор) прерывания. Вызов процедуры обработки прерывания аналогичен вызову процедуры через соответствующий шлюз.

Системная архитектура поддерживает либо прямое обращение по физическому адресу к ячейке памяти, либо обращение с использованием механизма виртуальной памяти к страницам памяти. В последнем случае, на страницы памяти отображаются не только сегменты кода, данных и стека пользовательских приложений, но и системные сегменты (а также GDT и IDT). Размещение страниц в физической памяти определено в двух системных структурах данных: каталоге страниц и таблице страниц. Обе эти структуры находятся в физической памяти. Базовый адрес каталога страниц находится в управляющем регистре CR3. Элемент каталога страниц содержит физический адрес таблицы страниц, права доступа и информацию, необходимую для управления памятью. Элемент таблицы страниц содержит физический адрес страницы, права доступа к странице и информацию, необходимую для управления памятью. Для реализации этого механизма, линейный адрес делится на 3 части: смещение (индекс) в каталоге страниц, смещение в таблице страниц и смещение ячейки памяти относительно начала страницы (рисунок 4). Система может иметь только один каталог страниц или несколько. Например, каждая задача может иметь собственный каталог страниц.

2015-03-08

2015-03-08 1486

1486