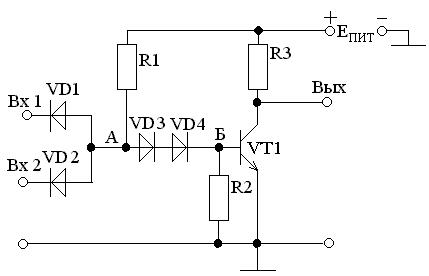

Принципиальная схема диодно-транзисторной логики (ДТЛ) изображена на рисунке 1.5. Число входов можно увеличить, подключая диоды параллельно VD1 и VD2, но в этом случае усложнится анализ схемы.

Рисунок 1.5

Предположим, что ЕПИТ =5 В. Тогда, если БТ закрыт (ток через него отсутствует), напряжение на выходе будет равно 5 В, что соответствует логической ²1² (U1=5 B). Если БТ находится в режиме насыщения, то на его выходе будет напряжение примерно равное 0,1 В, это соответствует логическому ²0² (U0=0,1 B). Принцип работы схемы поясним при помощи таблицы 1.7

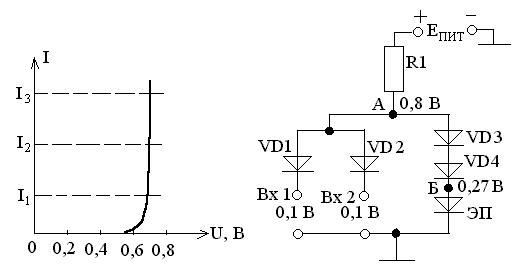

Если на оба входа подано напряжение U0=0,1 В (рисунок 1.6 б), тогда напряжение в точке А будет равно UА= 0,8 В. Оно состоит из входного напряжения U0 и падения напряжения на диоде, которое примерно равно

Таблица 1.7

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | UА, В | UБ, В | БТ | UВЫХ, В | Вых |

| 0,1 | 0,1 | 0,8 | 0,27 | Закр | ||||

| 0,1 | 0,8 | 0,27 | Закр | |||||

| 0,1 | 0,8 | 0,27 | Закр | |||||

| 2,1 | 0,7 | Откр | 0,1 |

0,7 В. Характеристика диода, выполненного на основе кремния, приведена на рисунке 1.6 а. Из рисунка видно, что при различных токах I1, I2, I3 падение напряжения на диоде примерно составляет 0,7 В.

Предполагая, что все три pn-перехода VD 3, VD 4 и эмиттерный переход (ЭП) транзистора одинаковы, получаем напряжение на базе транзистора (точка Б) составляет UБ =UА/3» 0,27 В. Входная характеристика транзистора соответствует характеристики pn-перехода (рисунок 1.6а), и, следовательно, ток базы отсутствует, ток коллектора равен нулю, транзистор закрыт. Напряжение на выходе будет около 5 В. Падением напряжения на резисторе R3 за счет тока IКЭ0 можно пренебречь. Это напряжение соответствует логической ²1². (Первая строчка таблицы).

а) б)

Рисунок 1.6

При подаче на вход 1 логической ²1² диод VD 1 будет включен в обрат- ном направлении, ток от источника питания будет проходить через диод VD 2 и напряжение в точке А будет по прежнему равно 0,8 В. Как и в преды -дущем случае транзистор будет закрыт и напряжение на выходе будет соот- ветствовать логической ²1². (Вторая и аналогично третья строчки таблицы).

При подаче на оба входа логической ²1²диоды VD 1 и VD 2 будут включены в обратном направлении, через них будет протекать обратный ток. Основной ток в этом случае протекает через VD 3, VD 4 и эмиттерный пере- ход транзистора. На каждом из pn-переходов падает напряжение 0,7 В (UА=2,1 В). Резистор R1выбирается таким образом, чтобы транзистор находился в режиме насыщения и тогда напряжение на его коллекторе составит примерно равно 0,1 В, что соответствует логическому ²0² (четвертая строчка таблицы).

Сравнивая два первых и последний столбцы таблицы видим, что данная схема выполняет логическую операцию И-НЕ.

2015-04-01

2015-04-01 849

849