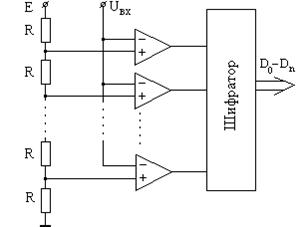

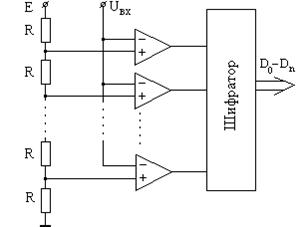

Алгоритм осуществляет из 2n-1 эталонов «подборку» нужного эталона, равного значению преобразуемого напряжения, за один такт (есть интегральные АЦП, реализующие данный алгоритм с задержкой преобразования не более 50 – 100 нсек)Структурная схема (в ее составе 2n–1 схема сравнения)

|

Электрическая цепь из последовательно соединенных 2nвысокоточных одинаковых по номинальному сопротивлению резисторов задает сетку из 2n-1 эталонов. Величина минимального эталона равна значению единицы младшего разряда преобразователя (снимается с резистора, подключенного к земле). Если присвоить минимальному эталону первый номер, то второй эталон будет в два раза больше, третий в три раза и т.д.. Напряжения данных эталонов подаются на входы быстродействующих схем сравнения (компараторов), другие входы которых объединены между собой и подключены к источнику преобразуемого напряжения - U  . Двоичные сигналы с выходов компараторов, равные нулю, если U

. Двоичные сигналы с выходов компараторов, равные нулю, если U  больше значения напряжения эталона, подключенного к рассматриваемому компаратору или единице в противном случае, образуют код из 2n-1нулей и единиц. Этот код по параллельному интерфейсу подается на кодирующую схему (шифратор), на выходе которой с небольшой задержкой получается двоичный код, соответствующий входному напряжению.

больше значения напряжения эталона, подключенного к рассматриваемому компаратору или единице в противном случае, образуют код из 2n-1нулей и единиц. Этот код по параллельному интерфейсу подается на кодирующую схему (шифратор), на выходе которой с небольшой задержкой получается двоичный код, соответствующий входному напряжению.

Работа ПНК считывающего типа описывается системой переключательных функций.

При N=8 – в выходной кодовой комбинации 3 разряда, чему соответствуют 3 функции yi. Не останавливаясь на минимизации функции yi отметим, что при минимизации учитывают определенные свойства конъюнкции аргументов xi

,

В результате при n = 3

Пример функциональной схемы ПНК считающего типа.

. Двоичные сигналы с выходов компараторов, равные нулю, если U

. Двоичные сигналы с выходов компараторов, равные нулю, если U  больше значения напряжения эталона, подключенного к рассматриваемому компаратору или единице в противном случае, образуют код из 2n-1нулей и единиц. Этот код по параллельному интерфейсу подается на кодирующую схему (шифратор), на выходе которой с небольшой задержкой получается двоичный код, соответствующий входному напряжению.

больше значения напряжения эталона, подключенного к рассматриваемому компаратору или единице в противном случае, образуют код из 2n-1нулей и единиц. Этот код по параллельному интерфейсу подается на кодирующую схему (шифратор), на выходе которой с небольшой задержкой получается двоичный код, соответствующий входному напряжению.

2015-04-01

2015-04-01 626

626