Кратко рассмотрим все интерфейсы связи, поддерживаемые используемым микроконтроллером Cygnal C8051F005. Это интерфейсы UART, SPI и I2C.

Концепция шины I2C

Шина I2C поддерживает любую технологию изготовления микросхем (НМОП, КМОП, биполярную). Две линии, данных (SDA) и синхронизации (SCL) служат для переноса информации. Каждое устройство распознается по уникальному адресу - будь то микроконтроллер, ЖКИ буфер, память или интерфейс клавиатуры - и может работать как передатчик или приёмник, в зависимости от назначения устройства. Обычно ЖКИ буфер - только приёмник, а память может как принимать, так и передавать данные. Кроме того, устройства могут быть классифицированы как ведущие и ведомые при передаче данных (см. Таблицу 5). Ведущий - это устройство, которое инициирует передачу данных и вырабатывает сигналы синхронизации. При этом любое адресуемое устройство считается ведомым по отношению к ведущему.

Таблица 5.

| Термин (англ) | Термин (рус) | Описание |

| Transmitter | Передатчик | Устройство, посылающее данные в шину |

| Receiver | Приемник | Устройство, принимающее с шины |

| Master | Ведущий | Начинает пересылку данных, вырабатывает синхроимпульсы, заканчивает пересылку данных |

| Slave | Ведомый | Устройство, адресуемое ведущим |

| Multi-master | - | Несколько ведущих могут пытаться захватить шину одновременно, без нарушения передаваемой информации |

| Arbitration | Арбитраж | Процедура, обеспечивающая Multi-master |

| Synchronization | Синхр. | Процедура синхронизации двух устройств |

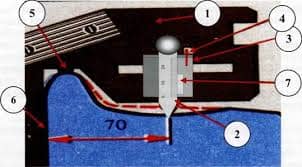

1. Микроконтроллер А

2. Массив

3. ЖКИ драйвер

4. АЦП

5. Статическая ОЗУ или ППЗУ

6. Микроконтроллер B

Шина I2C допускает несколько ведущих. Это означает, что более чем одно устройство, способное управлять шиной, может быть подключено к ней. Поскольку в качестве ведущих обычно выступают микроконтроллеры, давайте рассмотрим пример пересылки данных между двумя микроконтроллерами, подключенными к шине (рис 3). Пример покажет взаимоотношения передатчик-приемник и ведущий-ведомый, существующие в шине I2C. Необходимо заметить, что эти отношения не постоянны, а зависят только от направления пересылки данных в данный момент времени. Пересылка данных будет происходить следующим образом:

1. Пусть микроконтроллер А желает послать информацию в микроконтроллер В:

· микроконтроллер А (ведущий) адресует микроконтроллер В (ведомый)

· микроконтроллер А (ведущий-передатчик) посылает данные микроконтроллеру В (ведомый-приёмник)

· микроконтроллер А заканчивает пересылку

2. Пусть микроконтроллер А желает принять информацию от микроконтроллера В:

· микроконтроллер А (ведущий) адресует микроконтроллер В (ведомый)

· микроконтроллер А (ведущий-приемник) принимает данные от микроконтроллера В (ведомый-передатчик)

· микроконтроллер А заканчивает пересылку

В обоих случаях ведущий (микроконтроллер А) генерирует синхроимпульсы и заканчивает пересылку.

Возможность подключения более одного микроконтроллера к шине означает, что более чем один ведущий может попытаться начать пересылку в один и тот же момент времени. Для устранения хаоса, который может возникнуть в данном случае, разработана процедура арбитража. Эта процедура основана на том, что все I2C-устройства подключаются к шине по правилу монтажного И.

Генерация синхросигнала - это всегда обязанность ведущего; каждый ведущий генерирует свой собственный сигнал синхронизации при пересылке данных по шине. Сигнал синхронизации может быть изменен только если он “вытягивается” медленным ведомым устройством (путем удержания линии в низком состоянии), или другим ведущим, если происходит столкновение.

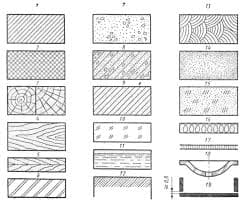

Как SDA, так и SCL являются двунаправленными линиями, подсоединенными к положительному источнику питания через подтягивающий резистор (см. Рис 4). Когда шина свободна, обе линии находятся в ВЫСОКОМ положении. Выходные каскады устройств, подключенных к шине, должны иметь открытый сток или открытый коллектор для обеспечения функции монтажного И. Данные по шине I2C могут передаваться со скоростю до 100 кбит/с в стандартном режиме, и до 400 кбит/с в “быстром” режиме. Количество устройств, подключенных к шине, определяется единственным параметром - емкостью линии (до 400 пф).

1. SDA (линия данных)

2. SCL (линия синхронизации)

3. Выход синхронизации

4. Вход синхронизации

5. Выход данных

6. Вход данных

7. Подтягивающие резисторы

8. Напряжение питания

Последовательный периферийный интерфейс - SPI - (Serial Peripheral Interface)

Последовательный периферийный интерфейс (SPI) обеспечивает высокоскоростной синхронный обмен данными между микроконтроллерами и периферийными устройствами или между несколькими микроконтроллерами.

Основные характеристики SPI интерфейса:

· Полнодуплексный 3-проводный синхронный обмен данными.

· Режим работы ведущий или ведомый.

· Обмен данными с передаваемыми первыми старшим или младшим битами.

· Четыре программируемые скорости обмена данными.

· Флаг прерывания по окончании передачи.

· Активация из Idle режима (только в режиме ведомого)

Соединения между ведущим и ведомым CPU, использующими SPI интерфейс, показаны на рис. 39. Вывод PB1(SCK) является выходом тактового сигнала ведущего микроконтроллера и входом тактового сигнала ведомого. По записи ведущим CPU данных в SPI регистр начинает работать тактовый генератор SPI и записанные данные сдвигаются через вывод выхода PB2(MOSI) ведущего микроконтроллера на вывод входа PB2 (MOSI) ведомого микроконтроллера. После сдвига одного байта тактовый генератор SPI останавливается, устанавливая флаг окончания передачи (SPIF). Если в регистре SPCR будет установлен бит разрешения прерывания SPI (SPIE), то произойдет запрос прерывания. Вход выбора ведомого PB0(SS), для выбора индивидуального SPI устройства в качестве ведомого, устанавливается на низкий уровень. При установке высокого уровня на выводе PB0(SS) порт SPI деактивируется и вывод PB2(MOSI) может быть использован в качестве вывода входа. Режим ведущий/ведомый может быть установлен и программным способом установкой или очисткой бита MSTR в регистре управления SPI.

Два сдвиговых регистра ведущего и ведомого микроконтроллеров можно рассматривать как один разнесенный 16-разрядный циклический сдвиговый регистр. См. Рис 39. При сдвиге данных из ведущего микроконтроллера в ведомый одновременно происходит сдвиг данных из ведомого микроконтроллера в ведущий, т.е. в течение одного цикла сдвига происходит обмен данными между ведущим и ведомым микроконтроллерами.

В системе организовано одиночное буферирование передающей стороны и двойное буферирование на приемной стороне. Это означает то, что передаваемые символы не могут быть записаны в регистр данных SPI прежде, чем будет полностью завершен цикл сдвига.

С другой стороны, при приеме данных принимаемый символ должен быть считан из регистра данных SPI прежде, чем будет завершен прием следующего символа, в противном случае предшествовавший символ будет потерян.

При разрешенном SPI направления данных выводов MOSI, MISO, SCK и SS настраиваются в соответствии со следующей таблицей:

Таблица 6. Настройка выводов SPI

| Вывод | Направление, ведущий SPI | <Направление, ведомый SPI/b> |

| MOSI | Определяется пользователем | Вход |

| MISO | Вход | Определяется пользователем |

| SCK | Определяется пользователем | Вход |

| S S | Определяется пользователем | Вход |

Из всех интерфейсов, поддерживаемых микроконтроллером, для связи с компьютером целесообразно использовать интерфейс UART. Этот интерфейс является наиболее простым для реализации в программном обеспечении и требует всего две односторонних линии передачи данных, что упрощает реализацию гальванической развязки интерфейса.

2015-04-30

2015-04-30 1092

1092