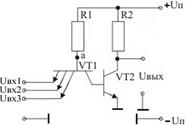

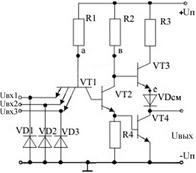

В интегральной схемотехнике логические элементы выполняются на транзисторах, что значительно упрощает технологию изготовления. Чаще всего в качестве входного элемента используется многоэмиттерный транзистор. Схема базового элемента транзисторно-транзисторной логики (ТТЛ) приведена на рисунке 4.7а.

а б

а – базовый элемент ТТЛ; б – экономичный элемент ТТЛ.

Рисунок 4.7 – Элемент ТТ-логики

В ТТЛ-элементах многоэмиттерный транзистор VT1 реализует функцию "И", а транзистор VT2 - функцию "НЕ". Если на все входы подана "1", т. е высокий потенциал, то эмиттерные переходы транзистора VT1 заперты. Переход база-коллектор VT1 находится под прямым напряжением и открыт. По цепи Un+;R1; база VT1; коллектор VT1;база VT2;эмиттер VT2;Un - протекает ток Iбн, который держит в насыщенном состоянии VT2. Выходное напряжение при этом равно "0". При подаче низкого потенциала хотя бы на один из входов PN переход этого эмиттера открывается и через VT1 начинает протекать ток Iэ, который много больше Iбн. Iэ создает на R1 падение напряжения почти равное Un. Потенциал точки "а" приближается к потенциалу общей шины. В результате Uбэ VT2 стремится к нулю; Iб VT2 прекращается и VT2 переходит в режим отсечки. Напряжение на выходе VT2 стремится к Un, т. е. на выходе VT2 появляется "1". Однако, схема рисунка 4.7а не экономична. Для повышения экономичности используют сложный инвертор (рисунок 4.7б). Каскад на транзисторе VT2 является предварительным и управляет работой транзисторов VT3, VT4. При "1" на всех входах VT2 насыщен и протекает ток Iк2н в несколько раз меньше, чем в схеме рисунок 4.7а. Ток эмиттера VT2 создает на R4 падение напряжения достаточное, чтобы VT4 был насыщен, следовательно, на выходе схемы устанавливается напряжение близкое к нулю, т. е. на выходе "0". При этом VT3 заперт, потому что потенциал точки "C" выше или равен потенциалу точки "B". Такое состояние схемы осуществляется за счет включения диода VD см; падение напряжения на диоде равно приблизительно 0.5В. Отсутствие собственного потребления тока в выходной цепи (за счет закрытого VT3) сложного инвертора делает его экономичным при "0" на выходе.

При наличии "0" хотя бы на одном из входов VT2 закрыт. Падение напряжения на R4 равно нулю; транзистор VT4 закрыт. Транзистор VT3 открыт возросшим до Un потенциалом точки "B". Ток через VT3, если не присоединена нагрузка, практически не протекает так как VT4 закрыт. Это обеспечивает экономичность схемы в режиме холостого хода при "1" на выходе. Ток при подключении нагрузки определяется соотношением:

Диоды VD1 и VD2 включены для защиты входных цепей и повышения помехоустойчивости. При положительных входных сигналах они заперты и не влияют на работу схемы. Открываются они при отрицательной полярности входных напряжений, что наблюдается при переходных процессах, когда при переключении схемы возникают затухающие колебания из-за наличия паразитных емкостей и индуктивностей. При первой отрицательной полуволне напряжения диод открывается, и напряжение на входе не превышает падения напряжения на диоде. Мощность паразитного колебания гасится и следующая положительная полуволна колебания уже меньше уровня логической единицы, поэтому ложного срабатывания логического элемента не происходит.

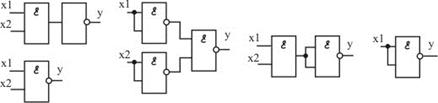

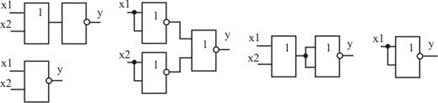

ТТЛ - элементы нашли широкое применение в практике. Промышленностью освоен ряд серий микросхем с ТТЛ, например К133, К134, К155 и другие. В качестве базового элемента серии микросхем могут использоваться элементы "ИЛИ-НЕ". На рисунке 4.8 и 4.9 приведены примеры реализации основного логического базиса с помощью таких элементов.

Рисунок 4.8 - Реализация основного логического базиса

с помощью элемента «2И-НЕ»

Рисунок 4.9 - Реализация основного логического базиса с

помощью элемента «2ИЛИ-НЕ»

2015-04-30

2015-04-30 682

682