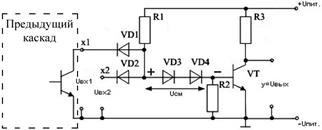

Элементы диодно-транзисторной логики (ДТЛ) получают объединением диодно-резисторных схем с усилителем на биполярном транзисторе, собранном по схеме с общим эмиттером, выполняющим операцию логического отрицания. Схема базового элемента ДТЛ приведена на рисунке 4.6.

При подаче на оба входа "1" т.е. высокого напряжения, диоды VD1 и VD2 заперты и от + Uпит через R1, диоды смещения VD3,VD4 и R2 протекает ток. Падение напряжения на R2 достаточно для того, что бы транзистор VT1 был открыт и насыщен. При открытом транзисторе напряжение на его коллекторе будет близко к нулю, т.е. Y=Uвых=OB ="0".

Рисунок 4.6 – Элемент ДТ-логики

Если хотя бы один из входных сигналов равен "0", то через соответствующий входной диод резистор R1 замыкается на корпус, потенциал на базе транзистора понижается и он переходит в состояние отсечки. На выход через R3 поступает напряжение, равное Uпит, соответствующее "1". Таким образом, базовый элемент реализует логическую функцию 2И-НЕ. ДTЛ используются при реализации микросхем, обладающих повышенной помехоустойчивостью, так как имеется возможность повышения порогового напряжения, например серия К511.

Падение напряжения на открытых диодах смещения VD3, VD4 должно быть таким, чтобы при открытом любом из входных диодов потенциал базы был достаточно низок для надежного запирания транзистора. Это условие выполняется при Uсм большем, чем сумма падений напряжений на входном диоде (VD1 или VD2) и открытом транзисторе предыдущего каскада.

2015-04-30

2015-04-30 1109

1109