Для большинства систем работающих от блоков микропроцессорного управления, необходимо учитывать последовательности срабатывания механизмов и устройств, а также соотв. Технологических параметров, которые контролируются посредством сигналов поступающих с датчиков. Если параметр соотв. Заданным значениям, значит его состояние истинное, что соответствует лог. 1.

В зависимости от кол- ва контролируемых пар- ров составляются логические выражения и таблицы истинности, которые имеют возможность управлять системой в целом. Эти выражения необходимо по возможности упрощать, что отражается на минимизации устройств которые её реализуют. Минимизация осуществляется используя алгебру логики и карт Карно:

a+b=b+a; a∙b=b∙a;-переменный з-н

a(b+c)=ab+ac; - сочетательный з-н

=

=  +

+  ;

;  =

=  ; теорема де Моргана

; теорема де Моргана

Основные соотношения

a∙1=1; a∙0=0; a+1=1; a+0=a;  =a; a+a=a; a+

=a; a+a=a; a+  b=a+b;

b=a+b;  +ab=

+ab=  +b;

+b;

Минимизация при помощи карт Карно

Карты Карно классифицируются в зависимости от кол-ва входных переменных: 2, 3, 4 и более.

| a | |

| ||

c c

| ||

| bc | ||

b

|

|  b b

| ab | a

| |

| ||||

d d

| ||||

| cd | ||||

c

|

Схематическоеизображение карт Карно с 3-4 переменными:

| X1 | X2 | X3 | X4 | y |

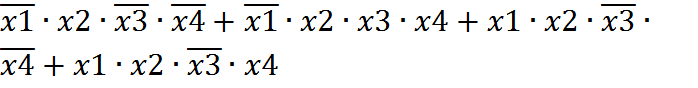

1. составляется таблица истинности в зависимости от сигналов с датчиков устройств, и записывается выражение.

y=

Полученное выражение минимизируется с помощью карт Карно. На карте Карно проставляются единицы соотв. Выражениями связанные логические или.

x1→a; x2→b; x3→c; x4→d;

В зависимости от предьявл. условий, определённые сочетания входов соотв. логическим единицам.

2. по таблице истинности составляем логическое выражение в дизъюнктивной нормальной форме (ДНФ). рядом расположеные единицы объединяем в контуры по 2,4 или 8 штук. Контуры соед. вдоль расположен. строк и столбцов:

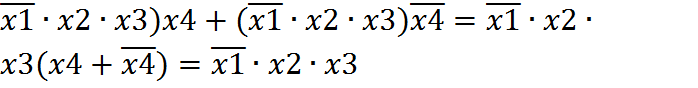

(

Единицы котор. не объединились в контуры представляющие собой выражения, сохранившиеся в исходном состоянии. Единицы проставляемые на карте Карно объединяются в контуры, при сворачивании карты в цилиндр относительно горизонтальной или вертикальной оси.

По лог. выражению ДНФ составляется схема из эл-тов входящих в состав интегральных микросхем, реализующих лог. функции инверсии и,или.

20)Дешифраторы

Дешифратор- логическое устройство, выполняющее преобразование двоичный n-разрядный код в унитарный 2 n код. Осуществляет обратный перевод двоичных чисел. Бывают полные (n-входов, 2 n –выходов) и неполные(выходов меньше).Для расширения числа входов и выходов используют каскадное включение.

2015-05-13

2015-05-13 427

427