- аналоговый компаратор (выполнен на базе операционного усилителя (ОУ))

- аналоговый компаратор (выполнен на базе операционного усилителя (ОУ))

R – резистор

С – поляризованный конденсатор

- IGFET - полевой транзистор с изолированным затвором

- IGFET - полевой транзистор с изолированным затвором

Counter – счетчик (увеличивает свое значение в соответствии с тактовыми импульсами)

Shift Register – сдвиговый регистр - используется для формирования выходного значения АЦП

В данном АЦП, в отличие от АЦП последовательного приближения, ступенчатого преобразования и следящего АЦП не используется DAC. Это достигается за счет его замены на analog ramping circuit и цифровой счетчик (digital counter) с точным таймингом.

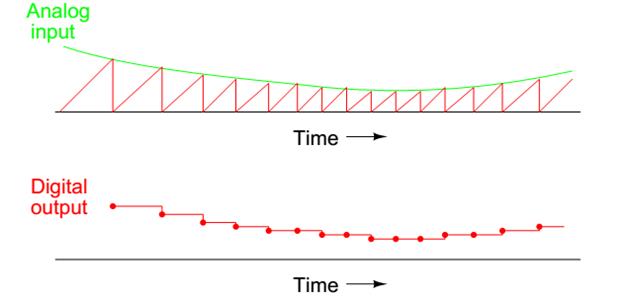

В этом и заключается основная идея интегрирующего АЦП (integrating ADC). Вместо того чтобы использовать DAC с пилообразным сигналом на выходе, мы можем воспользоваться цепь, основанную на операционном усилителе (op-amp circuit), называемую интегратором (integrator), для генерации пилообразного сигнала, который впоследствии будет сравниваться с входным аналоговым сигналом при помощи компаратора. Время, которое необходимо пилообразному сигналу для того, чтобы превысить значение входного сигнала, измеряется цифровым счетчиком, тактируемым при помощи прямоугольного сигнала (погрешность частоты счетчика не должна превышать эталонно допустимой величины).

Схема, состоящая из полевого транзистора с изолированным затвором и конденсатора (см рисунок выше), является упрощенной. В действительности, схема-защелка (latching circuit), будет с большой вероятностью подключаться к затвору транзистора для того, чтобы определить, полностью ли разряжен конденсатор, когда выходное значение компаратора будет иметь высокий уровень.

Основная идея заключается в следующем. Когда выходное значение компаратора имеет низкий уровень ( выше чем

выше чем  интегратора), интегратор начинает линейно заряжать конденсатор. Другими словами, счетчик инкрементируется с частотой тактируемого сигнала. Время, которое необходимо конденсатору для того чтобы зарядится до уровня входного напряжения

интегратора), интегратор начинает линейно заряжать конденсатор. Другими словами, счетчик инкрементируется с частотой тактируемого сигнала. Время, которое необходимо конденсатору для того чтобы зарядится до уровня входного напряжения  , зависит от уровня входного сигнала, а также параметров

, зависит от уровня входного сигнала, а также параметров  , R и C. Когда конденсатор достигает необходимого уровня входного напряжения, компаратор на выходе имеет высокий уровень сигнала, что в свою очередь загружает выход счетчика в сдвиговый регистр для получения конечного результата. IGFET срабатывает, когда на выходе компаратора высокий уровень, и разряжает конденсатор до 0 вольт. Когда значение интегратора падает до 0, компаратор вновь на выходе имеет низкий уровень напряжения, тем самым очищая значение счетчика и заставляя интегратор вновь наращивать напряжение.

, R и C. Когда конденсатор достигает необходимого уровня входного напряжения, компаратор на выходе имеет высокий уровень сигнала, что в свою очередь загружает выход счетчика в сдвиговый регистр для получения конечного результата. IGFET срабатывает, когда на выходе компаратора высокий уровень, и разряжает конденсатор до 0 вольт. Когда значение интегратора падает до 0, компаратор вновь на выходе имеет низкий уровень напряжения, тем самым очищая значение счетчика и заставляя интегратор вновь наращивать напряжение.

Интегрирующий АЦП ведет себя таким же образом как и АЦП ступенчатого преобразования, за исключением того что опорное напряжение имеет плавную пилообразную форму, а не ступенчатую.

Интегрирующий АЦП ведет себя таким же образом как и АЦП ступенчатого преобразования, за исключением того что опорное напряжение имеет плавную пилообразную форму, а не ступенчатую.

Данный АЦП страдает всеми недостатками АЦП ступенчатого преобразования + calibration drift (дрейф относительно показаний первоначально снятой градуировочной кривой). Точное соответствие выхода данного АЦП с его входом зависит от наклона напряжения интегратора вкупе с частотой тактируемого сигнала. В АЦП ступенчатого преобразования тактируемая частота не оказывала влияния на точность преобразования, только лишь на время обновления. В данном схеме, где частота интеграции и частота счетчика не зависят друг от друга, различия между этими параметрами неизбежны и приведут к потере точности. Единственный хороший момент, который наблюдается в этой схеме, заключается в том, что в нем не используется DAC, а это упрощает схему.

Панацеей от calibration drift является использование двухтактного интегрирующего АЦП. В таком АЦП интегрирующая схема увеличивает и уменьшает значение своего выходного напряжения в чередующихся циклах, вместо того чтобы сбрасываться в 0 в конце каждого цикла. Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1 постоянно; в качестве таймера используется счетчик с коэффициентом пересчета. После окончания стадии интегрирования ключ S1 размыкается, а ключ S2 замыкается и опорное напряжение Uоп поступает на вход интегратора. ри этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине. Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается.

Панацеей от calibration drift является использование двухтактного интегрирующего АЦП. В таком АЦП интегрирующая схема увеличивает и уменьшает значение своего выходного напряжения в чередующихся циклах, вместо того чтобы сбрасываться в 0 в конце каждого цикла. Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1 постоянно; в качестве таймера используется счетчик с коэффициентом пересчета. После окончания стадии интегрирования ключ S1 размыкается, а ключ S2 замыкается и опорное напряжение Uоп поступает на вход интегратора. ри этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине. Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается.

Отличительной особенностью метода многотактного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2 оставалась постоянной. Это можно обеспечить при использовании простого тактового генератора, поскольку существенные временные или температурные дрейфы частоты происходят за время несопоставимо большее, чем время преобразования.

2015-05-30

2015-05-30 2672

2672