Простейшим суммирующим элементом является четвертьсумматор. Происхождение этого термина станет ясным в ходе изложения. Наиболее известны для данной схемы названия: элемент “сумма по mod 2” и элемент “исключающее ИЛИ”.

|

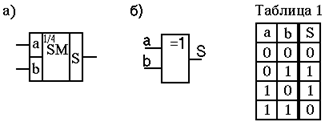

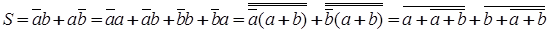

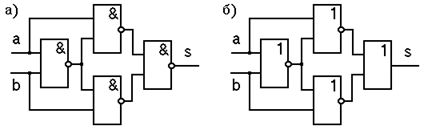

Рисунок 1.1 – Функциональное обозначение четвертьсумматора (а) и эквивалентного ему элемента “исключающее ИЛИ” (б).

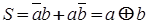

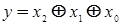

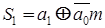

Схема (рисунок 1.1) имеет два входа a и b для двух слагаемых и один выход S для суммы. Работу её отражает таблица истинности 1, а соответствующее уравнение имеет вид:

. (1.1)

. (1.1)

Данный элемент выпускается в виде ИС типа ЛП5 (серии 133, 155, 530, 531, 533, 555, 1531, 1533); ЛП2 (561, 564); ЛП4 (1561) и т.п.

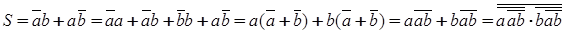

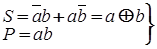

Реализуем четвертьсумматор в базисах И-НЕ и ИЛИ-НЕ, для чего преобразуем уравнение (1.1):

; (1.2)

; (1.2)

. (1.3)

. (1.3)

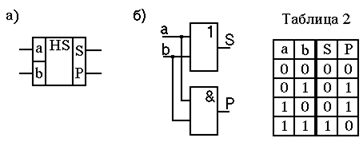

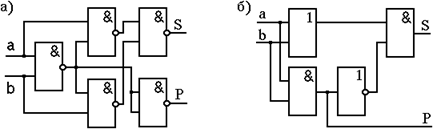

Схемы, реализованные по уравнениям (2) и (3), приведены на рисунке 1.2.

Рисунок 1.2 – Четвертьсумматор в базисах И-НЕ (а) и ИЛИ-НЕ (б).

|

Рисунок 1.3 –Функциональное обозначение полусумматора (а) и его реализация на элементах “исключающее ИЛИ” и «И» (б).

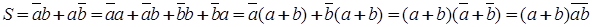

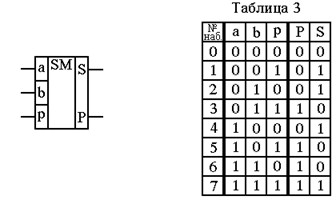

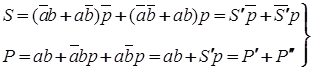

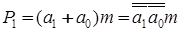

Полусумматор (Рисунок 1.3) имеет два входа a и b для двух слагаемых и два выхода: S – сумма, P – перенос. Обозначением полусумматора служат буквы HS (half sum – полусумма). Работу его отражает таблица истинности 2, а соответствующие уравнения имеют вид:

(1.4)

(1.4)

Из уравнений (1.4) следует, что для реализации полусумматора требуется один элемент “исключающее ИЛИ” и один двухвходовый вентиль И (Рисунок 1.3(б)). На рисунке 1.4(а) показана реализация полусумматора в базисе И-НЕ. Обратите внимание, что один из вентилей в схеме на рисунке 1.4 используется в качестве инвертора, а всего инверторов (операций инвертирования) пять. Реализуем полусумматор с использованием только одного инвертора, для чего уравнение для суммы запишем в следующем виде:

(1.5)

(1.5)

Схема полусумматора, построенного по уравнению (1.5), приведена на рисунок 4(б).

Рисунок 1.4. Полусумматор в базисе И-НЕ (а) и с одним инвертором (б).

|

Рисунок 1.5 – Функциональное обозначение полного двоичного одноразрядного сумматора.

Отметим два момента.

1) В табл. 1.2 и табл. 1.3 выходные сигналы P и S не случайно расположены именно в такой последовательности. Если значения P и S рассматривать как двухразрядное двоичное число, то очевидно, что  т.е. P=1, а S=0 или

т.е. P=1, а S=0 или  , т.е. P=1, S=1.

, т.е. P=1, S=1.

2) Выходные сигналы P и S полного двоичного сумматора относятся к классу самодвойственных функций алгебры логики. Самодвойственными называются такие функции, значение которых инвертируется при инвертировании всех переменных, от которых зависит функция. Обратите внимание, что S и P для четвертьсумматора и полусумматора не являются самодвойственными функциями! Преимущества, вытекающие из этого свойства полного двоичного сумматора, будут рассмотрены при анализе возможностей ИС типа ИМ1(133, 155).

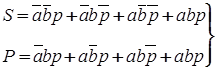

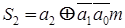

Уравнения, описывающие работу полного двоичного сумматора, представленные в совершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

(1.6)

(1.6)

Уравнение для переноса может быть минимизировано:

(1.7)

(1.7)

При практическом проектировании сумматора уравнения (1.6) и (1.7) могут быть преобразованы к виду, удобному для реализации на заданных логических элементах с некоторыми ограничениями (по числу логических входов и др.) и удовлетворяющему предъявляемым к сумматору требованиям по быстродействию.

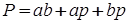

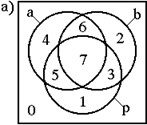

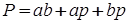

Например, преобразуем уравнения (1.6) следующим образом:

(1.8)

(1.8)

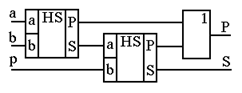

Из выражений (1.8) следует, что полный двоичный сумматор может быть реализован на двух полусумматорах и одном двухвходовом элементе ИЛИ. Соответствующая схема приведена на рис. 1.6. Из выражения (1.8) для S также следует:

(1.9)

(1.9)

Так как операция Å в выражении (1.9) коммутативна (переменные можно менять местами), то следует, что три входа полного двоичного сумматора абсолютно равноправны и на любой из них можно подавать любую входную переменную. Это полезно помнить, разводя печатные платы, на которых установлены ИС сумматоров.

Так как операция Å в выражении (1.9) коммутативна (переменные можно менять местами), то следует, что три входа полного двоичного сумматора абсолютно равноправны и на любой из них можно подавать любую входную переменную. Это полезно помнить, разводя печатные платы, на которых установлены ИС сумматоров.

Рисунок 1.6 – Полный двоичный сумматор, реализованный на двух полусумматорах.

Покажем, используя два метода, как была получена рациональная схема полного двоичного сумматора специалистами фирмы IBM, явившаяся основой схем сумматоров типа 7480, ИМ1(133, 155) и др.

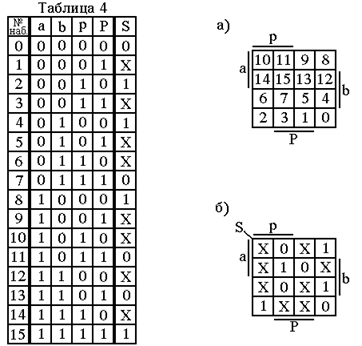

Первый метод основан на использовании значения выходного переноса P как вспомогательной переменной при определении выходной суммы S (табл. 1.4). В табл. 1.4 при наборах переменных, являющихся нереальными (например, единичное значение переноса при нулевых значениях всех переменных), поставлены безразличные значения X для функции S, которые можно доопределять произвольным образом.

|

Рисунок 1.7 – Карты Карно: а) – эталонная; б) – для S.

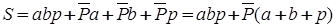

Из карты Карно для функции S (рисунок 1.7(б)) следует:

(10)

(10)

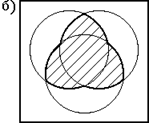

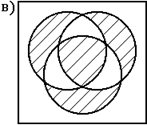

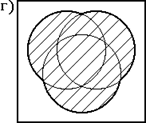

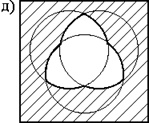

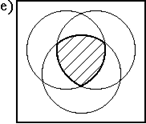

Второй метод основан на применении диаграмм Венна для реализации функций S и P сумматора при использовании только одного инвертора.

Рисунок 1.8. – Диаграммы Венна: для трёх переменных (а); для функций  (б); S (в);

(б); S (в);  (г);

(г);  (д); abp (е).

(д); abp (е).

На рис.8(а) показана диаграмма Венна для трёх переменных a, b, p; области, ограниченные окружностями, соответствуют переменным a, b и p, а области, обозначенные цифрами от 0 до 7 – соответствующим конъюнкциям (например,  ). Область, заштрихованная на рис.8(б), очевидно, соответствует функции

). Область, заштрихованная на рис.8(б), очевидно, соответствует функции  . Функция S представлена заштрихованной областью на рис.8(в). Её можно представить суммой произведения функции

. Функция S представлена заштрихованной областью на рис.8(в). Её можно представить суммой произведения функции  (рис.8(г)) на функцию

(рис.8(г)) на функцию  (рис.8(д)) и функции abp (рис.8(е)). Очевидно, что в этом случае получается выражение для S, аналогичное уравнению (10).

(рис.8(д)) и функции abp (рис.8(е)). Очевидно, что в этом случае получается выражение для S, аналогичное уравнению (10).

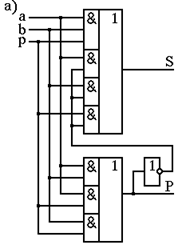

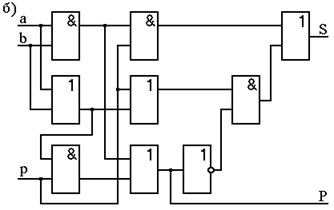

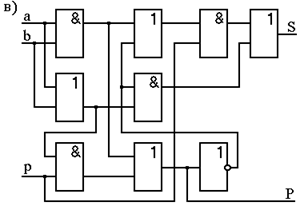

Схема сумматора, реализованного по уравнениям (7) и (10), приведена на рис.9(а). В данной схеме используется многовходовые логические элементы И и ИЛИ. Если использовать только двухвходовые элементы, то получаются схемы рис.9(б) и (в), причём вариант (б) разработан в США, а (в) – в СССР.

Рисунок 1.9. – Рациональные схемы полного двоичного сумматора: (а) – на многовходовых элементах; (б), (в) – на двухвходовых элементах.

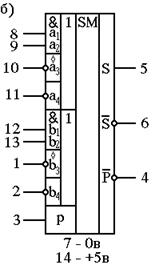

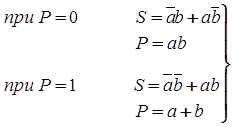

Логическая структура полного двоичного сумматора типа ИМ1(133, 155) приведена на рис. 1.10(а), а его функциональное обозначение – на рис. 1.10(б).

Рисунок 1.10. – Полный двоичный одноразрядный сумматор типа ИМ1(133, 155): (а) – логическая структура; (б) – функциональное обозначение.

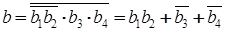

Рассмотрим возможности этой схемы, обеспечиваемые логикой на входах a и b. Сигнал на выходе вентиля D1, выполненного по схеме с открытым коллектором, равен  . Элемент D2 – это псевдоэлемент, реализующий операцию И над сигналом y1 и входом a3 (a3 – вывод открытого коллектора). Сигнал на выходе элемента D2 равен:

. Элемент D2 – это псевдоэлемент, реализующий операцию И над сигналом y1 и входом a3 (a3 – вывод открытого коллектора). Сигнал на выходе элемента D2 равен:  ,а сигнал на выходе элемента D3 будет:

,а сигнал на выходе элемента D3 будет:

(1.11)

(1.11)

Аналогично для входа b имеем:

(1.12)

(1.12)

При использовании данной схемы между входами  ,

,  и источниками питания +5В нужно включить резисторы с сопротивлением 1÷2 кОм.

и источниками питания +5В нужно включить резисторы с сопротивлением 1÷2 кОм.

Наличие входов  ,

,  и

и  ,

,  позволяет маскировать либо число

позволяет маскировать либо число  , либо число

, либо число  . Наличие входа

. Наличие входа  позволяет подключить любую дополнительную логику к схеме сумматора, а наличие входа

позволяет подключить любую дополнительную логику к схеме сумматора, а наличие входа  даёт возможность преобразовать многоразрядные числа A и B в обратный или дополнительный код, благодаря чему сумматор можно использовать в качестве вычитателя.

даёт возможность преобразовать многоразрядные числа A и B в обратный или дополнительный код, благодаря чему сумматор можно использовать в качестве вычитателя.

1.3 Одноразрядный сумматор как многофункциональный элемент

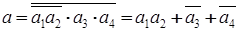

Кроме использования по прямому назначению, одноразрядный сумматор широко применяется в различных цифровых схемах в качестве многофункционального элемента. Так, в ряде серий ИС отсутствует мажоритарный элемент (схема голосования 2 из 3), так как в качестве такого элемента можно использовать выход P одноразрядного сумматора. Если один из входов одноразрядного сумматора (например, p) использовать в качестве управляющего, то из уравнений (1.6) и (1.7) следует:

(1.13)

(1.13)

т.е. одноразрядный сумматор можно использовать для реализации логических операций “сумма по mod 2”, равнозначность, И, ИЛИ.

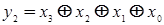

Наиболее широко в качестве многофункционального элемента используется схема “сумма по mod 2”. Приведём лишь несколько примеров:

1) преобразование двоичного кода в рефлексный (отраженный, Грея) код;

2) преобразование рефлексного кода в двоичный код;

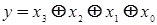

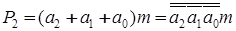

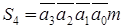

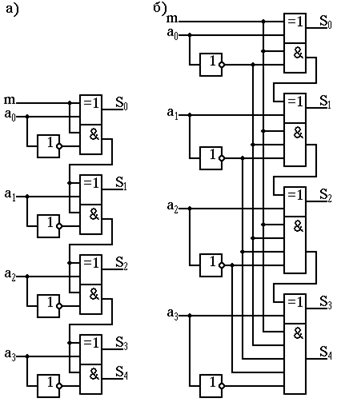

3) сложение по mod2 многих одноразрядных чисел, например, в схемах контроля на четность/нечетность (рис. 1.11 (а, б)), где  , а

, а  ;

;

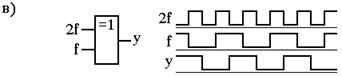

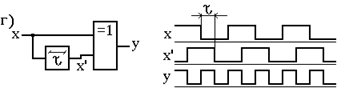

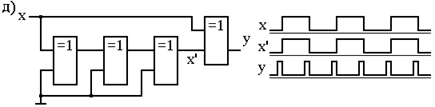

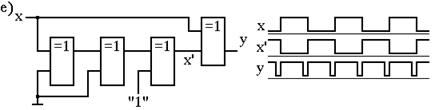

4) реализация сдвига фазы цифрового сигнала с частотой f, если доступен цифровой сигнал с частотой 2f (рис. 1.11(в));

5) реализация умножителя частоты на два (рис. 1.11(г));

6) формирование разностных преобразователей (детекторов фронтов) (рис.11(д)). На рис.11(д) три элемента “ сумма по mod 2” выполняют функцию повторителей-задержек, а на рис. 1.11(е) один из элементов выполняет функцию инвертора;

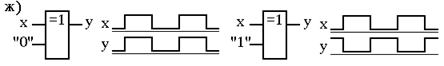

7) использование элемента “ сумма по mod 2” в качестве управляемого буфера: при “0” на одном из входов повторитель, при “1” на одном из входов инвертор (рис. 1.11(ж));

8) использование для обработки сигналов первичных датчиков в простейших устройствах ввода в ЭВМ типа “мышь”, “трэкболл”;

9) построение арифметических узлов типа “инкрементор”, “декрементор”;

10) преобразование прямого кода в обратный или дополнительный и т.д.

Рисунок 1.11. – Схема “сумма по mod 2” как многофункциональный элемент:

(а) – реализация  ; (б)– реализация

; (б)– реализация  ; (в) – сдвиг сигнала по фазе; (г) – умножитель частоты на два; (д) и (е) – разностные преобразователи; (ж) – управляемый буфер.

; (в) – сдвиг сигнала по фазе; (г) – умножитель частоты на два; (д) и (е) – разностные преобразователи; (ж) – управляемый буфер.

1.4 Инкрементор и декрементор

Инкрементором называется цифровой узел, выполняющий микрооперацию  , а декрементором -

, а декрементором -  .

.

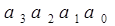

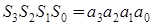

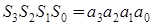

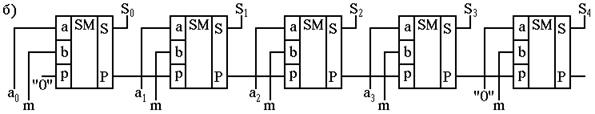

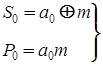

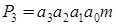

Разработаем четырёхразрядные схемы, которые выполняли бы две операции: при m=0  , а при m=1

, а при m=1  (для инкрементора) и

(для инкрементора) и  (для декрементора). Взяв за основу сумматор с последовательным переносом, получим структурную схему инкрементора (рис. 1..12(а)) и декрементора (рис. 1.12(б)). Для обеих схем при m = 0 получаем операцию суммирования числа

(для декрементора). Взяв за основу сумматор с последовательным переносом, получим структурную схему инкрементора (рис. 1..12(а)) и декрементора (рис. 1.12(б)). Для обеих схем при m = 0 получаем операцию суммирования числа  с числом 0000, т.е. повторение числа

с числом 0000, т.е. повторение числа  . Для схемы рис. 1.12(а) при m = 1 имеем

. Для схемы рис. 1.12(а) при m = 1 имеем  плюс 0001, а для схемы рис. 1.12(б)

плюс 0001, а для схемы рис. 1.12(б)  плюс 1111, где 1111 – дополнительный код числа –1.

плюс 1111, где 1111 – дополнительный код числа –1.

Рисунок 1.12 – Структурные схемы на базе сумматора: а – инкрементора; б – декрементора.

Так как схемы рис. 1.12 имеют константные сигналы на входах, их можно упростить. Для схемы рис.1.14 (а), используя выражения (1.7) – (1.9), получим:

; (1.14)

; (1.14)

; (1.15)

; (1.15)

(1.16)

(1.16)

или

; (1.17)

; (1.17)

; (1.18)

; (1.18)

(1.19)

(1.19)

или

; (1.20)

; (1.20)

; (1.21)

; (1.21)

(1.22)

(1.22)

или

. (1.23)

. (1.23)

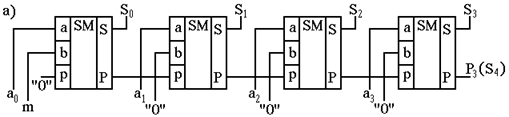

Уравнения (1.14) – (1.16), (1.18), (1.19), (1.22) и (1.23) отражают структуру инкрементора с последовательным и (в данном случае) сквозным переносом (рис. 1.13(а)), а уравнения (1.14), (1.15), (1.17), (1.18), (1.20), (1.21) и (1.23) – с параллельным переносом (рис. 1.13(б)).

Рисунок 1.13. – Схемы инкременторов: а – с последовательным и сквозным переносом; б – с параллельным переносом.

Для схемы рис. 1.12 (б), используя выражения (1.7) и (1.9) и учитывая соотношение  , то получим:

, то получим:

; (1.24)

; (1.24)

; (1.25)

; (1.25)

; (1.26)

; (1.26)

; (1.27)

; (1.27)

; (1.28)

; (1.28)

; (1.29)

; (1.29)

; (1.30)

; (1.30)

; (1.31)

; (1.31)

. (1.32)

. (1.32)

На рис. 1.14 (а) и (б) показаны соответственно схемы декременторов с последовательным (сквозным) переносом и параллельным переносом, реализованные по выражениям (1.24) – (1.32).

Инкременторы и декременторы используются, например, при организации серий обращений к последовательным адресам памяти и для этого вводятся в состав схем микропроцессоров. Они выполняют функции счетчиков в совокупности с регистром хранения, выходы которого поданы на входы этих схем. Такие счетчики легко тестировать, поскольку в них нет традиционных для счетчиков цепочек последовательно включённых триггеров, замедляющих проверку.

Рисунок 1.14 – Схемы декременторов: а – с последовательным (сквозным) переносом;

б – с параллельным переносом.

Лабораторное задание

1. Ознакомиться с теоретической частью.

2. Изучить описание лабораторного стенда УМ-11 или УМ-11М.

3. Выполнить синтез схем сумматоров и структур на их основе на основании задания.

4. Получить допуск к работе на лабораторном стенде.

Задание

1. Построить и исследовать четвертьсумматор в базисе И-НЕ.

2. Построить и исследовать четвертьсумматор в базисе ИЛИ-НЕ.

3. Построить и исследовать полусумматор в базисе И-НЕ.

4. Построить и исследовать полусумматор в базисе ИЛИ-НЕ.

5. Построить и исследовать полный двоичный одноразрядный сумматор в базисе И-НЕ.

6. Построить и исследовать полный двоичный одноразрядный сумматор в базисе ИЛИ-НЕ.

7. Построить и исследовать инкрементор с последовательным переносом

8. Построить и исследовать инкрементор с параллельным переносом

9. Построить и исследовать декрементор с последовательным переносом

10. Построить и исследовать декрементор с параллельным переносом

11. Построить и исследовать 2-х разрядный инкрементор на базе сумматора

12. Построить и исследовать 2-х разрядный декрементор на базе сумматора

Примечание. Исследование заключается в подаче входных сигналов и определении реакции на эти сигналы в соответствии с таблицей истинности.

13. Построить и исследовать умножитель частоты на 2 на базе четвертьсумматора с использованием двухканального осциллографа.

Требования к отчёту

Индивидуальный отчёт по лабораторной работе должен содержать:

- теоретические сведения, необходимые для выполнения работы;

- схемы синтезированных структур;

- временные диаграммы или осциллограммы синтезированных схем.

Контрольные вопросы

1. Почему суммирование является основной элементарной операцией в цифровых устройствах?

2. Что такое четвертьсумматор, полусумматор и сумматор?

3. Приведите классификацию сумматоров по определяющим признакам.

4. Как может быть получена рациональная схема сумматора?

5. Что такое многоразрядный сумматор?

6. Напишите уравнения, описывающие структуру схемы ускоренного переноса.

7. Что такое инкрементор?

8. Получите структуру инкрементора, используя его таблицу истинности.

9. Что такое декрементор?

10. Получите структуру декрементора, используя его таблицу истинности.

11. Обоснуйте структуру компаратора, построенного на базе сумматора.

1. САМОФАЛОВ К.Г., КОРНЕЙЧУК В.И., ТАРАСЕНКО В.П. Электронные цифровые вычислительные машины: Учебник. – Киев: Высшая школа, 1976. – 480с.

2. СОЛОВЬЕВ Г.Н. Арифметические устройства ЭВМ. – М.: Энергия, 1978. – 176с.

3. РАБИНОВИЧ З.Л. Основы теории элементных структур ЭВМ. – 2-е изд., перераб. и доп. – М.: Радио и связь, 1982. – 280с.

4. ЛАНЦОВ А.Л., ЗВОРЫКИН Л.Н., ОСИПОВ И.Ф. Цифровые устройства на комплементарных МДП интегральных микросхемах. – М.: Радио и связь, 1983. – 272с.

5. Схемотехника ЭВМ: Учебник для студентов вузов спец. ЭВМ / Под ред. Г.Н.СОЛОВЬЁВА. – М.: Высшая школа, 1985. – 391с.

6. ЗЕЛЬДИН Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Энергоатомиздат, 1986. – 280с.

7. Применение интегральных микросхем в электронной вычислительной технике: Справочник / ДАНИЛОВ Р.В., ЕЛЬЦОВА С.А., ИВАНОВ Ю.А. и др.; Под ред. ФАИЗУЛАЕВА Б.Н., ТАРАБРИНА Б.В. – М.: Радио и связь, 1986. – 384с.

8. УГРЮМОВ Е.П. Проектирование элементов и узлов ЭВМ.: Учеб. Пособие для вузов. – М.: Высшая школа, 1987. – 320с.

9. Применение интегральных схем: Практическое руководство: В 2-х книгах. Кн. 2. Пер. с англ. / Под ред. А.УИЛЬЯМА. – М.: Мир, 1987. – 413с.

10. ПОТЁМКИН И.С. Функциональные узлы цифровой автоматики. – М.: Энергоатомиздат, 1988. – 320с.

11. ШИЛО Б.Л. Популярные цифровые микросхемы: Справочник. – М.: Радио и связь, 1987. (Массовая радиобиблиотека. Вып.1111); 2-е изд., испр. – Челябинск: Металлургия, 1989. – 352с.

12. ВЕНИАМИНОВ В.Н., ЛЕБЕДЕВ О.Н., МИРОШНИЧЕНКО А.И. Микросхемы и их применение: Справ. Пособие. 3-е изд., перераб. и доп. – М.: Радио и связь, 1989. (Массовая радиобиблиотека. Вып.1143).

13. ПУХАЛЬСКИЙ Г.И., НОВОСЕЛЬЦЕВА Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. – М.: Радио и связь, 1990. – 304с.

14. БУКРЕЕВ И.Н., ГОРЯЧЕВ В.И., МАНСУРОВ Б.М. Микроэлектронные схемы цифровых устройств: 3-е изд., перераб. и доп. – М.: Радио и связь, 1990. – 416с.

2015-06-24

2015-06-24 16995

16995