Дешифратором называют логическую схему, которая преобразует код числа, поступающего на его входы, в управляющий сигнал только на одном из его выходов. Другими словами, дешифратор представляет собой совокупность схем совпадений, формирующих управляющий (рабочий) сигнал на одном из выходов, в то время как на остальных выходах управляющий сигнал отсутствует.

Иногда дешифраторы называют также избирательными схемами. При дешифрации N-разрядного двоичного кода и реализации всех комбинаций этого кода число выходов дешифратора К. будет равно 2N. Число входов дешифратора пд зависит от вида подачи входного числа в однофазной или парафазной форме и определяется как пД = N – при однофазном входном коде; пД = 2N – при парафазном входном коде.

По способу организации преобразования входного кода дешифраторы подразделяют на прямоугольные (матричные), пирамидальные и ступенчатые (каскадные) — двухкаскадные и многокаскадные.

Схемы дешифраторов выполняют на диодах, феррит-транзисторных ячейках, ферритовых сердечниках. Наибольшее распространение получили диодные дешифраторы. В цифровых вычислительных машинах дешифраторы применяются в устройствах управления для расшифровки кода операций и выдачи управляющих сигналов для выполнения тех или иных операций. В запоминающих устройствах ЦВМ дешифраторы используют для выбора ячеек соответствующих адресов при записи и считывании чисел из ЗУ. Они находят широкое применение в многоканальных преобразователях код – напряжение для переключения входных каналов в определенной заданной последовательности и т. д.

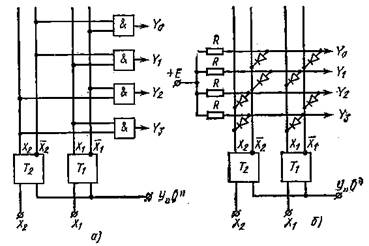

На рисунке 6 приведены схемы прямоугольного дешифратора на два входа и четыре выхода. Число, представленное в двоичном коде, записывается в двухразрядном регистре (триггеры Т1 и Т2).

С единичных выходов триггеров снимаются сигналы Х1, Х2, представляющие прямые значения переменных, а с нулевых выходов триггеров снимаются сигналы, представляющие собой инверсные значения.Таким образом, с регистра в схему дешифрации поступает парофазный код. Принципиальная схема прямоугольного дешифратора с логическими элементами совпадения на диодах на два входа показана на рисунке 6, б. Горизонтальные и вертикальные шины соединяются в определенных местах диодами, которые образуют сетку (матрицу) дешифратора. Резистор R и два диода, подключенные к горизонтальному проводу, образуют схему совпадения И. Таких схем в сетке четыре.

Рисунок 6 – Схема прямоугольного дешифратора на два входа: a — структурная; б — принципиальная на диодах.

Если Х1 = 0 и Х2 = 0 – это означает, что триггеры регистра находятся в положении, при котором высокий потенциал будет на нулевом выходе, триггеров. В этом случае диоды, связанные с верхней горизонтальной шиной дешифратора, закрыты и высокий потенциал источника +Е присутствует на шине Yo. Другие три горизонтальные шины связаны каждая хотя бы с одним диодом, находящимся в открытом состоянии. Поэтому на выходных шинах дешифратора Y1, Y2, Y3 в этом случае напряжение будет близко к нулю.

Если Х1 = 1, а Х2 = 0, то высокий уровень напряжения будет на выходе дешифратора У1. При Х1 = 0, Х2 = 1 высокий уровень напряжения будет на выходе У2, а при Х1 = 1, Х2 = 1 — на выходе Y3.

Принцип работы рассмотренного дешифратора можно представить в виде таблицы 1.

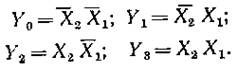

По данным этой таблицы можно записать выражения для переключательных функций:

Таблица 1.

| Х2 | Х1 | Y0 | Y1 | Y2 | Y3 |

Матрица прямоугольного дешифратора в общем случае составляется из 2п вертикальных шин. Прямоугольные дешифраторы целесообразно использовать для небольшого числа дешифрируемых величин, так как при большом количестве схем совпадения число диодов резко возрастает и тогда характеристики прямоугольного дешифратора ухудшаются.

В этом случае целесообразно применять ступенчатые дешифраторы.

Пирамидальный дешифратор состоит из нескольких ступеней дешифрируемых слов.

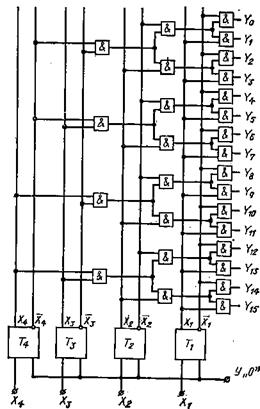

На рисунке 7 приведена структурная схема пирамидального дешифратора на четыре входа. Этот дешифратор реализует систему переключательных функций. Каждый из 16 сигналов Yi формируется в три ступени, первая ступень составлена из четырех схем совпадения, на вход которых поступают сигналы Х3, X4 и их инверсные значения. На выходе схем совпадения первой ступени возникают четыре сигнала, представляющие собой сочетание  .Вторая ступень составлена из восьми схем совпадения И. Эта ступень принимает сигналы

.Вторая ступень составлена из восьми схем совпадения И. Эта ступень принимает сигналы  от триггера Т2 и выходные сигналы от первой ступени схем совпадения. Третья ступень составлена из шестнадцати схем совпадения, каждая из которых рассчитана на два входа. Эта ступень принимает сигналы

от триггера Т2 и выходные сигналы от первой ступени схем совпадения. Третья ступень составлена из шестнадцати схем совпадения, каждая из которых рассчитана на два входа. Эта ступень принимает сигналы  от триггера Т1 и выходные сигналы схем совпадения И второй ступени. На выходе схем совпадения третьей ступени формируются выходные сигналы схемы дешифратора

от триггера Т1 и выходные сигналы схем совпадения И второй ступени. На выходе схем совпадения третьей ступени формируются выходные сигналы схемы дешифратора

Рисунок 7 – Схема пирамидального дешифратора на четыре входа.

Многоступенчатые дешифраторы. С точки зрения оборудования этот вид дешифраторов является наиболее экономичным. Принцип построения многоступенчатого дешифратора заключается в том, что дешифруемое слово разбивается на две группы. Затем каждая из этих двух групп разбивается также на две группы и так до тех пор, пока в каждой группе останется не более трех или двух переменных.

Структурная схема многоступенчатого дешифратора на десять входов приведена на рисунке 8. На схеме диодные матрицы изображены в виде квадратов с числом, показывающим количество выходных шин матрицы (на схеме для каждой матрицы показана только одна выходная шина).

Первую ступень дешифратора составляют четыре диодные матрицы с двумя или тремя входами и соответственно с четырьмя или восемью выходами.

Рисунок 8 – Схема многоступенчатого дешифратора, на десять входов.

Вторую ступень дешифратора составляют две матрицы, каждая из которых имеет 32 выхода.

Третья ступень дешифратора содержит одну матрицу на 1024 выхода.

При построении диодных дешифраторов основным фактором в выборе схемы является экономия диодов. Поэтому наибольшее распространение получили многоступенчатые дешифраторы.

2015-06-26

2015-06-26 7554

7554