В состав арифметического устройства (АУ) входит несколько узлов, основным из которых является сумматор. Сумматор предназначен для сложения или вычитания чисел. Схема его состоит из одноразрядных сумматоров.

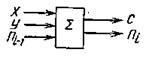

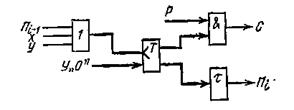

Одноразрядный сумматор. На рисунке 1 показано условное обозначение сумматора, где х, у – слагаемые; Пi-1 - единица переноса из предыдущего разряда; С – результат суммирования; Пi – единица при возможном переносе в следующий (старший) разряд. На вход одноразрядного сумматора подаются три одноразрядных числа. Два из них являются слагаемыми одинакового разряда, а третье – перенесенным из соседнего младшего разряда.

Сумматор имеет два выхода, по одному из которых выдается сумма этих трех чисел С, а по второму – число для переноса в старший разряд.

Принцип работы одноразрядного сумматора поясняется в таблице 1.

Рисунок 1 – Условное обозначение одноразрядного сумматора в функциональных схемах.

Таблица 1 принцип работы одноразрядного сумматора

| x | y | Пi-1 | C | Пi | x | y | Пi-1 | C | Пi |

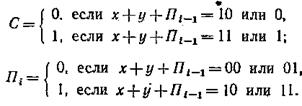

Таблицу можно изобразить следующим образом:

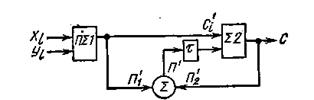

Одноразрядные сумматоры подразделяются на комбинационные и накапливающие.

В комбинационных сумматорах вначале производится сложение двух слагаемых, а затем результат суммы складывается с возможным числом переноса предыдущего разряда. Такой одноразрядный сумматор, формирующий сумму двух чисел, разбивается на два самостоятельных узла (блока), каждый из которых осуществляет сложение двух чисел. Такой узел или блок, производящий только часть операции суммирования, называют полусумматором.

Принцип работы полусумматора поясняется в таблице 2.

Таблица 2 принцип работы полусумматора.

| X | y | C' | П' | x | y | C' | П' |

Примечание. С' – частичная сумма; П' – частичный перенос.

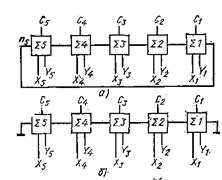

На рисунке 2, а и б представлены два варианта схем полусумматоров.

Рисунок 2 – Функциональные схемы комбинационных полусумматоров.

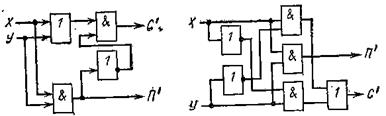

Как указывалось, комбинационный сумматор предназначен для сложения двух слагаемых и переноса из предыдущего разряда.

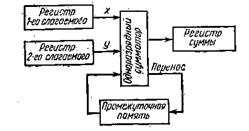

Структурная схема такого комбинационного сумматора приведена на рисунке 3; в нее входят две схемы полусумматоров и промежуточная память. Промежуточная память необходима для осуществления задержки передачи числа в следующий разряд до получения результата суммирования слагаемых.

Рисунок 3 – Функциональная схема комбинационного сумматора.

В накапливающем сумматоре основным элементом является счетчик, который осуществляет сложение—накапливание единиц одинаковых разрядов и перенос из предыдущего разряда.

В этих сумматорах операция сложения разделена во времени. Вначале поступает цифра первого слагаемого, а затем – второго и одновременно с этим образуется их сумма. Схема такого накапливающего сумматора приведена на рисунке 4.

Рисунок 4 – Схема накапливающего сумматора.

Ввод слагаемых х, у, а также возможного числа переноса из предыдущего разряда производится поочередно на соответствующий счетный вход триггера через схему ИЛИ.

На правом выходе триггера образуется код переноса, на левом – код суммы.

Если код переноса имеет единицу, то она через линию задержки τ поступает в триггер следующего разряда. Выходной вентиль В служит для разрешения выдачи результата суммы. Причем сумма выдается в том случае, когда выполнено сложение всех чисел с учетом переноса. Разрешение поступает по линии Р. Установка «0» служит для приведения схемы в исходное состояние.

Накапливающие сумматоры получили значительное распространение в схемах ЦВМ, так как они экономичнее и не нуждаются в жестких требованиях к синфазности и калибровке длительности входных импульсов. Однако для получения одинакового быстродействия схем триггеры накапливающих сумматоров должны обладать большей частотой срабатывания.

Многоразрядный сумматор состоит из нескольких одноразрядных сумматоров.

Многоразрядные сумматоры подразделяются на сумматоры с циклическим переносом и без циклического переноса (рисунке 5).

Сумматор с циклическим переносом позволяет производить перенос из старшего разряда в младший. В таких сумматорах числа складываются в обратном коде и результат вычисления также получается в обратном коде. Сумматор без циклического переноса производит сложение чисел в дополнительном коде и результат сложения также представляется в дополнительном коде.

Рисунок 5 – Структурные схемы многоразрядных сумматоров: а – с циклическим переходом; б – без циклического перехода.

Сумматоры бывают последовательного и параллельного действия.

Сумматор последовательного действия производит последовательное поразрядное сложение двух чисел с помощью одноразрядного сумматора. Структурная схема сумматора приведена на рисунке 6. В одноразрядный сумматор слагаемые поступают из двух регистров в последовательном коде, начиная с младшего разряда.

Рисунок 6 – Структурная схема сумматора последовательного действия.

Единица переноса при поразрядном суммировании, если только она появляется, заносится в промежуточную память, где хранится до прихода следующего разряда слагаемых. Такой процесс сложения продолжается до того момента, когда сложение будет произведено во всех разрядах обоих слагаемых.

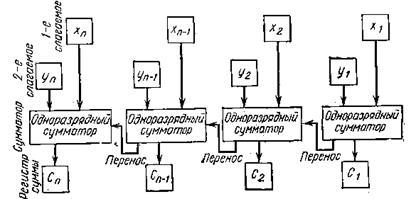

Сумматор параллельного действия производит параллельное поразрядное сложение двух чисел с помощью п одноразрядных сумматоров (n – число разрядов наибольшего слагаемого).

Структурная схема сумматора параллельного действия приведена на рисунке 7.

Сумматоры последовательного действия уступают сумматорам параллельного действия по быстродействию, но зато они более экономичны по оборудованию и применяются только в некоторых ЦВМ с небольшим быстродействием. Наиболее распространенными являются сумматоры параллельного действия накапливающего типа.

Рисунок 7 – Структурная схема сумматора параллельного действия.

2015-06-26

2015-06-26 6043

6043