АНАЛИЗ ПРОГРАММЫ ДЛЯ «УЧЕБНОГО» МИКРОКОНТРОЛЛЕРА (ЧАСТОТОМЕР)

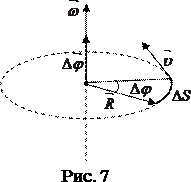

Частота – это количество колебаний в единицу времени. Допустим, необходимо определить частоту следования логических импульсов нулевого уровня, изображенных на рис.7.

Рис.7. Временная диаграмма следования логических импульсов

Если подсчитать количество логических импульсов, например, за 1с, то получится частота следования этих импульсов в Гц. Можно предложить следующий алгоритм реализации функции частотомера. На вход INT будем подавать логические импульсы неизвестной частоты fX, значение которой может изменяться в пределах от 0 до 255 Гц, а длительность импульсов постоянна τИ=500 мкс. С помощью подпрограммы обработки внешнего прерывания будем подсчитывать количество этих импульсов за 1 с. Выдержку времени τВ= 1с организуем с помощью таймера и прерываний от него в момент переполнения. При этом, время одного "тика" таймера для частоты кварцевого резонатора 6 МГц τ1ТИК=32*τМЦ=32*2,5=80 мкс. Количество "тиков" таймера при выдержке в 1с nТИК = τВ / τ1ТИК = 1000000 / 80 = 12500 "тиков". Количество переполнений таймера при этом nПЕР = nТИК / 256 = 12500 / 256 = 48 (212 - остаток). Т.е. выдержке времени в 1с соответствует 48 переполнений таймера плюс еще 212 "тиков" или 49 переполнений без 44 "тиков" (256-212=44). Запуск таймера осуществим с порога nПОРОГ = 44, а затем дождемся 49 переполнений таймера, что и будет соответствовать 1с. Количество переполнений таймера будем подсчитывать с помощью подпрограммы обработки прерываний от таймера. Запуск таймера будем осуществлять в момент прихода первого для данного измерительного цикла импульса неизвестной частоты, но подсчитывать этот импульс не будем, т.к. количество временных интервалов на один меньше чем импульсов их ограничивающих. Это будет синхронизированный по первому импульсу подсчет, причем погрешность подсчета импульсов находится в пределах от 0 до – 1. При несинхронизированном подсчете погрешность составляет ±1 импульс. На рис.8 приведена блок-схема алгоритма, реализующего описанный выше принцип измерения частоты, а пример программы по данной теме – см. лабораторную работу №9.

Рис.8. Блок-схема алгоритма, реализующего принцип измерения частоты

Подпрограмма задержки в 750 мкс необходима для гарантированного окончания очередного импульса, чтобы подсчитать его не более одного раза.

Задания к практическому занятию №8:

1) для программы частотомера определить время выполнения каждой из подпрограмм; 2) для программы частотомера рассчитать числовые значения при τИ=50 мкс, fX=0¸2550 Гц; τИ=5 мс, fX=0¸25,5 Гц.

ПРИЛОЖЕНИЕ 1

Система команд микроконтроллера типа КМ1816ВЕ48

| Мнемоника команды | Код команды двоичный В шестнадцатиричный Н | Краткий комментарий | Словесный комментарий | |

| Группа команд пересылки данных | ||||

| MOV A,Rn | 1111 1nnn B F 8÷F H | (A)←(Rn) | Записать в А содержимое регистра Rn (n=0÷7) | |

| MOV Rn,A | 1010 1nnn B A 8÷F H | (Rn)←(A) | Записать содержимое А в регистр Rn (n=0÷7) | |

| MOV A,#d | 0010 0011 B dB 2 3 H dH | (A)←d | Записать число d в А | |

| MOV Rn,#d | 1011 1nnn B dB B 8÷F H dH | (Rn)←d | Записать число d в регистр Rn (n=0÷7) | |

| MOV A,@Rn | 1111 000n B F 0÷1 H | (A)←((Rn)) | Записать в А содержимое ячейки, на которую указывает регистр Rn (n=0÷1) | |

| MOV @Rn,A | 1010 000n B A 0÷1 H | ((Rn))←(A) | Записать содержимое А в ячейку, на которую указывает регистр Rn (n=0÷1) | |

| MOV @Rn,#d | 1011 000n B dB B 0÷1 H dH | ((Rn))←d | Записать число d в ячейку, на которую указывает регистр Rn (n=0÷1) | |

| XCH A,Rn | 0010 1nnn B 2 8÷F H | (A)↔(Rn) | Обменять содержимое А и регистра Rn (n=0÷7) | |

| XCH A,@Rn | 0010 000n B 2 0÷1 H | (A)↔((Rn)) | Обменять содержимое А и ячейки, на которую указывает регистр Rn (n=0÷1) | |

| XCHD A,@Rn | 0011 000n B 3 0÷1 H | (A0-3)↔((Rn)0-3) | Обменять младшие тетрады А и ячейки, на которую указывает регистр Rn (n=0÷1) | |

| MOV A,T | 0100 0010 B 4 2 H | (A)←(T) | Записать содержимое таймера/счетчика в А | |

| MOV T,A | 0110 0010 B 6 2 H | (T)←(A) | Записать содержимое A в таймер/счетчик | |

| MOV A,PSW | 1100 0111 B C 7 H | (A)←(PSW) | Записать содержимое регистра ССП в А | |

| MOV PSW,A | 1011 0111 B D 7 H | (PSW)←(A) | Записать содержимое A в регистр ССП | |

| IN A,Pn | 0000 10nn B 0 9÷A H | (A)←(Pn) | Переслать данные из порта Pn в А (n=1÷2) (выполн. за 2м.ц.) | |

| INS A,BUS | 0000 1000 B 0 8 H | (A)←(BUS) | Стробируемый ввод данных из порта BUS в А (выполн. за 2м.ц.) | |

| OUTL Pn,A | 0011 10nn B 3 9÷A H | (Pn)←(A) | Переслать данные из A в порт Pn (n=1÷2) (выполн. за 2м.ц.) | |

| OUTL BUS,A | 0000 0010 B 0 2 H | (BUS)←(A) | Стробируемый вывод данных из А в порт BUS (выполн. за 2м.ц.) | |

| MOVX A,@Ri | 1000 000n B 8 0÷1 H | (A)←((Ri)) | Записать в А содержимое ячейки внешней памяти данных, на которую указывает регистр Ri (i=0÷1) (выполн. за 2м.ц.) | |

| MOVX @Ri,A | 1001 000n B 9 0÷1 H | ((Ri))←(A) | Записать содержимое А в ячейку внешней памяти данных, на которую указывает регистр Ri (n=0÷1) (выполн. за 2м.ц.) | |

| MOVD A,Pn | 0000 11nn B 0 C÷F H | (A0-3)←(Pn), (A4-7)←0000B | Ввод тетрады из порта Pn схемы расширителя в А (n=4÷7) (выполн. за 2м.ц.) | |

| MOVD Pn,A | 0011 11nn B 3 C÷F H | (Pn)←(A0-3) | Вывод тетрады из порта Pn схемы расширителя в А (n=4÷7) (выполн. за 2м.ц.) | |

| MOVP A,@A | 1010 0011 B A 3 H | (PC0-7)←(A), (A)←((PC)) | Записать в А содержимое ячейки ПЗУ, на которую указывает А (выполн. за 2м.ц.) | |

| MOVP3 A,@A | 1110 0011 B E 3 H | (PC0-7)←(A), (PC8-11)←0011В (A)←((PC)) | Записать в А содержимое ячейки, на которую указывает А, из 3-й страницы ПЗУ (выполн. за 2м.ц.) | |

| Группа команд арифметических операций | ||||

| ADD A,Rn | 0110 1nnn B 6 8÷F H | (A)←(A)+(Rn) | Прибавить к А содержимое регистра Rn (n=0÷7) | |

| ADD A,#d | 0000 0011 B dB 0 3 H dH | (A)←(A)+d | Прибавить к А число d | |

| ADD A,@Rn | 0110 000n B 6 0÷1 H | (A)←(A)+((Rn)) | Прибавить к А содержимое ячейки, на которую указывает регистр Rn (n=0÷1) | |

| ADDC A,Rn | 0111 1nnn B 7 8÷F H | (A)←(A)+(Rn)+(C) | Прибавить к А содержимое регистра Rn (n=0÷7) и признака переполнения С | |

| ADDС A,#d | 0001 0011 B dB 1 3 H dH | (A)←(A)+d+(С) | Прибавить к А число d и содержимое признака переполнения С | |

| ADDС A,@Rn | 0111 000n B 7 0÷1 H | (A)←(A)+((Rn))+ (С) | Прибавить к А содержимое ячейки, на которую указывает регистр Rn (n=0÷1), и признака переполнения С | |

| INC A | 0001 0111 B 1 7 H | (A)←(A)+1 | Увеличить на 1 содержимое А, не влияет на признак С | |

| INC Rn | 0001 1nnn B 1 8÷F H | (Rn)←(Rn)+1 | Увеличить на 1 содержимое регистра Rn (n=0÷7) | |

| INC @Rn | 0001 000n B 1 0÷1 H | ((Rn))←((Rn))+1 | Увеличить на 1 содержимое ячейки, на которую указывает регистр Rn (n=0÷1) | |

| DEC A | 0000 0111 B 0 7 H | (A)←(A)-1 | Уменьшить на 1 содержимое А, не влияет на признак С

| |

| DEC Rn | 1100 1nnn B C 8÷F H | ((Rn))←((Rn))-1 | Уменьшить на 1 содержимое регистра Rn (n=0÷7) | |

| DA A | 0101 0111 B 5 7 H | (A)BD← (A)B | Десятичная коррекция А | |

| Группа команд логических операций | ||||

| ANL A,Rn | 0101 1nnn B 5 8÷F H | (A)←(A)and(Rn) | Логическое умножение (И) А с маской в регистре Rn (n=0÷7) | |

| ANL A,#d | 0101 0011 B dB 5 3 H dH | (A)←(A) and d | Логическое умножение (И) А с непосредственным операндом-маской | |

| ANL A,@Rn | 0101 000n B 5 0÷1 H | (A)←(A)and((Rn)) | Логическое умножение (И) А с маской в ячейке, на которую указывает регистр Rn (n=0÷1) | |

| ORL A,Rn | 0100 1nnn B 4 8÷F H | (A)←(A)or(Rn) | Логическое сложение (ИЛИ) А с маской в регистре Rn (n=0÷7) | |

| ORL A,#d | 0100 0011 B dB 4 3 H dH | (A)←(A) or d | Логическое сложение (ИЛИ) А с непосредственным операндом-маской | |

| ORL A,@Rn | 0100 000n B 4 0÷1 H | (A)←(A) or ((Rn)) | Логическое сложение (ИЛИ) А с маской в ячейке, на которую указывает регистр Rn (n=0÷1) | |

| XRL A,Rn | 1101 1nnn B D 8÷F H | (A)←(A)xor(Rn) | Логическое исключающее ИЛИ А с маской в регистре Rn (n=0÷7) | |

| XRL A,#d | 1101 0011 B dB D 3 H dH | (A)←(A) xor d | Логическое исключающее ИЛИ А с непосредственным операндом-маской | |

| XRL A,@Rn | 1101 000n B D 0÷1 H | (A)←(A)xor((Rn)) | Логическое исключающее ИЛИ А с маской в ячейке, на которую указывает регистр Rn (n=0÷1) | |

| CLR A | 0010 0111 B 2 7 H | (A)←0 | Очистка А | |

| CPL A | 0011 0111 B 3 7 H | (A)←not(A) | Инверсия А | |

| SWAP A | 0100 0111 B 4 7 H | (A0-3)↔(A4-7) | Обмен тетрад в А | |

| RL A | 1110 0111 B E 7 H | (An+1)←(An), n=0÷6 (A0)←(A7) | Циклический сдвиг А влево | |

| RR A | 0111 0111 B 7 7 H | (An)←(An+1), n=0÷6 (A7)←(A0) | Циклический сдвиг А вправо | |

| RLC A | 1111 0111 B F 7 H | (An+1)←(An), n=0÷6 (A0)←(C), (C)←(A7) | Циклический сдвиг А влево через С | |

| RRC A | 0110 0111 B 6 7 H | (An)←(An+1), n=0÷6 (A7)←(С), (С)←(A7) | Циклический сдвиг А вправо через С | |

| CLR C | 1001 0111 B 9 7 H | (С)←0 | Очистка признака С | |

| CPL C | 1010 0111 B A 7 H | (C)←not(C) | Инверсия признака С

| |

| CLR F0 | 1000 0101 B 8 5 H | (F0)←0 | Очистка признака пользователя F0 | |

| CPL F0 | 1001 0101 B 9 5 H | (F0)←not(F0) | Инверсия признака пользователя F0 | |

| CLR F1 | 1010 0101 B A 5 H | (F1)←0 | Очистка признака пользователя F1 | |

| CPL F1 | 1011 0101 B B 5 H | (F1)←not(F1) | Инверсия признака пользователя F1 | |

| ANL Pn,#d | 1001 10nn B dB 9 9÷A H dH | (Pn)←(Pn) and d | Логическое умножение (И) порта Pn с операндом-маской (n=1÷2) | |

| ANL BUS,#d | 1001 1000 B dB 9 8 H dH | (BUS)←(BUS) and d | Логическое умножение (И) порта BUS с операндом-маской | |

| ANLD Pn,A | 1001 11nn B dB 9 C÷F H dH | (Pn)←(Pn) and (A0-3) | Логическое умножение (И) порта Pn схемы расширителя и А (n=4÷7) | |

| ORL Pn,#d | 1010 10nn B dB A 9÷A H dH | (Pn)←(Pn) or d | Логическое сложение (ИЛИ) порта Pn с операндом-маской (n=1÷2) | |

| ORL BUS,#d | 1010 1000 B dB A 8 H dH | (BUS)←(BUS) or d | Логическое сложение (ИЛИ) порта BUS с операндом-маской | |

| ORLD Pn,A | 1010 11nn B dB A C÷F H dH | (Pn)←(Pn) or (A0-3) | Логическое сложение (ИЛИ) порта Pn схемы расширителя и А (n=4÷7) | |

| Группа команд передачи управления | ||||

| JMP M | M10M9M800100B MB | (PC0-10)←M0-10, (PC11)←DBF | Безусловный переход на метку М (по адресу М) в пределах блока ПЗУ | |

| DJNZ Rn,M | 1110 1nnn B MB E 8÷F H MH | (Rn)←(Rn)-1; если (Rn)<>0, то (РС0-7) ←М, иначе (РС)←(РС)+2 | Декремент регистра Rn и переход на метку М (по адресу М), если Rn<>0, иначе выполняется следующая команда (n=0÷7) | |

| JC M | 1111 0110 B MB F 6 H MH | если(С)=1,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если (С)=1 | |

| JNC M | 1110 0110 B MB E 6 H MH | если(С)=0,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если (С)=0 | |

| JZ M | 1100 0110 B MB C 6 H MH | если(A)=0,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если (A)=0 | |

| JNZ M | 1001 0110 B MB 9 6 H MH | если(A)<>0,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если (A)<>0 | |

| JBn M | nnn1 0010 B MB | если(An)=1,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если n-й бит аккумулятора равен 1, (n=0÷7) | |

| JF0 M | 1011 0110 B MB B 6 H MH | если(F0)=1,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если признак пользователя F0 равен 1 | |

| JF1 M | 0111 0110 B MB 7 6 H MH | если(F1)=1,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если признак пользователя F1 равен 1 | |

| JTF M | 0011 0110 B MB 3 6 H MH | если(TF)=1,то(TF)←0, (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если признак переполнения таймера/счетчика TF равен 1

| |

| JT0 M | 0011 0110 B MB 3 6 H MH | если(T0)=1,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если на входе Т0 логическая 1 | |

| JNT0 M | 0010 0110 B MB 2 6 H MH | если(T0)=0,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если на входе Т0 логический 0 | |

| JT1 M | 0101 0110 B MB 5 6 H MH | если(T1)=1,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если на входе Т1 логическая 1 | |

| JNT1 M | 0100 0110 B MB 4 6 H MH | если(T1)=0,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если на входе Т1 логический 0 | |

| JNI M | 1000 0110 B MB 8 6 H MH | если(INT)=0,то (РС0-7) ←М, иначе (РС)←(РС)+2 | Переход, если на входе INT логический 0 | |

| CALL M | M10M9M810100B MB | ((SP)0-11)←(PC), ((SP)12-15)←(PSW4-7), (SP)←(SP)+1, (PC0-10)←M0-10, (PC11)←DBF | Вызов подпрограммы по метке М (по адресу М) | |

| RET | 1000 0011 B 8 3 H | (SP)←(SP)-1, (PC)←((SP)) | Возврат из подпрограммы (выполн. за 2 м.ц.) | |

| RETR | 1001 0011 B 9 3 H | (SP)←(SP)-1, (PC)←((SP)), (PSW4-7)←((SP)12-15) | Возврат из подпрограммы обработки прерывания (выполн. за 2 м.ц.) | |

| JMPP @A | 1011 0011 B B 3 H | (PC0-7)←((A)) | Косвенный переход в текущей странице ПЗУ программ | |

| Группа команд управления режимами работы | ||||

| STRT T | 0101 0101 B 5 5 H | Запуск таймера | ||

| STRT CNT | 0100 0101 B 4 5 H | Запуск счетчика | ||

| STOP TCNT | 0110 0101 B 6 5 H | Останов таймера/счетчика | ||

| EN TCNTI | 0010 0101 B 2 5 H | (tie)←1 | Разрешение прерывания от таймера/счетчика | |

| DIS TCNTI | 0011 0101 B 3 5 H | (tie)←0 | Запрещение прерывания от таймера/счетчика | |

| EN I | 0000 0101 B 0 5 H | (ie)←1 | Разрешение внешнего прерывания (по входу INT) | |

| DIS I | 0001 0101 B 1 5 H | (ie)←0 | Запрещение внешнего прерывания (по входу INT) | |

| SEL RB0 | 1100 0101 B C 5 H | (BS)←0 | Выбор банка регистров RB0

| |

| SEL RB1 | 1101 0101 B D 5 H | (BS)←1 | Выбор банка регистров RB1 | |

| SEL MB0 | 1110 0101 B E 5 H | (DBF)←0 | Выбор банка ПЗУ программ МB0 | |

| SEL MB1 | 1111 0101 B F 5 H | (DBF)←1 | Выбор банка ПЗУ программ МB1 | |

| ENT0 CLC | 0111 0101 B 7 5 H | Разрешение выдачи синхросигнала на выход Т0 (2 МГц) | ||

| NOP | 0000 0000 B 0 0 H | (РС)←(РС)+1 | Холостая команда | |

2020-04-07

2020-04-07 181

181