5.1. Примеры УГО элементов приведены в табл. 6 - 15 для соглашения положительной логики. Приведенные буквенные обозначения функций и меток выводов элементов являются обязательными, за исключением альтернативных, приведенных в табл. 2 или в табл. 4 (в круглых скобках). При этом допускается не указывать порядковые номера в метках выводов при обозначении зависимости.

Порядок расположения меток выводов (групп меток выводов - при их наличии) является рекомендуемым.

Указатели выводов элементов приведены в предпочтительной форме 1 табл. 3, однако допускается использовать все формы указателей, приведенных в табл. 3.

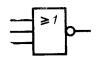

5.2. Примеры УГО логических элементов приведены в табл. 6.

Таблица 6

| Наименование | Обозначение |

| 1. Элемент «НЕТ» |

|

| 2. Элемент 3И-НЕ |

|

| 3. Элемент 2И-НЕ с открытым коллекторным выходом и повышенной нагрузочной способностью |

|

| 4. Элемент 3ИЛИ-НЕТ |

|

| 5. Комбинированный элемент 2И-ИЛИ с инвертированным выходом |

|

| 6. Элемент 4И-НЕТ с открытым коллектором на выходе |

|

| 7. Элемент 2И-ИЛИ с инвертированным выходом и расширительным входом |

|

| 8. Расширитель |

|

| 9. Элемент проверки четности или нечетности |

|

5.3. Примеры УГО приемопередающих элементов приведены в табл. 7.

Таблица 7

| Наименование | Обозначение |

| 1. Четыре шинных усилителя с двухпороговым входом и выходом на три состояния с общим входом разрешения третьего состояния |

|

| 2. Двунаправленный шинный приемопередатчик восьмиканальный |

|

| 3. Шестиканальный буферный элемент с тремя состояниями на выходе с сигналом разрешения по выходу |

|

5.4. Примеры УГО гистерезисных элементов приведены в табл. 8.

Таблица 8

| Наименование | Обозначение |

| 1. Инвертирующий усилитель с порогом Шмитта |

|

| 2. Триггер Шмитта с логическим элементом 4И на входе |

|

5.5. Примеры УГО преобразователей (дешифраторов) и кодирующих устройств (шифраторов) приведены в табл. 9.

Таблица 9

| Наименование | Обозначение |

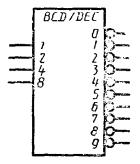

| 1. Преобразователь двоично-десятичного кода в десятичный код |

|

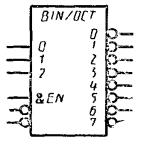

| 2. Преобразователь с трех линий на восемь |

|

| 3. Преобразователь двоичного кода в двоично-десятичный |

|

| 4. Преобразователь-усилитель двоичного кода в семисегментный. Примечание. Допускается заменить строчные буквы прописными: А, В, С, D, Е, F, G |

|

| 5. Кодирующее устройство приоритета (приоритетный шифратор) с 8 линий на 3 линии (GS - «групповой сигнал») |

|

| 6. Два дешифратора, принимающих двухразрядный код. Примечание. Допускается обозначение дешифраторов А и В, которые изображаются в качестве групповой метки выходов соответствующего дешифратора |

|

| 7. Преобразователь уровней ТТЛ в уровни МОП |

|

| 8. Преобразователь уровней ЭСЛ в уровни ТТЛ. Примечание к пп. 7 и 8. Обозначение функции преобразователя сигналов */* может быть заменено обозначением *//*, если необходимо указать наличие гальванической связи между его входами и выходами |

|

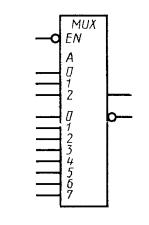

5.6. Примеры УГО мультиплексоров и демультиплексоров, а также коммутаторов цифровых и аналоговых сигналов приведены в табл. 10.

Таблица 10

| Наименование | Обозначение |

| 1. Мультиплексор на 8 входов со стробированием. Примечание. Вход стробирования EN допускается обозначать STR |

|

| 2. Демультиплексор на 8 линий |

|

| 3. Мультиплексор четырехканальный по два входа каждый |

|

| 4. Мультиплексор двухканальный по 4 входа каждый. Примечание к пп. 3, 4. При обозначении каналов мультиплексора не порядковыми номерами (1, 3 и т.д.), а буквами А, В и т.д.) для устранения неоднозначности понимания входу адреса данных присваивается метка «Выбор»: SEL или SE |

|

| 5. Электронный коммутатор |

|

5.7. Примеры УГО арифметических элементов приведены в табл. 11.

Таблица 11

| Наименование | Обозначение |

| 1. Полный одноразрядный сумматор |

|

| 2. Четырехразрядный сумматор-вычитатель |

|

| 3. Полный сумматор на 4 бита |

|

| 4. Четырехразрядное скоростное АЛУ |

|

| 5. Генератор ускоренного переноса для АЛУ |

|

| 6. Четырехразрядный цифровой компаратор |

|

5.8. Примеры УГО триггеров (бистабильных элементов) приведены в табл. 12.

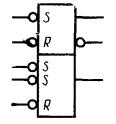

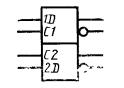

Таблица 12

| Наименование | Обозначение |

| 1. Два триггера с раздельным запуском (RS -типа), один с дополнительным входом |

|

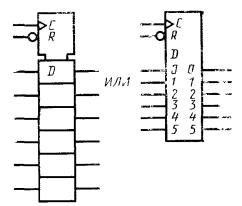

| 2. Два триггера задержки D -типа |

|

| 3. Шесть D -триггеров с общими входами управления и сброса |

|

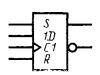

| 4. Триггер D -типа, запускаемый по фронту |

|

| 5. Триггер JK -типа, запускаемый по фронту |

|

| 6. Универсальный JK -триггер со структурой «мастер-помощник» |

|

| 7. Два JK -триггера с общими входами управления и сброса |

|

5.9. Примеры УГО моностабильных (мультивибраторов) и нестабильных элементов приведены в табл. 13.

Таблица 13

| Наименование | Обозначение |

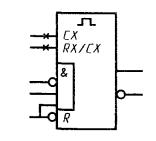

| 1. Ждущий мультивибратор с перезапуском |

|

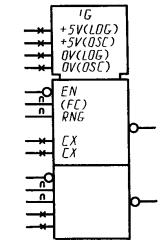

| 2. Два генератора, управляемых напряжением, с указанием выводов питания (LOG - питание цифровой части элемента, OSC - питание аналоговой части элемента, FC - управление частотой) |

|

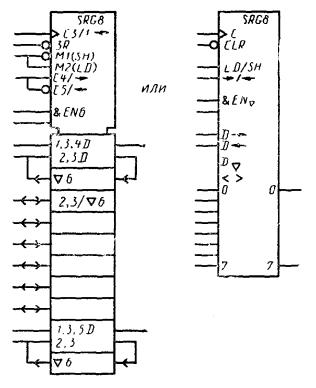

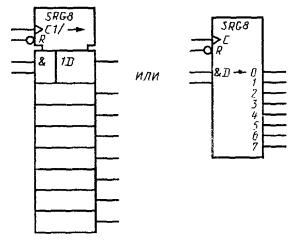

5.10. Примеры УГО регистров и счетчиков приведены в табл. 14.

Таблица 14

| Наименование | Обозначение |

| 1. Сдвиговый 4-разрядный регистр с параллельными входами |

|

| 2. Сдвиговый 4-разрядный последовательно-параллельный регистр с прямым и дополнительным кодом на выходе (Т / С - вход переключения кода на выходах: прямой или дополнительный; P / S - вход, управляющий соединением разрядов регистров последовательно или параллельно) |

|

| 3. Сдвиговый 4-разрядный двунаправленный универсальный регистр |

|

| 4. Универсальный 8-разрядный регистр |

|

| 5. Сдвиговый 8-разрядный регистр с двойным последовательным входом и параллельными выходами |

|

| 6. Сдвиговый 8-разрядный универсальный регистр с последовательным и параллельными входами и выходами (A / S - вход, переключения режимов: асинхронного или синхронного; ALD - вход разрешения параллельной записи информации в канал А) |

|

| 7. Сдвиговый 8-разрядный регистр с параллельной загрузкой |

|

| 8. Двоичный 14-разрядный счетчик со сквозным переносом |

|

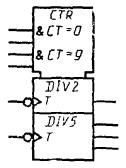

| 9. Асинхронный десятичный счетчик, состоящий из делителей на 2 и на 5 с параллельной записью |

|

| 10. 4-разрядный асинхронный десятичный счетчик, состоящий из делителей на 2 и на 5 с предварительной установкой и синхронным сбросом |

|

| 11. Синхронный десятичный счетчик с параллельной загрузкой |

|

| 12. Десятичный синхронный реверсивный счетчик |

|

5.11. Примеры УГО запоминающих устройств (ЗУ) приведены в табл. 15.

Таблица 15

| Наименование | Обозначение |

| 1. ПЗУ на 32 слова по 8 битов |

|

2. ОЗУ с произвольной выборкой на 16 слов по 4 бита.

Примечание. Обозначения выводов:

RD/WR и RD/WR и

RD/WR тождественны RD/WR тождественны

|

|

| 3. ОЗУ с произвольной выборкой на 4 слова по 4 бита с отдельной адресацией при записи и при считывании |

|

| 4. Статическое ОЗУ на 4 слова по 4 бита |

|

| 5. Статическое ОЗУ на 256 слов по 1 биту |

|

5.12. Соотношения размеров основных условных графических обозначений на модульной сетке приведены в приложении 5.

ПРИЛОЖЕНИЕ 1

Рекомендуемое

2015-01-07

2015-01-07 643

643