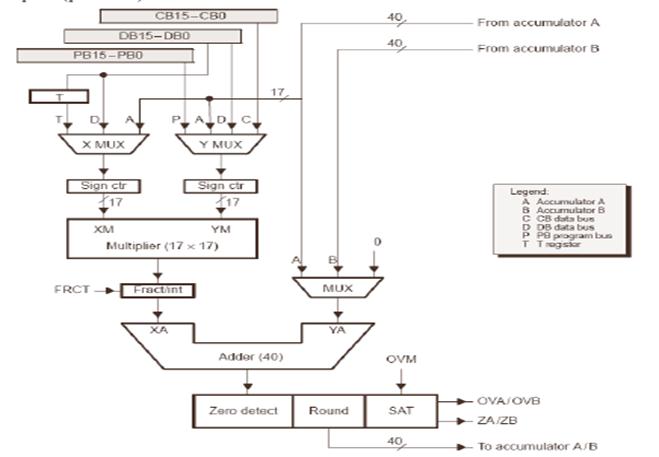

Процессор имеет устройство умножения 17 х 17 бит с 40-битным сумматором (рис. 5.7).

Умножитель позволяет выполнять знаковое, беззнаковое и знаковое на беззнаковое умножение:

• Для знакового умножения 16-битовый операнд дополняется 17-м знаковым разрядом.

• Для беззнакового умножения 16-битовый операнд дополняется 17-м разрядом равным 0.

• Для умножения знакового числа на беззнаковое один операнд дополняется знаком, а второй – 0.

Выход умножителя может быть сдвинут влево на 1 разряд для компенсации появления второго знакового разряда при умножении дробных (fractional) чиссел в дополнительном коде (выбор режима дробных чисел осуществляется установкой в 1 бита FRCT в ST1).

Сумматор содержит детектор нуля и модули округления и насыщения.

На вход XM умножителя могут подаваться:

• Временный регистр (T)

• Операнд из памяти данных через шину DB

• Разряды 32–16 аккумулятора А

На вход YM умножителя могут подаваться:

• Операнд из памяти данных через шину DB

• Операнд из памяти данных через шину CB

• Операнд из памяти программ через шину PB

• Разряды 32–16 аккумулятора А

2015-02-04

2015-02-04 767

767