Значения частоты тактового сигнала SCK

| SPR1 | SPR2 | Частота сигнала SCK |

| FCLK/4 | ||

| FCLK/16 | ||

| FCLK/64 | ||

| FCLK/128 |

Контроль состояния модуля SPI осуществляется с помощью регистра состояния SPSR (доступен только для чтения), расположенного по адресу $0E ($2E). Формаг этого регистра приведен на рис.8.3.

SPI Status Register (SPSR)

| Бит $0E($2E) R/W Нач.знач. | SPCR | ||||||||

| SPIF | WCOL | - | - | - | - | - | - | ||

| R | R | R | R | R | R | R | R | ||

Рисунок 8.3 – Регистр состояния SPI (SPSR)

Бит 7 - SPIF (SPI Interrupt Flag). Флаг прерывания от SPI. Устанавливается в «1» по окончании передачи очередного байта, а также при переводе микроконтроллера из режима Master в режим Slave посредством вывода SS (см. раздел 3.3). Флаг сбрасывается аппаратно либо при старте подпрограммы обработки прерывания, либо после чтения регистра состояния SPI с последующим обращением к регистру данных SPDR.

Бит 6 - WCOL (Write Collision Flag). Флаг конфликта записи. Устанавливается в «1» при попытке записи в регистр данных SPDR во время передачи очередного байта. Флаг сбрасывается аппаратно после чтения регистра состояния SPI c последующим обращением к регистру данных SPI.

Биты 5…0 – Зерезервированы, читаются как «0».

SPI Data Register (SPDR)

| Бит $0F ($2F) R/W Нач.знач. | SPDR | ||||||||

| MSB | - | - | - | - | - | - | LSB | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 8.4 – Регистр ввода – вывода SPI (SPDR)

Передаваемые данные записываются, а принимаемые — считываются из регистра данных SPDR, расположенного но адресу $0F ($2F). Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое приемного буфера сдвигового регистра. Поэтому этот регистр можно назвать буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI.

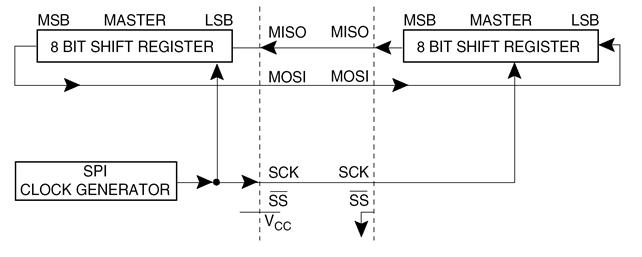

Соединение двух микроконтроллеров (ведущий ведомый) по интерфейсу SPI показано на рис.8.5. Вывод SCK ведущего микроконтроллера является выходом тактового сигнала, а ведомого микроконтроллера — входом.

Рисунок 8.5 - Соединение микроконтроллеров по интерфейсу SPI

Передача данных осуществляется следующим образом. При записи в регистр данных SPI ведущего микроконтроллера запускается генератор тактового сигнала модуля SPI, и данные начинают поразрядно выдаваться на вывод MOSI и, соответственно, поступать па вывод MOSI ведомого микроконтроллера. После выдачи последнего разряда текущего байта генератор тактового сигнала останавливается с одновременной установкой в «1» флага «Конец передачи» (SPIF). Если прерывания от модуля SPI разрешены (флаг SPIE регистра SPCR установлен в «1»), генерируется запрос на прерывание. При подключении к ведущему устройству нескольких ведомых, что разрешено спецификацией SPI, выбор конкретного ведомого устройства осуществляется подачей на его вход SS сигнала НИЗКОГО уровня.

Образно говоря, два сдвиговых регистра ведомого и ведущего устройств можно считать одним распределенным 16-разрядным циклическим сдвиговым регистром, как показано на рис.8.5. Одновременно с передачей данных от ведущего к ведомому происходит передача и в обратном направлении. Таким образом, в каждом цикле сдвига происходит обмен данными между устройствами.

В модуле используется одинарная буферизация при передаче и двойная - при приеме. Это означает, что готовый для передачи байт данных не может быть записан в регистр данных SPI до окончания предыдущего цикла обмена. При попытке изменить содержимое регистра данных во время передачи устанавливается в «1» флаг WCOL регистра SPSR. Сбрасывается этот флаг после чтения регистра SPSR с последующим обращением к регистру данных SPI.

Соответственно во время приема принятый байт должен быть прочитан из регистра данных SPI до того, как в сдвиговый регистр поступит последний разряд следующего байта. В противном случае первый байт будет потерян.

2015-03-20

2015-03-20 340

340