| Режим работы |  |  |  C C | D | Qn+1 | Qn+1  |

| Асинхронная установка | х | х | ||||

| Асинхронный сброс | х | х | ||||

| Неопределенность | х | х | ||||

| Загрузка | ||||||

| Загрузка | ||||||

| Хранение | х | Qn | Qn | |||

| Хранение | х |

а б

| Режим работы | S | R |  C C | D | Qn+1 | Qn+1 |

| Асинхронная установка | х | х | ||||

| Асинхронный Сброс | х | x | ||||

| Неопределенность | х | х | ||||

| Загрузка | ||||||

| Загрузка | ||||||

| Хранение | х | Qn | Qn |

в г

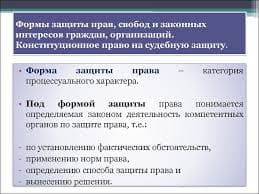

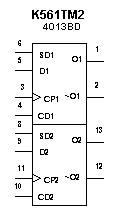

Рис. 13 Микросхемы D-триггеров

а- К155ТМ2; б- таблица функционирования К155ТМ2;

в- цоколевка К561ТМ2; г- таблица функционирования К561ТМ2

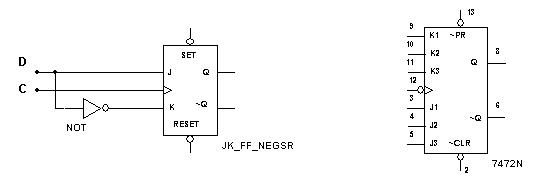

На основе двухступенчатого JK-триггера можно построить D-триггер, как показано на рис. 14.

а б

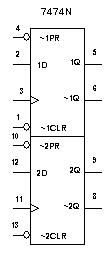

Рис. 14 Использование JK-триггера в качестве D-триггера

а- схема образования D-входа

б- микросхема К155ТВ1 (7472)

В отличие от защелки такой D-триггер будет непрозрачен по D-входу. Явление захвата и проскока у него отсутствуют, т.к. триггер переключается перепадом.

Рассмотренные триггеры объединяют в схемы, которые могут выполнять более сложные задачи, чем одиночный триггер. Наиболее известными и применяемыми являются регистры и счетчики.

Для запоминания и преобразования многоразрядных слов необходимое число триггеров объединяют в единый функциональный узел- регистр. Регистры, построенные на триггерах-защелках, например К155ТМ5,К155ТМ7, К561ТМ3 и др. можно рассматривать как четырехразрядные регистры- защелки, имеющие информационные входы Di, вход сигнала записи- С, вход гашения-R, выходы триггеров Qi. Занесение информации в регистр называют операцией ввода или записи, а извлечение ее из регистра- выводом или считыванием. Немаловажным обстоятельством является возможность записи новой информации в регистр без его предварительного обнуления.

Все регистры в зависимости от функциональных свойств подразделяются на две категории- накопительные (регистры памяти, хранения) и сдвигающие. В свою очередь сдвигающие регистры делятся по способу ввода и вывода информации на параллельные, последовательные и комбинированные, по направлению передачи (сдвига) информации на однонаправленные и реверсивные.

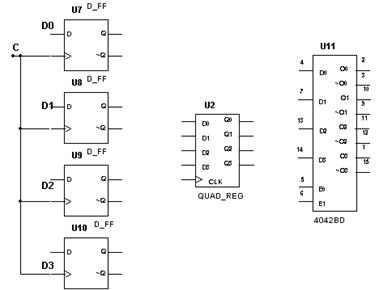

На рис. 15 приведена схема регистра памяти, предназначенного для хранения двоичной информации небольшого объема. Регистр состоит из набора синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) информации производится параллельным кодом. Ввод обеспечивается тактовым импульсом, с приходом очередного тактового импульса записанная информация обновляется. Считывание производится в прямом или обратном коде (с инверсных выходов).

а б в

Рис. 15 Регистр памяти

а- схема;

б- четырехразрядный регистр из библиотеки MISC;

в- регистр К561ТМ3 (CD4042)

Особенностью регистра К561ТМ3 является наличие входа переключателя полярности – POLAVITY (вывод 6 на рис. 15в). Если на этом входе Е1 низкий уровень, информация от входа Di появится на выходе Qi во время низкого уровня импульса на тактовом входе – CLOCK (вывод 5 на рис. 15в). В табл. 5 приведены сигналы управления этим регистром.

Управление К561ТМ3 Таблица 5

| CLOCK | POLAVITY | Q |

| D | ||

| Не разрешено | |

| D | ||

| Не разрешено |

Регистры сдвига, кроме операции хранения, осуществляют преобразование последовательного двоичного кода в параллельный, а параллельного в последовательный; они выполняют арифметические и логические операции, служат в качестве элементов временной задержки.

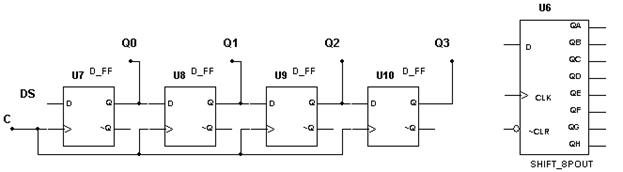

Схема сдвигового регистра приведена на рис. 16.

а б

Рис. 16 Регистр сдвига

а- схема четырехразрядного регистра;

б- восьмиразрядный регистр сдвига из библиотеки MISC

С приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования единиц и нулей. На отечественных схемах символом регистра служат буквы RG, а стрелка указывает направление сдвига: сдвиг информации влево от младших разрядов к старшим, сдвиг информации вправо, символ реверсивного (двунаправленного) регистра.

С приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования единиц и нулей. На отечественных схемах символом регистра служат буквы RG, а стрелка указывает направление сдвига: сдвиг информации влево от младших разрядов к старшим, сдвиг информации вправо, символ реверсивного (двунаправленного) регистра.

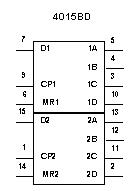

В качестве примера на рис. 17 приведены параметры регистра CD4015, которому соответствует отечественный аналог К561ИР2.

| Вход | Выход | |||

| CP | D | MR | QA | Qn |

| Qn-1 | |||

| Qn-1 | |||

| Х | QA | Без изменения Qn | |

| Х | Х |

а б

Рис. 17 Микросхема регистра К561ИР2

а- библиотечное изображение 4015BD;

б- таблица состояний

Как видно из рис. 17а микросхема К561ИР2 (CD4015) содержит два независимых четырехразрядных регистра сдвига. Каждый регистр имеет четыре выхода Q от каждого триггера (1A-1D и 2A-2D). Все триггеры регистра двухступенчатые D- типа. Данные в регистр вводятся через последовательный порт D (D1 и D2). Регистр имеет вход тактовых импульсов- CP, причем данные принимаются от входа D первого триггера и сдвигаются на один шаг влево (от младших разрядов к старшим) после каждого положительного тактового перепада на входе CP. Обнулить триггеры регистра можно подав на вход асинхронного сброса MR напряжение высокого логического уровня.

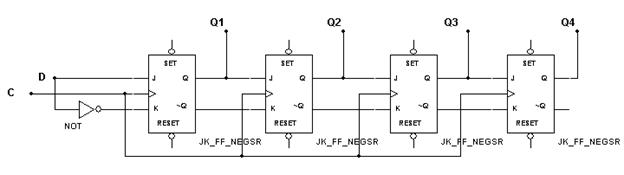

На рис. 18 представлена схема сдвигового регистра, образованного из JK-триггеров. Схема образования функции D-триггера показана на рис. 14а.

Рис. 18 Сдвиговый регистр на JK-триггерах

Применение сдвиговых регистров разнообразно. В двоичной арифметике сдвиг числа на один разряд влево соответствует умножению его на 2, сдвиг вправо - делению пополам. Сдвигающий регистр, содержащий всего одну единицу, может выполнять роль счетчика, отображающего число поступивших на вход сигналов положением единицы на линейной шкале. Если на вход сдвига подать импульсы от тактового генератора, то импульсы, образующиеся на его выходах, могут быть использованы для многофазного управления, например, шаговым двигателем или многофазной синхронизации.

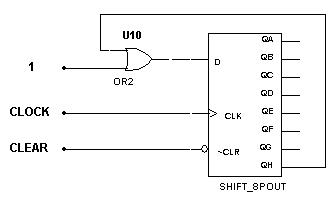

На рис. 19 представлена схема кольцевого распределителя импульсов на основе сдвигового регистра.

Рис. 19 Кольцевой распределитель импульсов

На рис. 20 представлен универсальный, восьмиразрядный, синхронный регистр сдвига К155ИР13 (74198). Входы A-H предназначены для подачи информации при параллельной записи, R и L (Right и Left) для подачи информации при последовательной записи и сдвиге вправо и влево соответственно, S0 и S1 для управления режимом, CLK (Clock) для подачи тактовых импульсов, CLR (Clear) для сброса триггеров регистра, причем этот вход обладает наибольшим приоритетом т.к. при подаче 0 происходит сброс всех триггеров независимо от состояния других входов.

а

| Режим работы | Вход | Выход | ||||

| CLK CLR | S0 S1 | DR DL DA | QA | QB-QG | QH | |

| Сброс | Х 0 | Х Х | Х Х Х | 0 - 0 | ||

| Хранение |  1 1 | 0 0 | Х Х Х | qa | qb-qg | QH |

| Сдвиг влево |  1 1 | 1 0 | Х 0 Х | qb | qc-qh | |

1 1 | 1 0 | X 1 X | qb | qc-qh | ||

| Сдвиг вправо |  1 1 | 0 1 | 0 X X | qa-qf | qg | |

1 1 | 0 1 | 1 X X | qa-qf | qg | ||

| Параллельная загрузка |  1 1 | 1 1 | 1 1 dn | da | db-dg | dh |

б

Рис. 20 Регистр К155ИР13 (74198)

а- цоколевка микросхемы;

в- таблица функционирования

Другим устройством, объединяющим ряд триггеров, является счетчик. Как уже было показано, сдвиговый регистр можно рассматривать в функции счетчика, например, счетчик Джонсона по своей структуре не что иное, как сдвиговый регистр.

Счетчиком называют устройство, сигналы на выходе которого отображают число импульсов, поступивших на счетный вход. По мере поступления входных сигналов счетчик последовательно перебирает свои состояния в определенном для данной схемы порядке. Длину списка используемых состояний называют модулем пересчета или емкостью счетчика.

Различные схемы счетчиков могут перебирать свои состояния в различном порядке. Различают: двоичное кодирование, когда порядок смены состояний триггеров соответствует последовательности двоичных чисел, одинарное кодирование, когда состояние счетчика представлено местом расположения единственной единицы (например, сдвигающий регистр с одной двигающейся единицей), унитарное кодирование, когда состояние представлено числом единиц (например, счетчик Джонсона) и более сложные виды кодирования.

По направлению счета известны суммирующие, вычитающие и реверсивные, а по способу организации внутренних связей – с непосредственной связью, с трактом последовательного переноса, с параллельным переносом, комбинированные и кольцевые.

К классификационным признакам счетчиков относятся также следующие временные показатели: Траз.сч. разрешающая способность – минимальное время между двумя входными сигналами, в течение которого не возникают сбои в работе (обратная величина Fмакс.= 1\Траз.сч. называется максимальной частотой счета), время установки кода Туст. - равное времени между моментом поступления входного сигнала и переходом счетчика в новое устойчивое состояние. Эти параметры зависят от быстродействия триггеров и способа их соединения между собой.

Классификационные признаки независимы и могут встречаться в различных сочетаниях.

Микросхемы счетчиков выпускают в составе целого ряда серий, как правило, в корпусах с 14 или 16 выводами, по четыре триггера в корпусе и хорошо приспособлены к наращиванию разрядности.

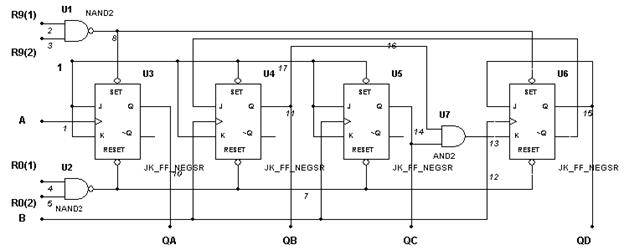

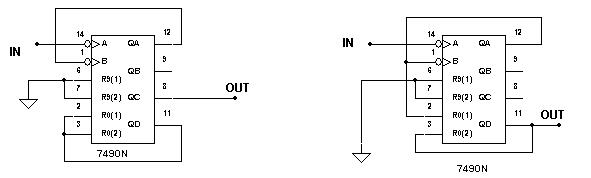

Варьируя связи между триггерами, предприятия изготавливают микросхемы счетчиков с различными модулями пересчета, например, 6,10,12. В некоторых ТТЛ сериях счетчик разбивается на две части: триггер (т.е. счетчик на 2), с выведенными входом и выходом и счетчик на 8,6 или 5, также с собственными входом и выходом. В результате одну и ту же микросхему можно использовать как счетчик с несколькими коэффициентами счета. Типичным представителем этого семейства является счетчик К155ИЕ2 (SN 7490) – четырехразрядный десятичный асинхронный счетчик пульсаций, приведенный на рис. 21. Он состоит из делителей на 2 и на 5, выполненных на тактируемых JK-триггерах. Для обоих тактовых входов запускающим перепадом является переход от 0 к 1.

Рис. 21 Структура счетчика К155ИЕ2

R9(1), R9(2) – входы предварительной загрузки в счетчик кода 10012=910

R0(1), R0(2) - входы синхронного сброса

A – тактовый вход первой ступени Ксч.=2

B – тактовый вход второй ступени Ксч.=5

QA – выход триггера первой ступени счетчика

QB, QC, QD – выходы триггеров второй ступени счетчика

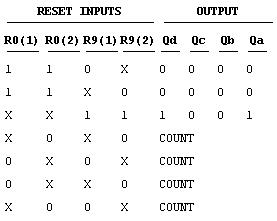

На рис. 22 приведены условное обозначение микросхемы и таблица функционирования.

а б

Рис. 22 Микросхема К155ИЕ2 (SN 7490)

а – таблица выбора режима работы

б - цоколевка микросхемы

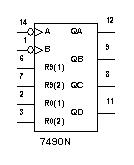

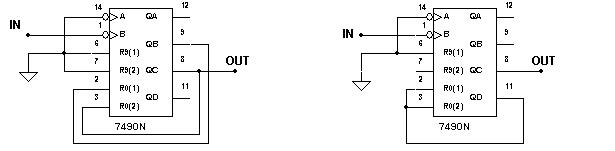

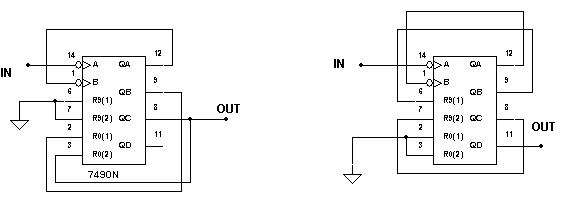

На рис. 23 показаны возможные способы изменения коэффициента счета микросхемы К155ИЕ2 без применения внешних дополнительных логических элементов.

а б

в г

д е

Рис. 23 Схемы внешних соединений при изменении коэффициента счета

а – Ксч.=3

б - Ксч.=4

в - Ксч.=6

г - Ксч.=7

д - Ксч.=8

е - Ксч.=9

Образование недостающих коэффициентов: 2, 5 и 10 очевидно и не требует пояснений.

В табл. 6 приведены функциональное назначение и соответствие между наиболее популярными отечественными и зарубежными сериями ТТЛ и КМОП микросхем счетчиков.

Таблица 6

Соответствие наименований зарубежных и отечественных микросхем

| К155 | SN 74 | Функциональное назначение | К561 | CD 4000 | Функциональное назначение |

| ИЕ2 | Четырехразрядный асинхронный дво- ично-десятичный счетчик | ИЕ8 | Десятичный счетчик-делитель Джонсона | ||

| ИЕ4 | Четырехразрядный асинхронный счетчик-делитель на 12 | К176 ИЕ1 | Семиразрядный счетчик-делитель | ||

| ИЕ5 | Четырехразрядный асинхронный двоичный счетчик | ИЕ20 | 12-ти разрядный двоичный счетчик | ||

| ИЕ6 | Четырехразрядный реверсивный двоично-десятичный счетчик | Нет аналога | Реверсивный счетчик с предустановкой | ||

| ИЕ7 | Четырехразрядный реверсивный двоичный счетчик | ИЕ11 | Реверсивный счетчик с предустановкой | ||

| ИЕ9 | Четырехразрядный синхронный двоично-десятичный счетчик | ИЕ10 | Двойной четырехразрядный двоичный счетчик |

Счетные микросхемы выпускают в виде как счетчиков-делителей, имеющих лишь счетный вход и выход переноса, без выводов состояний триггеров, так и собственно счетчиков, у которых выведены выходы всех триггеров, а иногда и их входы Di для параллельной загрузки начального состояния. Большинство счетчиков имеет вход гашения R. Загрузку и гашение обычно делают по приоритетным S и R входам триггеров, а J и K входы используют только для счета. Как правило, вход управления параллельной загрузкой PL имеет приоритет по отношению к счетному входу, т.е. при одновременной подаче активного счетного фронта и активного уровня загрузки операция счета игнорируется, а выполняется операция параллельной загрузки кода со входов Di. Вход гашения R практически всегда имеет наивысший приоритет по отношению как к счету, так и к загрузке.

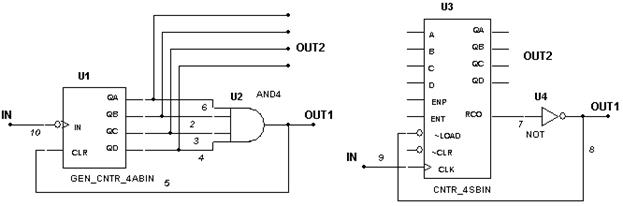

Изменить коэффициент счета готового счетчика на желаемое значение можно двумя основными способами: со сбросом счетчика в 0 и с загрузкой дополнения. На рис. 24 приведены схемы реализации этих способов.

а б

Рис. 24 Структурные схемы счетчиков по произвольному основанию

а – со сбросом счетчика в 0

б – с загрузкой дополнения

Идея работы схемы по рис.4а заключается в обнаружении кода конца счета, для чего двоичный счетчик разрядности n (причем чтобы 2n было больше Ксч.), дополняется элементом И, который по состояниям выходов Qi обнаруживает ситуацию Ксч.-1, после чего по цепи CLR (сброс) происходит принудительная очистка триггеров счетчика. Путем коммутации проводников № 2,3,4 и 6 на рис. 24а, можно получить желаемый коэффициент деления как в виде числа импульсов (OUT1), так и в виде параллельного кода (OUT2). По второму способу (рис.4б) двоичный счетчик перед началом счета загружается кодом дополнения числа Ксч. до 2n. Кодом конца счета в этом случае является естественное переполнение счетчика, т.е. код 1111 на выходе OUT2, обнаруживаемый штатным трактом переноса RCO, в результате чего вырабатывается сигнал OUT1, который воздействуя на вход LOAD, управляющий параллельной загрузкой, снова устанавливает в счетчике дополнение Ксч. до 2n.

Задачи

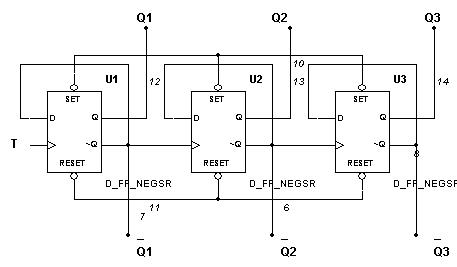

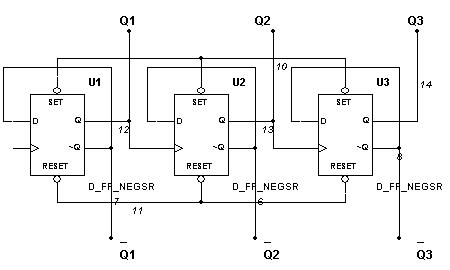

1. Используя элементы и инструменты библиотеки Multisim, построить и исследовать нижеприведенные схемы:

а. определить на каких выходах Q1-Q3 и  -

-  появляются коды увеличения и уменьшения содержимого счетчика?

появляются коды увеличения и уменьшения содержимого счетчика?

б. чему равен Ксч. этих схем?

в. построить циклограммы работы счетчиков а и б.

а

б

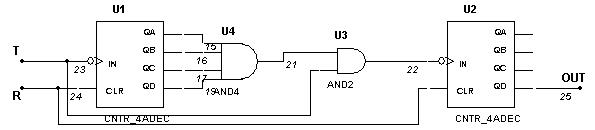

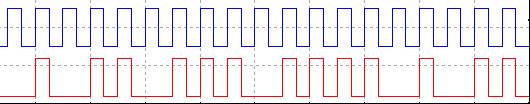

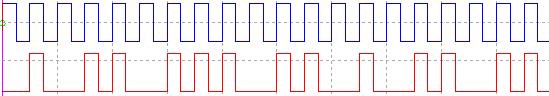

2. Определить Ксч. всей схемы.

3. Спроектировать и построить счетчик с Ксч.=123.

4. Разработать схему суммирующего счетчика с Ксч.=3 на:

а – D-триггерах;

б – JK-триггерах

Построить циклограммы работы счетчиков

5. Используя дополнительные логические элементы, превратить схемы счетчиков из задачи 1а и 1б в реверсивные.

6. Разработать схему устройства, которое имело бы цикл из восьми тактов и выдавало на выходе последовательность импульсов A при значении управляющего сигнала Z=1 и B при Z=0. Устройство построить на триггерах и логических элементах из библиотеки MISC.

| Такт | В а р и а н т ы | |||||||||||||||||||

| A | B | A | B | A | B | A | B | A | B | A | B | A | B | A | B | A | B | A | B | |

7. На триггерах типа К155ТМ2 построить делитель входной частоты на:

| В А Р И А Н Т Ы | |||||||

| Коэффициент деления |

8. Спроектировать, построить и исследовать схемы преобразователей четырехразрядных кодов: 2 в 2\10 и 2\10 в 2. Использовать счетчики К155ИЕ6 (74192) и К155ИЕ7 (74193).

9. Разработать схему электронного цифрового секундомера у которого запуск, остановка счета и сброс осуществляются одной кнопкой.

10. Разработать схему устройства, которое на четырехразрядном выходе формирует двоичные коды, возрастающие от 0 до 9, затем убывающие от 9 до 0 и т.д. Использовать счетчик К155ИЕ6 (74192).

11. Разработать схему «дозатора» импульсов, выдающего по сигналу «Пуск» одиночную пачку импульсов, содержащую заданное число импульсов, вырезанных из непрерывной последовательности входных.

| В а р и а н т | ||||||||||||||||

| Число импульсов в пачке |

12. Разработать схему устройства суммирующее входные импульсы по принципу:

а – каждый четный;

б – каждый нечетный;

в – каждый третий;

г – каждый девятый

13. Разработать схему светофора регулирования дорожного движения:

Желтый свет – 2 такта

Красный свет – 6 тактов

Желтый свет – 2 такта

Зеленый свет – 6 тактов

Желтый свет должен быть мигающим.

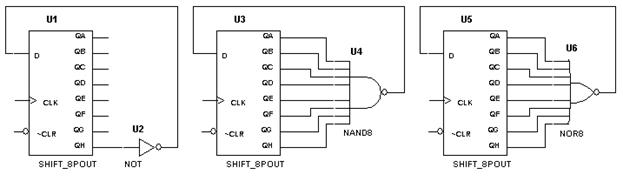

14. Разработать схему генератора импульсов:

а

б

15. Разработать схему автомата, который имел бы цикл из четырёх тактов и выдавал на шести выходах последовательности импульсов, указанные в таблице.

| Номер такта | У1 | У2 | У3 | У4 | У5 | У6 |

16. Разработать схему автомата, который имел бы цикл из восьми тактов и выдавал одновременно на двух отдельных выходах последовательности импульсов в соответствии с таблицей.

| Номер такта | У1 | У2 |

17. Разработать схему перестраиваемого автомата, который имел бы цикл из четырех тактов и выдавал на единственном выходе при управляющем сигнале z=0 последовательность У1, а при Z=1 последовательность У2.

| Номер такта | У1 | У2 |

18. Разработать схему управляемого суммирующего счетчика в котором при управляющем сигнале Z = 0 модуль счета к=8, а при Z = 1 к=5.

19. Спроектировать устройство «кольцевой бегущий огонь» из 8-ми лампочек. Устройство должно выполнять следующие функции:

а - останавливать вращение;

б – менять направление вращения;

в – осуществлять сдвиг пачки от одной до семи горящих лампочек;

20. Разработать схему управления многофазным шаговым двигателем согласно таблице вариантов (A – H).

| Наличие импульса напряжения на фазах двигателя | Количество фаз в двигателе | |||

| Только на одной фазе | A | B | C | D |

| Одновременно на двух соседних фазах | E | F | G | H |

Схема должна иметь возможность остановки двигателя без снятия напряжения с фаз и изменения направления вращения.

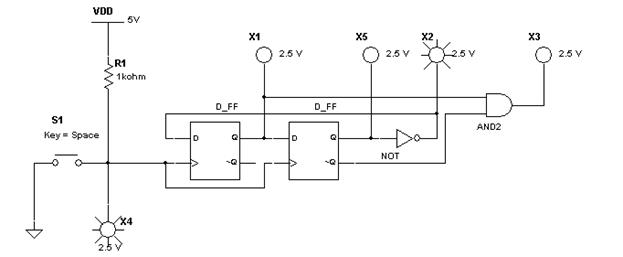

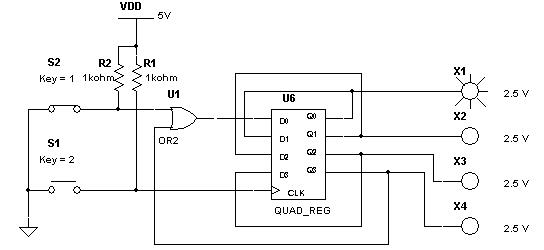

21. Составить схему устройства на сдвиговом регистре, которое в течение 4-х тактов вырабатывало бы на выходе последовательность импульсов согласно таблице задания. Регистр образовать из триггеров и логических элементов библиотеки Multisim. Оснастить схему средствами управления и контроля. Пример схемы для варианта № 1 приведен ниже.

| № такта | В А Р И А Н Т Ы | |||||||

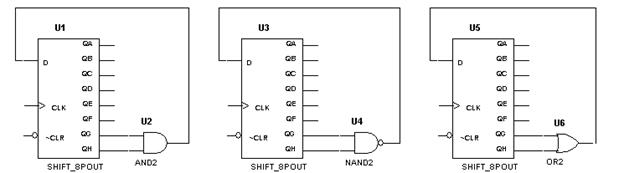

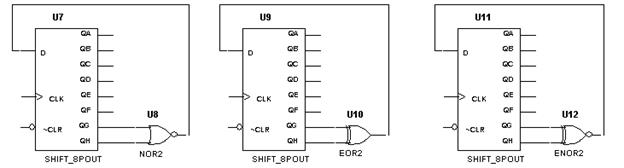

22. Исследовать нижеприведенные схемы кольцевых распределителей импульсов на основе регистра сдвига. Пример образования регистра сдвига из библиотеки MISC и оснащения его средствами управления и контроля приведен ниже. Определить длительность цикла.

а б в

г д е

ж з и

2015-05-05

2015-05-05 3853

3853