БИС КР580ИК80А (рис.2.2) - это 8-разрядный процессор, в котором совмещены операционное и управляющее устройства. Управляющая память (микропрограммная) недоступна пользователю, в ней в процессе изготовления БИС уже записаны микропрограммы операций (микропрограммы, по которым выполняются команды). Другими словами, предусматривается использование некоторой фиксированной системы команд, в которую пользователь не может внести изменения.

Д0...Д7 МД

Д0...Д7 МД

Буфер

данных Внутренняя

данных Внутренняя

шина данных

шина данных

|  | ||||||||||||||

|  | ||||||||||||||

|  |  |  | ||||||||||||

Акку- (8) Буфер-(8) Регистр (5) Регистр (8)

Акку- (8) Буфер-(8) Регистр (5) Регистр (8)

мулятор ный признаков команд

мулятор ный признаков команд

регистр Мультиплексор

регистр Мультиплексор

(8) Дешифра- W (8) Z (8)

(8) Дешифра- W (8) Z (8)

Буферный (8

Буферный (8

) АЛУ тор команд Схема B (8) C (8)

) АЛУ тор команд Схема B (8) C (8)

регистр выбо- D (8) E (8)

регистр выбо- D (8) E (8)

ра H (8) L (8)

ра H (8) L (8)

Схема реги- Указатель стека

Схема реги- Указатель стека

десятичной стров Счетчик команд

десятичной стров Счетчик команд

коррекции Регистр адреса

коррекции Регистр адреса

|

Блок управления

Буфер адреса

Буфер адреса

Управляющее устройство

Управляющее устройство

|

|

|

(6) МУ (6) А0...А15 МА

(6) МУ (6) А0...А15 МА

| |||

| |||

Ф1 Ф2 Сброс Разрешение Прием с Запись

Готовность прерывания шины данных Ожидание

Запрос прерывания Подтверждение Синхронизация

Запрос захвата захвата

Рис.2.2. Структурная схема КР580ИК80А.

Регистры. Для хранения участвующих в операциях данных предусмотрено семь 8-разрядных регистров. Регистр А, называемый аккумулятором, предназначен для обмена информацией с внешними устройствами. При выполнении арифметических, логических и операций сдвига он служит источником операнда, в него помещаетсярезультат операции.

Шесть других регистров, обозначаемых B, C; D, E; H, L образуют БРОН. Название “регистры общего назначения” связано с тем, что эти регистры могутиспользоваться как для данных, так и для адресов. Эти регистры могут использоваться как 8-разрядные одиночные регистры. Когда необходимо хранить 16-разрядные двоичные числа, регистры объединяются в следующие пары: BC, DE, HL.

Регистры “Буф.регистр 1”, “Буф.регистр 2”, W и Z используются как буферные, рпограммно-недоступные.

16-разрядный указатель стека (SP) служит для адресации организуемого в ОЗУ стека.

СчК (16 разрядов) предназначен для хранения адреса команды. После выбора из ОЗУ очередной текущей команды содержимое СчК увеличивается на +1, и таким образом (в отсутсвие переходов) формируется адрес очередной команды.

При обращении к памяти в качестве адреса может использоваться и содержимое любой пары регистров из РОН.

При выдаче адреса содержимое соответствующих регистров передается в 16-разрядный РА, из которого через буфер адреса поступает на 16-разрядную МА. Число адресов при прямом обращении к памяти 2^16=64К.

|

|

|

АЛУ. В 8-разрядном АЛУ могут быть выполнены по четыре разновидности арифметических, логических и сдвиговых операций. Для операций первых двух типов одним из операндов служит содержимое аккумулятора, и результат также помещается в аккумулятор. Сдвиг выполняется только над содержимым аккумулятора.

Арифметические операции могут выполняться над десятичными числами, представленными в коде 8421 (в нем одна десятичная цифра представляется значениями четырех двоичных разрядов). Разряды регистров делятся на две группы по четыре разряда. При суммировании десятичных чисел в таком коде может потребоваться коррекция результата путем прибавления к нему числа 0110. В каждом квартете (четырех разрядах результата) такая коррекция в МП выполняется схемой десятичной коррекции (СДК).

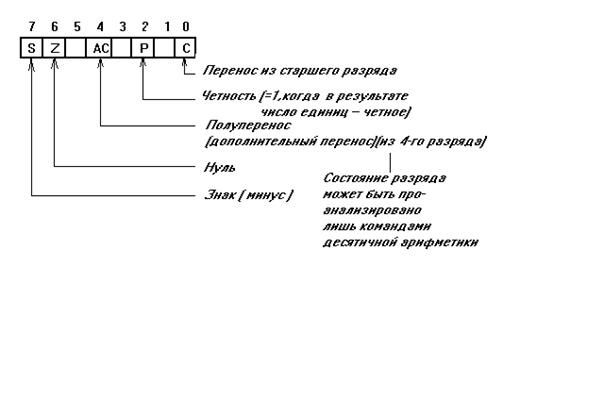

Регистр признаков (РП). 5-разрядный регистр,предназначен для хранения определенных признаков числа-результата некоторых операций (рис.2.3.).

Рис.2.3. Регистр признаков КР580ИК80А

Блок управления состоит из РК (регистра команд),куда принимается 1-й байт команды,и управляющего устройства (УУ),формирующего управляющие сигналы,под действием которых выполняются микрооперации в отдельных узлах,и содержащего выполненную на ПЛМ(программируемой логической матрице) УП (управляющую память),в которой хранятся микропрограммы отдельных операций.Буферы данных и буферы адреса обеспечивают связь центрального процессора с внешними МД и МА.Их особенность-в каждом разряде эти буферы используют логические элементы с тремя состояниями.Кроме состояний логического 0 и логической 1,имеется еще одно,в котором они имеют практически бесконечное сопротивление.Использование таких буферов позволяет: 1) микропроцессору отключаться от внешних магистралей МА иМД,предоставляя их в распоряжение ВУ; 2) использовать одну и ту же МД как для приема данных,так и для их передачи,что позволяет сократить число выводов корпуса МП.

Выдача/прием информации о состоянии МП КР580ИК80А

в специальный регистр/системный контроллер

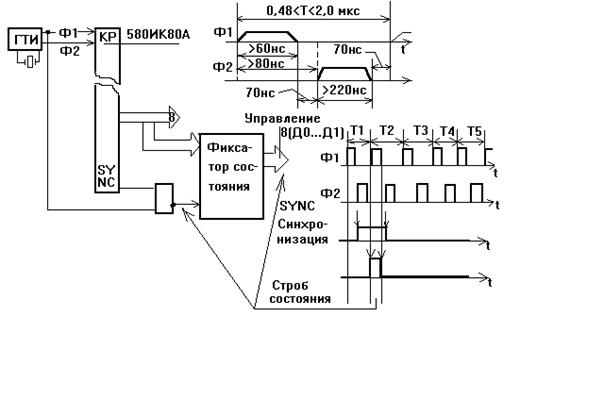

Процесс выполнения всякой команды разбит на циклы М1,...,М5.В каждом цикле производится одно обращение МП к памяти/УВВ (за исключением одной лишь команды ДАД).В зависимости от типа команды ее выполнение может занять от одного (М1) до пяти (М1,...,М5) циклов.

Каждый цикл включает в себя несколько тактов: Т1,...,Т5.Циклы могут содержать три (Т1,...Т3),четыре (Т1,...,Т4) либо пять (Т1,...,Т5) тактов.Первые три такта во всех циклах используются для организации обмена с памятью /УВВ,такты Т4 и Т5,если они есть в цикле,-для выполнения внутренних операций в МП.

Каждый из восьми разрядов (Д0,...Д7) кода состояния МП, зафиксированного в системном контроллере (рис.2.4.),имеет свою трактовку в течении соответствующих циклов команд.

Рис.2.4. Взаимодействие КР580ИК80А с системным контроллером.

Рис.2.4. Взаимодействие КР580ИК80А с системным контроллером.

Например,Д2 свидетельствует о том,что в данном цикле на адресной шине (МА) установлено содержимое указателя стека (SP).Д2=1 лишь в двух типах циклов из десяти возможных: ”Чтение стека”,”Запись в стек”.

В течении остальных типов циклов,например,”Выборка 1-го байта команды”,или “Подтверждение прерывания”, Д2=0.

Однокристальный микропроцессор К1801ВМ1/ВМ2

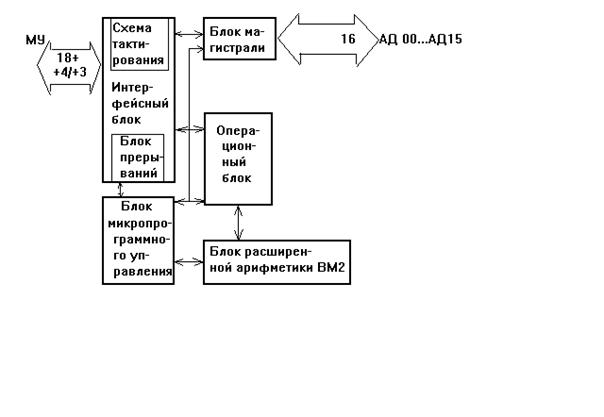

16-разрядный МП К1801ВМ1 предназначен для обработки цифровой информации в системах управления,связи,контрольно-измерительной аппаратуре (рис.2.5).

Рис.2.5. Укрупненная структурная схема К1801ВМ1/ВМ2

Операционный блок - 16-разрядный - обеспечивает формирование адресов команд и данных,выполнение арифметических и логических операций,временное хранение операндов и результатов операций.Блок расширенной арифметики МП К1801ВМ2 (рис.2.5.) реализует команды умножения,деления,сдвига на N разрядов одиночного и двойного слова.

|

|

|

Блок микропрограммного управления (БМУ) предназначен для выработки последовательности микрокоманд, соответствующей выполняемой команде.

Интерфейсный блок обеспечивает обмен управляющей информацией между МП и его окружением.Здесь в его состав включен блок прерываний, который обеспечивает работу проритетной системы прерываний, производя прием и предварительную обработку внутренних и внешних запросов прерывания. В этот блок также входит схема тактирования, обеспечивающая синхронизацию всех функциональных блоков МП.

Блок магистрали связывает внутреннюю магистраль МП с внешней магистралью Адрес/Данные (МА/МД), т.е. системной магистралью МПС.

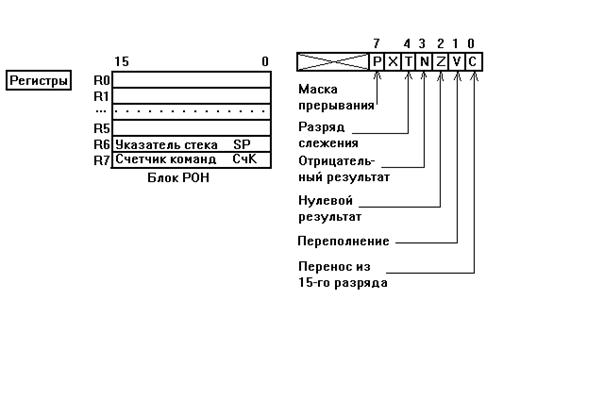

К1801ВМ1 реализует систему команд “Э-60”.Посмотрим поэтому более подробно ресурсы операционного блока (регистры), используемые командами (рис 2.6.).

Рис.2.6. Регистры общего назначения и признаков К1801ВМ1

Рис.2.6. Регистры общего назначения и признаков К1801ВМ1

Большинство РОН являются универсальными: выполняют функции аккумуляторов, базовых регистров, указателей адресов и т.д. Два РОН используются специальным образом: R0 интерпретируется командами работы с подпрограммами и прерываний как аппаратный указатель стека (SP), R7 служит счетчиком команд (СчК) и не может выполнять функции аккумулятора.

В регистре признаков (состояний) процессора хранятся коды условий (N, Z, V, C), которые информируют о результате выполнения операции.

Маска прерывания “Р”. Если Р=0, то сигнал прерывания принимается к обработке, т.е. происходит прерывание текущей программы.При Р=1 прерывание запрещено (замаскировано).

Разряд слежения “Т”. Если Т=1 (устанавливается программистом), то выполняемая программа прерывается сразу после выполнения текущей команды. Другими словами, установкой Т=1 программист обеспечивает возможность покомандного выполнения отлаживаемой программы.

Глава 3. ПОДСИСТЕМА ПАМЯТИ МИКРОПРОЦЕССОРНЫХ СИСТЕМ.

Память ЭВМ - функциональная часть ЭВМ, используемая для хранения данных, запоминания результатов операций команд, сохранения информации о состоянии процессора и т.п. В микроЭВМ применяется исключительно полупроводниковая память (здесь речь не идет о внешних запоминающих устройствах), стоимость которой составляет значительную часть всей стоимости микроЭВМ.

|

|

|

Запоминающие устройства (ЗУ) - комплекс технических средств, предназначенный для приема, хранения и выдачи информации, представленной двоичным словом.

Запоминающие элементы (ЗЭ), или элементы памяти, -простейшие схемы или физические среды, предназначенные для приема, хранения и выдачи одного бита информации.

Характеристики ЗУ:

емкость (информационная емкость) - колличество битов (байтов, слов, и т.п.), вмещаемое памятью:

1К=210=1024, 1М=220=1048676,1Г=230=1073741824;

стоимость одного бита, определяемая как отношение стоимости памяти к ее емкости;

возможность изменения информации, зависящая от типа памяти;

оперативное ЗУ (ОЗУ) - память с произвольным доступом к словам, хранимымв ЗЭ с “легко” изменяемыми состояниями;

постоянное ЗУ (ПЗУ;ППЗУ - программируемое ПЗУ) - память с произвольным доступом к словам, хранимым в ЗЭ с единожды (при изготовлении или перед установкой в ЭВМ) определенным состоянием.

СППЗУ, ЭСППЗУ - стираемое, электрически стираемое (ЭИПЗУ - электрически изменяемое) программируемое ПЗУ - разновидности ППЗУ. Их содержимое (СППЗУ) можно стереть в специальной установке, а затем вновь заполнить информацией. ЭСППЗУ можно стирать (записывать) на той же плате - без удаления из микроЭВМ;

способ выборки информации. Два основных типа ЗУ: с произвольной и последовательной выборкой. В первых т.н. время доступа к данному слову не зависит от месторасположения этого слова в памяти, а во вторых - зависит;

сохранение информации при отключении питания. В некоторых видах ЗУ, например, полупроводниковых ОЗУ, происходит потеря информации даже при кратковременных прерываниях питания. Это - энергозависимые ЗУ. В энергонезависимых ЗУ информация при отключении питания сохраняется. Таковы все ПЗУ и ППЗУ;

временные соотношения.

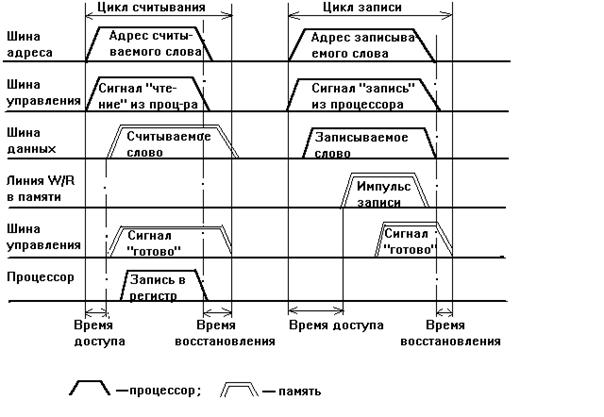

Иллюстрирующие эти соотношения временные диаграммы приведены на рис.3.1.

Время доступа - интервал от момента выставления процессором на адресной магистрали адреса требуемой ячейки памяти и посылки по МУ сигнала “ЧТ” или, соответственно, “ЗП” до момента осуществления связи этой ячейки с МД.

Время восстановления - время, необходимое для приведения памяти в исходное состояние после снятия процессором с магистралей адреса, и (или) данных, и (или) сигнала ЧТ/ЗП.

Цикл считывания - цикл записи - время с момента выдачи процессором адреса нужной ячейки памяти (и сигнала “ЧТ” или “ЗП” - они могут выдаваться позже) до момента окончания действий, связанных с выполняемой операцией ЧТ/ЗП, когда память будет готова реализовать следующую операцию. Если длительность цикла считывания равна длительности цикла записи, то иногда используют обобщающий термин - цикл памяти.

Время записи - интервал времени, необходимый для переписи содержимого магистрали данных в связанную с ней ячейку памяти. Минимальная величина этого интервала определяется физическими свойствами элементов памяти. Спецсхема в памяти вырабатывает импульс записи (см.рис.3.1.) нужной длительности. Этот импульс выдается в конце интервала времени доступа. После окончания импульса записи память сообщает процессору о выполнении операций “ЗП” посылкой сигнала “Готово”.

Рис.3.1. Временные соотношения работы с памятью

Структура ЗУ с произвольным доступом

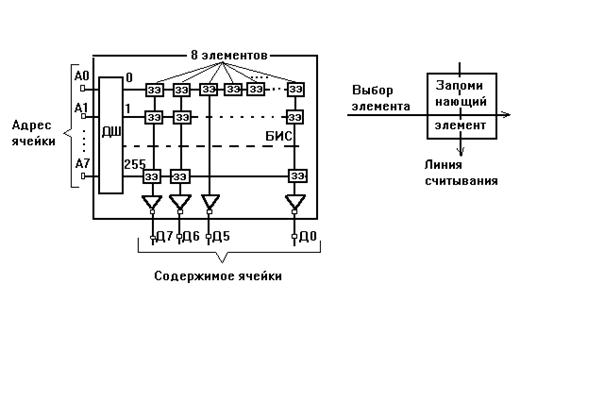

Существуют две основные организации ЗЭ внутри БИС памяти и самих БИС в памяти ЭВМ - одномерая (словарная, линейная, однокоординатная) и двумерная (матричная).

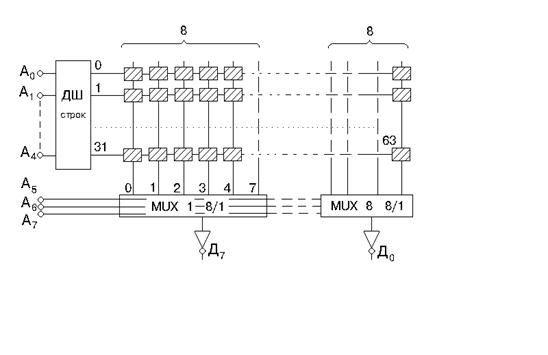

Одномерная организация. Пусть кристалл БИС содержит 256 8-битовых слов (256x8=2048=2К. Такая емкость может быть организована также в ввиде 2К однобитовых слов 2Кx1, или 512x4-битовых слов). Такой кристалл с одномерной организацией имеет 28=256 строк по восемь элементов в каждой (рис.3.2.)

Рис.3.2. ЗУ 256x8 с одномерной организацией

При поступлении на входы кристалла адреса ячейки на одном из 256 выходов ДШ появляется сигнал, выбирающий строку из восьми ЗЭ. В зависимости от содержимого ЗЭ на его линии считывания появляются 0 или 1, которые через усилитель считывания попадают на соответствующий выход (Д0,...,Д7).

При значительном объеме ЗУ (большое число адресов) резко возрастает число выходов ДШ. Это усложняет производство таких “одномерных” БИС ЗУ.

Двумерная организация. Для уменьшения числа выходов ДШ используют двумерную организацию. На рис.3.3. приведен простой пример двумерной организации того же БИС 256x8 - в виде восьми двумерноадресуемых ЗУ 256x1.

Рис. 3.3. ЗУ с двумерной организацией

Рис. 3.4. ЗУ 256х8 с двумерной организацией и матрицей 32х64

На практике при организации БИС ПЗУ для хранения многобитовых слов ЗЭ стараются размещать в матрицы с примерно равным (обычно с точностью до множителя 2) числом строк и столбцов. Поэтому на деле ПЗУ 256х8 имеет матрицу с 25=32 строками и 26=64 строками, 25х26=211=2 К (рис. 3.4).

При проектировании памяти микроЭВМ на БИС не удается, как правило, подобрать такую серийную БИС, которая содержала бы нужное число слов нужной разрядности. Сейчас промышленность выпускает около 10 различных по емкости БИС ОЗУ с 1-битовыми и, реже, 4-битовыми словами, и несколько больше различных по емкости БИС ПЗУ (ППЗУ, СППЗУ) с 4-битовыми и 8-битовыми словами. Поэтому память обычно составляют из нескольких однотипных БИС. Получение памяти со словами большей разрядности, чем разрядность слов БИС, не вызывает трудностей.

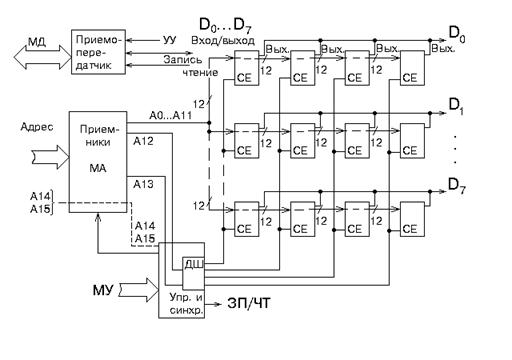

При создании памяти из множества БИС конкретный корпус выбирается с помощью внешнего дешифратора путем подачи разрешающего потенциала с выхода дешифратора ДШ на вход СЕ требуемого корпуса БИС (рис. 3.5). Входы этого внешнего ДШ подключаются к соответствующим (старшим) шинам МА. Входы/выходы внутри корпусов БИС отделены тристабильными вентилями от ЗЭ; вентили управляются сигналом СЕ. Это позволяет напрямую соединять адресные шины, входы/выходы и т.п. большого числа БИС без значительного повышения нагрузки.

Рис. 3.5. Примеры организации БИС RAM одной и той же емкости

БИС ОЗУ имеет также вход для установки ее в режим записи/чтения: R/W (ЗП/ЧТ). Входы для ввода и вывода данных могут быть раздельными или совмещенными (см. рис. 3.5).

Наибольшее распространение получили БИС ОЗУ с 1-битовыми словами. Они имеют в сравнении с БИС ОЗУ более простую внутреннюю организацию и меньше габариты. Пример сравнения - в табл. 3.1.

Таблица 3.1

Сравнение однобитовых и многобитовых БИС ОЗУ одной емкости.

| БИС ОЗУ | 64 К×1 | 8 К×8 |

| Число шин МА | 16: 116 = 64 К | 13: 210×23 = 8 К |

| Число шин МД | 1 вх., 1 вых. или 1 вх./вых. | 8 вх., 8 вых. или 8 вх./вых. |

| Итого | 17 - 18 | 21 - 29 |

БИС ПЗУ программируются при изготовлении и не имеют линии ЗП/ЧТ. БИС ППЗУ (СППЗУ) программируются по линиям вход/выход при наличии сигнала “ЗП” и изображаются так же, как БИС ОЗУ с многобитовыми словами (см. рис. 3.5).

Для упрощения на рисунке 3.6 не показаны линии входов МД в БИС памяти, и выходы Д0...Д7 не соединены с блоком приемопередатчика. Также опущена линия ЗП/ЧТ, выходящая из блока управления и синхронизации. Адресные входы всех 32 корпусов БИС соединены соответственно друг с другом. Они отвечают шинам А0...А11 МА. 12-ю разрядами адресуются 4 К бит.

Объединены также все входы ЗП/ЧТ микросхем.

32 корпуса разделены на 4 группы-столбца по 8 БИС, корпуса в столбце соединены по входам СЕ. По строкам соединены выходы Двых и входы Двх корпусов.

Для выбора одного из четырех столбцов применяется дешифратор ДШ в блоке управления и синхронизации; этот ДШ использует два старших разряда - А12 и А13.

При 16-разрядной МА старшие разряды А14 и А15 испрльзуются в блоке управления и синхронизации следующим образом. Значения А14 и А15 сравниваются в компараторе, входящем в этот блок, со значениями. обусловленными перемычками. Возможны четыре комбинации кодов перемычек. При совпадении вырабатываются нужные для работы сигналы СЕ, ЗП/ЧТ и пр.; при несовпадении данный модуль на 16 кбайт “молчит”.

Рис. 3.6. Пример структуры модуля ОЗУ

Связь модуля с системным интерфейсом осуществляется через магистральные приемопередатчики. Это набор тристабильных вентилей.

Легко видеть, почему память не может сразу по выставлении адреса на МА и приказа на считывание информации выдать содержимое адресуемой ячейки. Время доступа тратится, помимо прочего, на последовательное прохождение сигналами адреса, синхронизацию и выбор целого ряда схем.

Это время еще больше возрастает в модулях памяти, микроЭВМ с мультиплексированной магистралью МА/МД. Такие модули сначала должны прочитать с магистрали и запомнить адрес нужной ячейки, для чего в этих модулях имеется специальный буферный РА, и лишь после этого осуществить операции по выдаче или приему информации.

ЗЭ ОЗУ с произвольным доступом

В настоящее время промышленность изготовляет два основных типа запоминающих элементов ОЗУ: статические и динамические.

Статический ЗЭ - это бистабильная схема (схема с двумя устойчивыми состояниями), обычно называемая триггером. В наиболее распространенных БИС ОЗУ, построенных на МОП (металл - окисел - проводник)-технологии, такие схемы выполнены на шести транзисторах. В этих схемах два транзистора играют роль нагрузочных сопротивлений, два - образуют собственно триггер (находятся практически всегда в противоположных состояниях), два - используются для управления выбором ЗЭ и процессом переключения/чтения/записи. Более сложные 8-транзисторные схемы используют еще два транзистора для организации матричной адресации ЗЭ (выборки). Обязательно используется внешний источник питания.

Динамический ЗЭ - схема, запоминающей основой которой является емкость “затвор-исток” МОП-транзистора. Каждый динамический ЗЭ содержит, как минимум, 1 транзистор. С учетом еще двух транзисторов, обеспечивающих выбор элемента и организацию режимов чтения/записи, число транзисторов достигает трех. В результате плотность ЗЭ в динамическом ЗУ больше, чем в статическом.

Наличие заряда в емкости определяет одно логическое состояние, отсутствие заряда - другое. Из-за утечки заряда хранимая информация разрушается, поэтому каждые несколько миллисекунд должна производиться ее регенерация.

Главное достоинство динамических элементов - бо’льшая плотность на кристалле. Кроме того, динамический ЗЭ не потребляет тока - за исключением тех относительно коротких промежутков времени, когда к нему обращаются. В итоге у динамического ЗЭ меньшая стоимость, меньшие габариты, бо’льшая надежность в сравнении со статическими ЗЭ.

Основной недостаток динамических элементов - более сложные схемы управления, организующие, во-первых, регенерацию, и, во-вторых, арбитраж между процессами регенерации и запросами процессора и других устройств МПС к памяти.

Схемы регенерации являются, как правило, внешними по отношению к кристаллам памяти. Они повышают стоимость памяти, поэтому применение динамической памяти малых объемов (менее 4 - 8 кбайт) обычно не оправдано.

Разработаны псевдостатические ЗУ, у которых схемы регенерации реализованы на кристалле, благодаря чему пользователь может рассматривать их как статические.

Предварительное замечание к процедуре регенерации заключается в следующем. Возобновлять заряд надо только в том ЗЭ, где он имеется, постепенно уменьшаясь, в то время как отсутствие заряда - состояние самоподдерживающееся. Тем не менее для ускорения и для упрощения всего процесса регенерации подвергается любой ЗЭ, причем целой группой, не в одиночку. Обычно эта группа - строка при той или иной организации ЗУ (рис. 3.7). Выход каждого ЗЭ этой строки через свой усилитель, формирователь, соединяется со своим же входом, т.е. для этой строки в каждом столбце линия “ЧТ” через усилитель соединяется с линией “ЗП” того же столбца. После такого подключения усилителей выбираются ЗЭ данной строки и осуществляется собственно перезапись (регенерация).

Рис. 3.7. Упрощенная структурная схема регенерации

Количество строк динамического ЗУ и цикл памяти ЗЭ позволяют закончить весь процесс регенерации за несколько десятков микросекунд. Поскольку для большинства БИС динамических ЗУ регенерация должна выполняться через 1 - 2 миллисекунды, то на регенерацию памяти затрачивается не более 1 - 2% времени ее работы.

Однако в процессе регенерации память недоступна для других устройств, и поэтому запрос, например процессора, на запись или чтение может задержаться на несколько десятков микросекунд. Если такой режим нежелателен, то логическая схема регенерации снабжается дополнительными блоками, позволяющими приостановить процесс регенерации на время выполнения запроса процессора или другого устройства, связанного с памятью.

Постоянные ЗУ

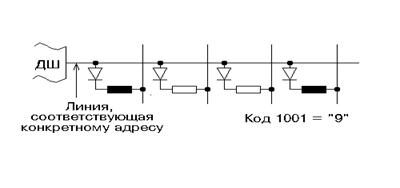

ПЗУ с масочным программированием - устройства, в которые информация записана раз и навсегда в процессе изготовления полупроводниковых БИС. Запись производится путем металлизации промежутков, позволяющих соединить через диоды (МОП-транзисторы) те строки и столбцы, которые соответствуют коду (рис. 3.8). Это делается с помощью маскирующих фотошаблонов, задающих те участки металлизации, которые нужны для кодирования той или иной информации. Изготовляют и используют ПЗУ для преобразования двоичного кода в коды символов (русских и латинских букв, цифр и пр.), в ПЗУ хранят микропрограммы, программы управляющих микроЭВМ и т.п.

Рис. 3.8. Фрагмент ПЗУ

Программируемые ПЗУ (ППЗУ). При изготовлении БИС все перемычки устанавливаются на место, так что, например, если ППЗУ имеет байтовую организацию, то по всем адресам пишутся 11111111 = FF16. Перемычки - плавкие. В ходе программирования на ППЗУ последовательно подаются адреса, а импульсами тока перемычки разрушаются в тех местах, где они не нужны. Если в ходе программирования была допущена ошибка, то она не может быть исправлена.

Стираемые, они же репрограммируемые, ППЗУ (СППЗУ) от ППЗУ существенно отличаются тем, что между строк и столбцов установлены не диоды с плавкими перемычками, а специальные МОП-транзисторы с изолированным затвором. После изготовления все МОП-транзисторы обладают очень большим сопротивлением - они закрыты.

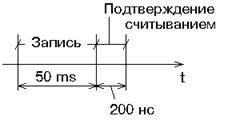

Подачей импульса большой амплитуды выбранный МОП-транзистор переводится в проводящее состояние, которое он может сохранять и после 10 лет. Типичный цикл записи/проверочного считывания приведен на рис. 3.9.

Рис. 3.9. Цикл записи-считывания при изготовлении СППЗУ

Пятьдесят миллисекунд выбраны в качестве наихудшего случая, чтобы гарантировать переключение самого неудачного в этом смысле МОП-транзистора. Однако запись таким методом 32 К слов на одном кристалле требует более 25 мин (32×103 × 0.05 с). Фирма Intel разработала метод, сокращающий время примерно в пять раз. По этому методу запись с контрольным считыванием циклически повторяется в течении одномиллисекундных импульсов до тех пор, пока запись не станет правильной. После этого осуществляется дополнительная запись в течение малого времени; вся запись в итоге длится примерно 10 миллисекунд.

Для возвращения МОП-транзисторов в исходное закрытое состояние их надо подвергнуть длительному (10 - 30 мин) облучению ультрафиолетовым излучением. Групповое облучение всех МОП-транзисторов проводится через кварцевое окошко БИС. После этого БИС СППЗУ оказывается в исходном состоянии, и ее можно снова программировать.

Электрически стираемые программируемые ПЗУ (ЭСППЗУ) отличаются от СППЗУ тем, что в них можно вернуть в исходное состояние любой отдельно взятый МОП-транзистор. Поэтому ЭСППЗУ похожи скорее на ОЗУ, у которых цикл записи в несколько тысяч раз больше цикла чтения. Кроме того, ЭСППЗУ энергонезависимы, однако они не обеспечивают столь длительного хранения информации, как СППЗУ.

ЭСППЗУ обеспечивает:

стирание и запись информации в рабочем состоянии устройства, смонтированного на плате;

пословное стирание и запись информации.

По сравнению со считыванием, которое длится примерно 250 наносекунд, стирание и запись осуществляются медленнее и требуют около 10 миллисекунд.

Надежность ЗУ

Отдельные БИС могут исправно работать десятилетия. Однако при объединении сотен и тысяч БИС среднее время между сбоями, которые возникают то в одном, то в другом кристалле, может составить всего несколько часов, что недопустимо, особенно для управляющих микроЭВМ.

В случае повреждения микросхемы возникающая ошибка становится неустранимой.

ЗЭ при этом либо “застревает” в одном положении, либо беспорядочно перебрасывается из одного состояния в другое. Если повреждены адресные линии, то ненадежными могут стать целый столбец или строка данных.

Однако ошибки возникают и в неповрежденных микросхемах. Обычными виновниками таких ошибок являются альфа-частицы, испускаемые ядрами тяжелых элементов при радиоактивном распаде. Альфа-частицы - отрицательный фактор, который присущ, как правило, устройствам памяти современных ЭВМ, так как радиоактивные атомы в небольших количествах присутствуют почти во всех материалах. В частности, атомы урана и тория содержатся в пластмассовых корпусах обычных микросхем памяти. В итоге кристалл подвергается настоящей бомбардировке.

На физическом уровне состояние ЗЭ определяется наличием/отсутствием заряда в определенной области полупроводника. Проникновение массивной и заряженной альфа-частицы в такую область может привести к изменению ее заряда, что на деле обычно соответствует переходу 1 в 0. Возникает сбой, т.е. случайная ошибка, которую можно предвидеть, но нельзя избежать.

Наиболее простой (дешевый) способ борьбы сегодня с подобными ошибками - избыточное кодирование (коды Хемминга). Его аппаратной основой служат дополнительные разряды каждого хранимого слова. Их содержимое формируется автоматически (недоступно пользователю), наподобие разряда обычного контроля на “чет-нечет”. Используется это содержимое также автоматически, обеспечивая локализацию одиночной ошибки слова и ее коррекцию, так что такая ошибка не достигает выходного контакта. Пример соотношения объемов основной и дополнительной памяти на одном кристалле: 256К*1 бит (или 64К*4 бит) - основная память, 128 К бит - дополнительная.

Использование корректирующих кодов позволяет увеличить среднее время до появления сбоя на несколько десятичных порядков.

Г л а в а 4. ОРГАНИЗАЦИЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ

Область применения микроЭВМ, т.е. класс реализуемых алгоритмов, обусловливает, во-первых, выбор типа центрального процессора и, во-вторых, количество и перечень требуемых типов внешних устройств (ВУ) и каналов связи. Оба эти фактора приводят к применяемой в большинстве МПС двухуровневой схеме сопряжения ВУ с процессором и памятью.

На 1-м уровне процессор и память сопрягаются с контроллерами ВУ (ИК) через системный интерфейс (магистрали).

На 2-м уровне сопряжения ИК посредством шин связи с ВУ соединяются с соответствующими ВУ.

На первом уровне в общем случае можно выделить два основных способа использования системного интерфейса для организации обмена информации с ВУ: 1) с применением специальных команд ввода-вывода; 2) по аналогии с обращением к памяти.

В первом случае номер (адрес) ВУ передается по магистрали адреса МА, как и адрес ячейки памяти. Как номер ВУ информация на МА интерпретируется только при наличии специальных управляющих сигналов, т.е. сигналов на МУ, например, “Ввод из ВУ” или “Вывод в ВУ”.

Для задания моментов времени, указывающих на готовность данных в ВУ для передачи в миктоЭВМ либо подтверждающих их прием в ВУ, может служить управляющий осведомительный сигнал “Готовность ВУ”.

Описанного простого набора сигналов достаточно для организации асинхронного программно-управляемого обмена данными с ВУ на 1-м уровне (процессор - ИК).

Операция ВЫВОД, инициируемая МП, выполняется следующим образом.

МП выставляет на МА адрес (номер) ВУ, на МД - значения разрядов выводимого слова данных. Далее МП единичным сигналом по линии “Вывод в ВУ” указывает тип операции (рис.4.1). Адресуемый ИК принимает данные, пересылает их в ВУ и единичным сигналом на линии “Готовность ВУ” сообщает процессору, что данные приняты ВУ и можно снять информацию с МА, МД и МУ.

|

Рис.4.1. Диаграмма операции ВЫВОД

|

Рис.4.2. Диаграмма операции ВВОД

Операция ВВОД начинается с того, что МП выставляет на МА адрес (номер) ВУ и единичным сигналом на шине “Ввод из ВУ” указывает тип операции (рис.4.2). По этому сигналу ИК считывает слово данных из ВУ, выставляет его на МД и единичным сигналом по линии “Готовность ВУ” сообщает об этом процессору. Приняв данные, МП снимает сигналы на МА и МУ.

Во втором случае, т.е. при обращении к ВУ по аналогии с обращением к памяти, отпадает необходимость в специальных сигналах, позволяющих так или иначе интерпретировать содержимое МА. ИК просто селектирует это содержимое и выделяет собственный адрес.

Однако остается необходимость передавать в ВУ приказ на ввод/вывод информации. Для этого используются шины МУ “чтение” и “запись”, используемые обычно для работы с модулями памяти. Временные диаграммы операций ВВОД и ВЫВОД для этого случая полностью соответствуют тем, что приведены на рис.4.1 и 4.2.

В принципе рассмотренный здесь минимальный набор управляющих сигналов позволяет организовать обмен с ВУ не только в асинхронном режиме, но и в режиме прерывания программы. Однако это покупается ценой существенного усложнения алгоритомв обработки управляющих сигналов и, соответственно, аппаратуры для такой обработки. Для организации прерываний и режима прямого доступа более рациональным оказывается пойти на увеличение числа управляющих сигналов, о чем речь пойдет далее.

Исключительное разнообразие ВУ микроЭВМ приводит к необходимости различать и отрабатывать в ИК большое число различных режимов работы. Организовать передачу каждого приказа ВУ по отдельной линии МУ системного интерфейса пратически невозможно по двум причинам:

1) при разработке МП трудно предвидеть все разнообразие применений микроЭВМ на его основе, а значит, и разнообразие используемых ВУ;

2) для каждого дополнительного управляющего сигнала потребуется отдельный вывод в БИС МП.

Проблема решается путем мультиплексирования МД, т.е. путем использования ее как для обмена данными с ИК в одни моменты времени, так и частью управляющей информации в другие моменты.

При этом данные должны размещаться в регистре данных ИК, а управляющая информация - в одном или нескольких регистрах управления и состояния. Их число зависит от сложности ВУ и разрядности МД. Это ставит новую задачу - выбор одного или нескольких регистров ИК ВУ.

Наиболее просто эта задача решается путем выделения своего адреса каждому регистру ИК в системе адресов микроЭВМ.

Рассмотрим далее на примере КР580 (MicroBus) и “Э-60” (Q-Bus) оба случая организации системных магистралей с использованием специальных команд и по аналогии с обращением к памяти соответственно.

Т а б л и ц а 4.1

Управляющие сигналы MicroBus

| Обозна-чение | Значение | Источник | Назначение |

| DBIN | Разрешение приема информации с МД | МП | МД D0,..., D7 находится в режиме приема информации |

| WR | Признак выдачи информации на МД | МП | На МД МП выдана информация для передачи в память или ВУ |

| READY | Готовность данных к передаче | Память, ВУ | Информация в памяти или ВУ готова для передачи в МП. При отсутствии сигнала READY МП переходит в состояние ожидания (WAIT). |

| WAIT | Ожидание | МП | МП в ожидании, выходит из него при поступлении сигнала READY |

| INT | Запрос прерывания | ВУ | Запрос ВУ на обслуживание-прерывание текущей программы после выполнения очередной команды; запрос ВУ на обслуживание в состоянии ожидания МП во время останова. |

| INTE | Разрешение прерывания | МП | Разрешение, выдаваемое для ВУ на обмен информацией в режиме прерывания программы |

| HOLD | Захват шин | ВУ | Запрос ВУ на ПДП |

| HLDA | Подтверждение захвата шин | МП | Разрешение для ВУ на обмен в режиме ПДП. МА и МД (внутренние) МП отключаются от магистралей |

| SYNC | Синхронизация | МП | Начало машинного цикла подтверждает выдачу МП на МД слова состояния МП |

| RESET | Сброс | Внешние схемы управления | СЧК—>0, триггеры разрешения прерывания и захвата шин —>0 |

Вначале - MicroBus. На рис.4.3 и в табл.4.1 приведены и раскрыты сигналы МУ.

По младшим восьми шинам 16-разрядной МА передаются адреса ВУ; соответственно можно адресовать до 256 регистров при ВЫВОДЕ (OUT) и столько же при ВВОДЕ (IN).

Тактовые сигналы Тактовые сигналы

| HOLD | RESET | READY | INT | DSIN | WR | INTE | SYNC | WAIT | HLDA |

| |||||||||||||||

| |||||||||||||||

|  |  |  | ||||||||||||

|  | ||||||||||||||

|

Рис.4.3. Сигналы МУ КР580ИК80А

Сами команды ввода/вывода идентифицируются в слове состояния МП, выводимом по МД в специальный регистр или системный контроллер. В частности, в тех типах циклов, которые отвечают вводу/выводу, разряд Д4 этого слова равен 1 лишь при выводе, Д6 - лишь при вводе.

В целом MicroBus позволяет реализовать два режима обмена с ИК ВУ: программно-управляемый асинхронный и по прерыванию программы; режим ПДП.

Допускается также обработка в МП сигналов от ВУ запроса прерывания и захвата шин во время останова МП. За счет этого удается организовать эффективное взаимодействие программ микроЭВМ и медленной периферии в системах реального времени.

Q-Bus. Здесь для адресации ВУ используется часть адресного пространства, о чем ранее уже шла речь. Можно адресовать до 4К регистров ВУ.

Управление передачей информации (адресов или данных) сводится к реализации стандартных циклов обмена (ВВОД или ВЫВОД) между двумя устройствами, подключенными к системному интерфейсу. На одно из этих устройств возлагаются функции управления обменом, и оно называется активным. Таковым обычно является МП, но это может быть и ИК ПДП. Второе устройство называется пассивным. Таковым всегда является память микроЭВМ.

При этом используется следующий набор управляющих сигналов.

Синхронизация активного устройства (СИА). Источник - активное устройство. Передний фронт этого сигнала указывает, что на МА/МД активным устройством выставлены адрес ВУ или данные. СИА = 1 в течении всего цикла обмена.

Синхронизация пассивного устройства (СИП). Источник - пассивное устройство. Является ответом на сигналы активного устройства ВВОД или ВЫВОД. С помощью этого сигнала активное устройство извещается, что данные приняты с МА/МД при ВЫВОДЕ, или данные установлены пассивным устройством там же при ВВОДЕ.

ВВОД. Источник - активное устройство. Вырабатывается в течении СИА. Означает, что ведется ввод в активное устройство, готовое принять данные.

ВЫВОД. Источник - активное устройство. Это означает, что на МА/МД им выставлены данные. Пассивное устройство принимает данные, в подтверждение чего должно выработать сигнал СИП.

БАЙТ. Источник - активное устройство. Вырабатывается только при ВЫВОДЕ. Активное устройство выводит один байт информации по шинам ДА00...ДА07.

ВУ. Источник - активное устройство. Вырабатывается в том случае, когда на МА/МД установлен адрес, относящийся к старшим 4К адресов (с 160000 В по 177776 В), т.е. к тому адресному пространству, что соответствует регистрам ВУ. Введение этого сигнала позволяет сократить затраты оборудования в ИК на селекцию адресов, передаваемые по МА/МД.

Эти шесть сигналов обеспечивают в рамках Q-Bus реализацию асинхронного программно-управляемого обмена данными с ВУ.

Сигналы для обмена по прерыванию и в режиме МДП сведены в табл.4.2.

Т а б л и ц а 4.2

Сигналы Q-Bus, управляющие режимами обмена с ВУ

| Обозна-чение | Значение | Источник | Назначение |

| ТПТ | Требование прерывания | ВУ | Информирует МП о том, что ВУ готово к обмену данными. Вызывает прерывание программы после выполнения очередной команды |

| ППР | Предоставление прерывания | МП | Извещает ВУ, что прерывание разрешено. Линия ППР проходит последовательно через все ВУ, обеспечивая приоритетное обслуживание запросов на прерывание |

| ТПД | Требование прямого доступа к памяти | ВУ | Информирует МП о том, что ВУ требует ПДП |

| ППД | Предоставление прямого доступа | МП | Разрешение для ВУ на обмен в режиме ПДП. МП приостанавливает выполнение команды после завершения текущего цикла обмена. Линия ППД проходит через ВУ аналогично линиям ППР |

Продолжение табл. 4.2

|  |  |

| Обозначение | Значение | Источник | Назначение |

ПВ

ПВ

| Подтверждение выбора | ВУ | Вырабатывается в ответ на сигнал ППД и подтверждает, что ВУ ведёт обмен в режиме ПДП |

| ПРТ | Требование прерывания по внешнему событию | Аппаратный таймер, ВУ | Обычно используется для передачи в МП сигналов аппаратного таймера. Более приоритетен, чем ТПР |

Контроллеры внешних устройств

Структурная и функциональная организация контроллеров ВУ (ИК) в основном определяется:

* форматами данных и режимами работы конкретных ВУ;

* типом системного интерфейса микроЭВМ.

Влияние первого факта очевидно - нерационально было бы создавать ИК универсального типа, обеспечивающего подключение таких разных ВУ, как например, цифровых индикаторов и НГМД.

Наиболее перспективным оказался путь стандартизации набора информационых и управляющих сигналов, которыми обмениваются ИК и ВУ. Были разработаны ИК, обеспечивающие:

* связь с ВУ по стандартному параллельному (ИРПР) каналу передачи данных (ПД);

* связь с ВУ по стандартному последовательному (ИРПС) каналу ПД;

* преобразование “аналог - код” с заданной точностью;

* преобразование “код - аналог” в заданном диапазоне изменения аналоговых величин.

Второй фактор влияет в основном на сложность схем распознавания алресов ВУ. Наиболее просты схемы в случае микроЭВМ с отдельным интерфейсом ввода/вывода (рис.4.4). Более сложны упоминавшиеся ранее схемы распознавания адресов и разделения адресов и данных, передаваемых по единым шинам.

Расмотрим блок-схему типичного ИК, обеспечивающего программно-управляемый обмен с ВУ с помощью операций ВВОД и ВЫВОД, временные диаграммы которых приведены на рис.4.1 и 4.2.

МА Про- МА ввод/вывод

МА Про- МА ввод/вывод

К памяти МД цессор МД ввод/вывод

К памяти МД цессор МД ввод/вывод

МУ МУ ввод/вывод

МУ МУ ввод/вывод

Рис.4.4 Отдельный интерфейс ввода-вывода

Основу ИК ВУ составляют несколько регистров. Каждый регистр имеет свой адрес, и нередко их называют портами ввода/вывода (рис.4.5).

или МА/МД при мультиплексировании

или МА/МД при мультиплексировании

Приемо- ВУ-состояние Регистры

Приемо- ВУ-состояние Регистры

|

датчики или входные Связь

датчики или входные Связь

|

данных с ВУ

данных с ВУ

|

|

“Ввод” данные

Системный

интерфейс “Вывод” Управ-

интерфейс “Вывод” Управ-

ление 0

ление 0

“Готов- Управление обменом

“Готов- Управление обменом

ностьВУ” с регистрами ИК

ностьВУ” с регистрами ИК

|  |

Прием-

МА ники

МА ники

шин

шин

адреса

адреса

|

При мультиплексировании МА/МД

отсутствует

Рис.4.5. Блок-схема контроллера ВУ

Регистры входных/выходных данных работают (доступны) соответственно только в режиме чтения и только в режиме записи.

Регистр состояния работает только в режиме чтения и содержит информацию о текущем состоянии ВУ: включено/выключено, готово/не готово к обмену данными и т.п.

Регистр управления работает только в режиме записи и служит для приёма из микроЭВМ приказов для ВУ.

В ИК для простых ВУ (клавиатура, перфоратор) удается обычно совместить в один регистр регистры состояния/управления, что позволяет сократить количество портов ИК, т.е. количество адресов для данного ВУ.

Логика управления ИК ВУ выполняет селекцию портов, а также приём, обработку и формирование управляющих сигналов.

Приёмопередатчики служат для физического подключения электронных схем ИК к соответствующим магистралям.

В настоящее время в практику широко внедряются программируемые контроллеры ВУ. Настройка таких ИК на требуемый режим прооизводится программным путём с помощью специальных команд (управляющих слов), передаваемых из процессора в ИК перед началом обмена.

Примеры режимов обмена: синхронный или асинхронный, с использованием сигналов прерывания или без них, с настройкой на заданную скорость обмена и т. д.

Сложные программные контроллеры, например для НГМД, имеют хранимые в ПЗУ или ППЗУ программы управления и обмена с ВУ. Такие ИК есть, по сути, специализированные микроЭВМ. Их настройка на взаимодействие с конкретным ВУ осуществляется сменой программы, т.е. заменой БИС ПЗУ или ППЗУ.

В современных микроЭВМ зачастую трудно провести границу между интерфейсом ввода/вывода и ИК ВУ. Иногда это проявляется даже в смешении самих терминов.

Нередко ИК конструктивно реализуется на плате процессора либо непосредственно в ВУ. Это создаёт у пользователя иллюзию отсутствия ИК и несогласованности в структурных и функциональных схемах микроЭВМ.

Тем не менее в любой микроЭВМ всегда можно достаточно чётко выделить компоненты системы ввода/вывода, что необходимо как при изучении микроЭВМ, так и при их использовании в различных системах.

Параллельная передача данных. Простой контроллер

параллельного вывода

Здесь в шине связи с ВУ используется всего два управляющих сигнала “Данные приняты” и “Выходные данные готовы”.

С этими сигналами в ИК используется одноразрядный адресуемый регистр состояния и управления А2 (рис.4.6.)

Регистр данных А1

МД Приёмо- 0

2015-04-20

2015-04-20 3276

3276