В классификации по первому признаку (рис. 1) ПЛИС разделены на 4 класса.

Рисунок 1. Классификация ПЛИС по архитектуре.

3.4.1 SPLD

Первый из классов — SPLD, Simple Programmable Logic Devices, т. е. простые программируемые логические устройства. По архитектуре эти ПЛИС делятся на подклассы программируемых логических матриц ПЛМ (PLA, Programmable Logic Arrays) и программируемой матричной логики ПМЛ (PAL, Programmable Arrays Logic, или GAL, Generic Array Logic).

Оба эти подкласса микросхем реализуют дизъюнктивные нормальные формы (ДНФ) переключательных функций, а их основными блоками являются две матрицы: матрица элементов И и матрица элементов ИЛИ, включенные последовательно. Такова структурная модель ПЛМ и ПМЛ. Технически они могут быть выполнены и как последовательность двух матриц элементов ИЛИ-НЕ, но варианты с последовательностью матриц И-ИЛИ и с последовательностью матриц ИЛИ-НЕ — ИЛИ-НЕ функционально эквивалентны, т. к. второй вариант согласно правилу де Моргана тоже реализует ДНФ, но для инверсных значений переменных.

Заметим, что термин "матрица" обозначает в данном случае не более чем "набор", "множество" и обусловлен тем, что схемные элементы ПЛМ и ПМЛ удобнее всего располагать по строкам и столбцам, обеспечивая тем самым регулярность структуры БИС.

На входы матрицы И поступают m входных переменных в виде как прямых, так и инверсных значений, так что матрица имеет 2т входных линий. На ее выходах формируются конъюнктивные термы, ранг которых не выше т. В дальнейшем для краткости конъюнктивные термы называются просто термами. Число термов не имеет прямой связи с величиной т и определяется конструктивными параметрами матрицы — числом конъюнкторов. Матрица И идентична для обоих подклассов SPLD, т. е. для ПЛМ и ПМЛ.

Выработанные термы поступают на вход матрицы ИЛИ. Эти матрицы для ПЛМ и ПМЛ различны. В ПЛМ матрица ИЛИ программируется, а в ПМЛ она фиксирована.

Программируемая матрица ИЛИ микросхем ПЛМ составлена из дизъюнкторов. На входы каждого дизъюнктора при программировании можно подать любую комбинацию имеющихся термов, причем термы можно использовать многократно (т. е. один и тот же терм может быть использован для подачи на входы нескольких дизъюнкторов).

В ПМЛ выработанные матрицей И термы поступают на фиксированную (непрограммируемую) матрицу элементов ИЛИ. Это означает жесткое заранее заданное распределение имеющихся термов между отдельными дизъюнкторами. Каждому дизъюнктору придаются свои собственные термы, и если для разных дизъюнкторов окажутся нужными одинаковые термы, придется вырабатывать их в матрице И несколько раз. Однако при этом программируемость матрицы ИЛИ исключается, что для многих задач в итоге существенно упрощает схему ПМЛ в сравнении со схемой ПЛМ.

ПЛМ обладают большей функциональной гибкостью, все воспроизводимые ими функции могут быть комбинациями любого числа термов, формируемых матрицей И. Это полезно при реализации систем переключательных функций, имеющих большие взаимные пересечения по термам. Такие системы свойственны, например, задачам формирования сигналов управления машинными циклами процессоров. Для широко распространенных в практике задач построения "произвольной логики" большое пересечение функций по термам не типично. Для них программируемость матрицы ИЛИ используется мало и становится излишней роскошью, неоправданно усложняющей микросхему. Поэтому ПМЛ распространены больше, чем ПЛМ, и к их числу относится большинство SPLD.

Структуры ПМЛ полнее освещены ниже при описании CPLD, составными частями которых они служат.

3.4.2 CPLD

В сложных программируемых логических схемах CPLD (Complex Programmable Logic Devices) несколько блоков, подобных ПМЛ, объединяются средствами программируемой коммутационной матрицы. В CPLD могут входить сотни блоков и десятки тысяч эквивалентных вентилей. Архитектуры CPLD разрабатываются фирмами Altera, Atmel, Lattice Semiconductor, Cypress Semiconductor, Xilinx и др. Воздействуя на программируемые соединения коммутационной матрицы и ПМЛ, входящих в состав CPLD, можно реализовать требуемую схему.

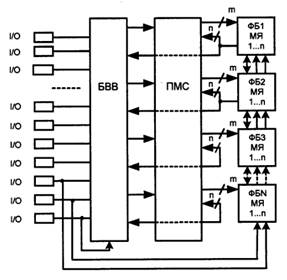

Все составные части CPLD программируются. Обобщенная структура CPLD показана на рис. 2.

Рисунок 2. Структура CPLD

БВВ – блок ввода/вывода; ПМС – программируемая матрица соединений; ФБ – функциональный блок; МЯ – макроячейка.

В структурной схеме приняты следующие обозначения. Через ФБ (FB) обозначены функциональные блоки, число которых N зависит от уровня интеграции микросхемы и изменяется в довольно широких пределах. В каждом ФБ имеется п макроячеек МЯ (МС, Macrocells). Функциональные блоки получают входные сигналы от программируемой матрицы соединений ПМС (PIA, Programmable Interconnect Array). Число таких сигналов m. Выходные сигналы ФБ поступают как в ПМС, так и в блоки ввода/вывода CPLD (IOBs, Input/Output Blocks, БВВ). ПМС обеспечивает полную коммутируемость функциональных блоков, т. е. возможность подавать сигналы с любого их выхода на любой вход.

Блоки ввода/вывода связаны с внешними двунаправленными выводами I/O, которые, в зависимости от программирования, могут быть использованы как входы или как выходы.

Число контактов ввода/вывода может совпадать с числом выходов всех ФБ, но может быть и меньшим. В последнем случае часть макроячеек может быть использована только для выработки внутренних сигналов устройства (в частности, сигналов обратной связи). Необходимость в таких сигналах типична для структур большинства цифровых устройств.

Структура на рис. 2 несколько упрощена. Кроме показанных блоков в CPLD могут присутствовать контроллеры для управления операциями программирования непосредственно в системе (In System Programmability, ISP), контроллеры для работы с интерфейсом JTAG и др.

3.4.3 FPGA

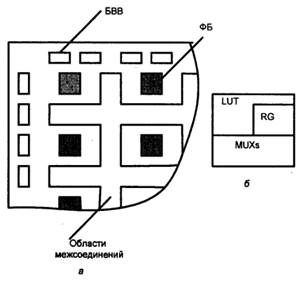

Микросхемы программируемых пользователями вентильных матриц FPGA (Field Programmable Gate Arrays) в своей основе состоят из большого числа конфигурируемых логических блоков (функциональных блоков, ФБ), расположенных по строкам и столбцам в виде матрицы, и трассировочных ресурсов, обеспечивающих их межсоединения, а в периферийной области - блоки ввода/вывода (рис. 3, а). В архитектуре FPGA явно прослеживается большое сходство с архитектурой БМК. Разница в том, что FPGA, поступающая в распоряжение потребителя, имеет уже готовые, стандартные, хотя и не запрограммированные, трассировочные ресурсы, не зависящие от конкретного потребителя. Получение конкретного проекта на базе FPGA, как и на основе других ПЛИС, реализуется воздействием на программируемые межсоединения, в ходе которого обеспечивается замкнутое состояние одних участков и разомкнутое — других. Обращаться к изготовителю FPGA при этом не требуется.

Рисунок 3. Структура FPGA

БВВ – блок ввода/вывода; ФБ – функциональный блок; LUT – таблица поиска; RG – регистр; MUX – мультиплексор.

Все части FPGA (функциональные блоки ФБ, система межсоединений и блоки ввода/вывода БВВ) являются конфигурируемыми или реконфигурируемыми.

Перечисленные части — основа FPGA. Кроме них современные варианты FPGA, как правило, оснащены дополнительными средствами для автоподстройки задержек в системе тактирования (PLL, Phase Locked Loop или DLL, Delay Locked Loop), средствами поддержки интерфейса JTAG и др.

При конфигурировании FPGA функциональные блоки настраиваются на выполнение необходимых операций преобразования данных, а система межсоединений — на требуемые связи между функциональными блоками. В результате во внутренней области FPGA реализуется схема нужной конфигурации. Расположенные по краям кристалла блоки ввода/вывода обеспечивают интерфейс FPGA с внешней средой. Блоки ввода/вывода современных FPGA можно программировать на выполнение требований множества стандартов передачи данных (число таких стандартов может доходить до 20).

На рис. 3, б укрупненно показан состав типичного функционального блока ФБ, в который входят функциональный преобразователь ФП, реализованный в виде программируемого запоминающего устройства (LUT, Look-Up Table), триггер (регистр) и мультиплексоры, играющие роль средств конфигурирования ФБ.

Архитектуры FPGA разрабатываются фирмами Xilinx, Actel, Altera, Atmel, Agere Systems (ранее Lucent Technologies), QuickLogic и др.

3.4.4 ПЛИС с комбинированной архитектурой

В течение первых лет развития ПЛИС они были представлены архитектурами CPLD и FPGA в "чистом" виде. Каждая из этих архитектур имеет свои достоинства и недостатки. Стремление к сочетанию достоинств CPLD и FPGA и рост уровня интеграции БИС/СБИС привели к появлению ПЛИС с комбинированной архитектурой. Класс ПЛИС с комбинированной архитектурой не имеет таких четких границ, как классы CPLD и FPGA, отличается большим разнообразием вариантов и различной степенью близости к тому или иному классическому типу ПЛИС. Не имеет он и общепринятого названия. Тем не менее, представляется целесообразным рассматривать ПЛИС с комбинированной архитектурой как отдельный класс, поскольку принадлежащие к нему схемы трудно квалифицировать как FPGA или CPLD, что подтверждается и разнобоем в названиях, используемых для таких схем различными фирмами. Примером первых ПЛИС с комбинированной архитектурой могут служить микросхемы семейств FLEX8000 и FLEX10K фирмы Altera (FLEX, Flexible Logic Element matriX).

Фактическое существование ПЛИС с комбинированной архитектурой и отсутствие для них общепринятого обобщающего названия вносят ощутимые неудобства в процесс составления классификации ПЛИС. Зачастую ПЛИС с комбинированной архитектурой представляются производителем под каким-либо конкретным именем, в котором не упоминаются ни CPLD, ни FPGA. Таких имен много, и на их основе не провести какую-либо классификацию. Поэтому ниже наряду с узким применяется и широкое толкование термина FPGA. При этом выделяются "классические" FPGA с их канонической архитектурой, а ПЛИС комбинированной архитектуры при необходимости (главным образом, при описании справочных данных) относятся к FPGA в широком смысле этого понятия. Обоснованием такого подхода служит то, что в комбинированных архитектурах черты FPGA обычно проявляются более выраженно, чем черты CPLD. Правда, такой подход заставляет применять к некоторым схемам термины, которые самими производителями не используются (это относится, в частности, к фирме Altera, которая никогда не пользуется термином FPGA). Следует заметить, что авторы, не связанные с фирмой Altera, этого правила придерживаются не всегда и называют некоторые микросхемы данной фирмы термином FPGA. Сказанное выше отображается на рисунке 1 объединением классических FPGA и ПЛИС с комбинированными архитектурами общим прямоугольником из штриховых линий.

На рис. 4 приведена структура микросхем семейства FLEX.

Рисунок 4. Структура микросхем семейства FLEX

LAB – функциональный блок; LE – логический элемент; ВБП – встроенный блок памяти.

Микросхемы семейства FLEX имеют функциональные блоки (LABs, Logic Array Blocks) с логическими элементами ЛЭ (LEs, Logic Elements), содержащими функциональные преобразователи ФП табличного типа (LUTs). Функциональные блоки расположены в виде матрицы, между их строками и столбцами проходят горизонтальные и вертикальные трассировочные каналы, что характерно для FPGA. В то же время, трассы в каналах не сегментированы, а непрерывны, что типично для CPLD. Поскольку в схемах с большим числом функциональных блоков применение единой коммутационной матрицы затруднено, система коммутации имеет два уровня межсоединений — глобальный и локальный. Локальная программируемая матрица соединений (локальная ПМС или ЛПМС) обеспечивает межсоединения логических элементов ЛЭ, из которых составляются функциональные блоки LABs. В состав LAB входят 8 логических элементов. Соединения между блоками LAB обеспечиваются глобальной программируемой матрицей соединений ГПМС, к концам строк и столбцов которой подключаются блоки ввода/вывода (IOBs, Input/Output Blocks).

Начиная с семейства FLEX10K, в составе многих микросхем ПЛИС появились встроенные блоки памяти ВБП (EABs, Embedded Array Blocks). Ранее имелась возможность использования в качестве субмодулей памяти лишь тех ресурсов, которые имеются в ФП типа LUT.

В схеме на рис. 4 показан включенный в середине строк встроенный блок памяти (у большинства микросхем семейства FLEX10K его емкость равна 2048 бит). Такой блок может конфигурироваться как ЗУ с организацией 256x8, или 512x4, или.1024x2, или 2048x1 и использоваться не только для хранения данных, но и как табличный ФП для реализации сложных функций с числом аргументов 8—10 (в частности, на блоках ЕАВ строятся быстродействующие арифметико-логические устройства АЛУ, перемножители 4x4 и т. д.).

Блоки встроенной памяти ориентированы также на организацию буферов FIFO, а в микросхемах FLEX10KE и на построение двухпортовой памяти. Несколько блоков можно объединять для создания более емкой памяти. Так как блоки памяти расположены на том же кристалле, что и логическая часть схемы, работа с памятью отличается высоким быстродействием.

3.4.5 SOPC

Термин SOPC (System On Programmable Chip), т. е. "система на программируемом кристалле" относится к ПЛИС наибольшего уровня интеграции, содержащим сотни тысяч или даже миллионы эквивалентных вентилей. Такой высокий уровень интеграции достигается только с помощью самых современных технологических процессов (малые топологические нормы проектирования, многослойность систем металлизации и т. д.). На основе прогрессивных технологических процессов обеспечивается одновременно высокий уровень интеграции и высокое быстродействие БИС/СБИС. В результате становится возможной интеграция на одном кристалле целой высокопроизводительной системы.

Микросхемы семейств АРЕХ20К/КЕ принадлежат к первым промышленным SOPC с конфигурируемостью всех областей кристалла. Память конфигурации — статическая (триггерная). Микросхемы АРЕХ20К имеют напряжение питания ядра 2,5 В и уровни сигналов ввода/вывода 2,5; 3,3 и 5,0 В, а микросхемы АРЕХ20КЕ напряжение питания ядра 1,8 В, а уровни сигналов ввода/вывода 1,8; 2,5; 3,3 и 5,0 В.

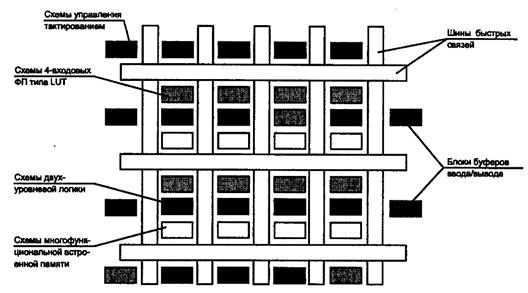

Общий план микросхем показан на рисунке 5. Архитектура микросхем называется Multicore, в ней сочетаются функциональные блоки типов LUT и PAL. Кроме того, микросхемы имеют встроенные блоки памяти ESB (Embedded System Blocks), содержащие также средства для реализации ДНФ логических функций (что и объясняет термин "системные" в названии блоков).

Рисунок 5. Общий план кристалла микросхем семейства APEX20K/KE.

2015-05-10

2015-05-10 3394

3394