Отчет к лабораторной работе № 6

Исследование регистров.

Выполнил: Богомазов А. Е.

Группа: МИ-09

Цель работы: знакомство с работой параллельных и последовательных

регистров.

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств.

Программа 6.1

( последовательный регистр на 8 разрядов)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity regsdv is

port(clk,d_in:in std_logic;

d_out:out std_logic);

end regsdv;

architecture bb of regsdv is

signal shift: std_logic_vector (6 downto 0);

begin

process (clk)

variable i: integer range 7 downto 0;

begin

if(rising_edge(clk)) then

shift(0)<=d_in;

for i in 1 to 6 loop

shift(i)<=shift(i-1);

end loop;

d_out<=shift(6);

end if;

end process;

end bb;

Программа 6.2

( последовательно-параллельный регистр на 8 разрядов. )

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity regsdv1 is

port(clk,d_in:in std_logic;

d_out:out std_logic_vector (7 downto 0));

end regsdv1;

architecture bb of regsdv1 issignal shift: std_logic_vector (7 downto 0);

begin

process (clk)

variable i: integer range 7 downto 0;

begin

shift(0)<=d_in;

if(rising_edge(clk)) then

for i in 1 to 7 loop

shift(i)<=shift(i-1);

end loop;

d_out<=shift;

end if;

end process;

end bb;

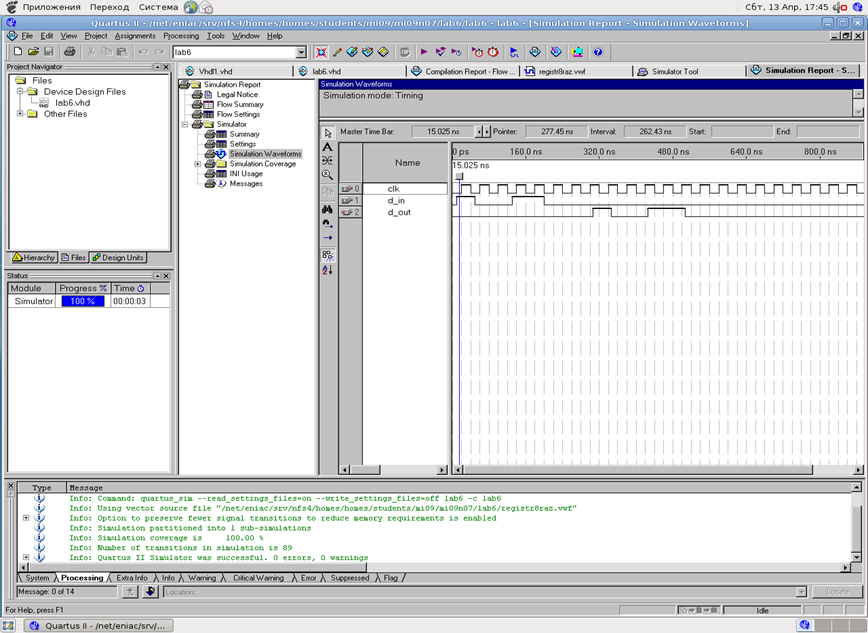

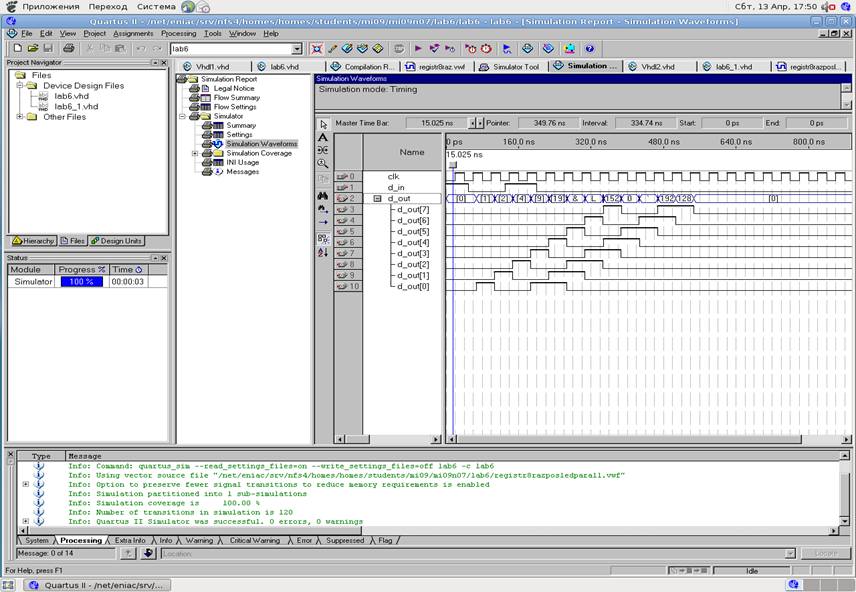

Временные диаграммы работы устройств:

1 Последовательный регистр на 8 разрядов

2. Последовательно-параллельный регистр на 8 разрядов.

2015-05-10

2015-05-10 321

321