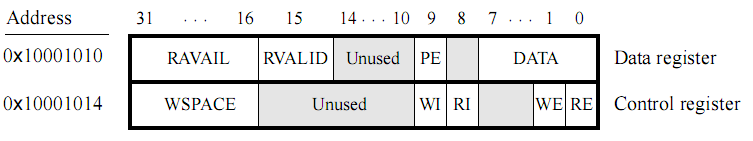

Последовательный порт в процессорной системе включает UART, который соединен с соответствующей микросхемой RS232 на плате. Этот UART конфигурируется для передачи восьми битов данных, одного стопового бита, бита нечетности. Он работает со скоростью 115200 бит в секунду. Программный интерфейс последовательного порта состоит из двух 32-битных регистров, показанных на рис. 3.11. Регистр, доступный по адресу 0x10001010, является регистром данных. Регистр, доступный по адресу 0x10001014, является регистром управления.

Рис. 3.11 – Регистры UART последовательного порта

Когда символьные данные пересылаются в процессорную систему через разъем RS232, они сохраняются в 128-символьном буфере FIFO. Как показано на рис. 3.11, число символов RAVAIL, хранимых в текущий момент времени в этом FIFO, представлено в битах 31-16 регистра данных. Если буфер FIFO получаемых данных полный, то дополнительные данные, переданные в процессорную систему, будут потеряны. Когда данные присутствуют в буфере FIFO получаемых данных, то величина бита 15 регистра данных (RVALID) будет равна 1.

Чтобы осуществить чтение символа из вершины буфера FIFO, необходимо прочитать содержимое регистра данных порта UART. При этом младшие разряды 7-0 регистра данных будут содержать вводимый символ. Поле RAVAIL при выполнении чтения автоматически уменьшится на единицу, и это уменьшенное значение как раз и будет получено в результате чтения. Если данных в принимаемом буфере FIFO нет, то поле RVALID будет содержать нулевое значение, и результат чтения из разрядов 7-0 регистра данных UART будет не определен.

Последовательный порт так же включает 128-символьный буфер FIFO, который хранит данные, ожидающие отправки в RS232. Символьные данные загружаются в этот буфер посредством записи в биты 7-0 регистра данных. Запись в регистр данных не оказывает никакого влияния на получаемые данные. Размер доступного пространства в текущий момент времени в заполняемом буфере FIFO указывается в разрядах 31-16 регистра управления. Это поле WSPACE (см. рис. 3.11). Если буфер FIFO заполнен, то все данные, в последующем записываемые в регистр данных, будут потеряны.

Биты регистра управления RE, WE, WI, RI обсуждаются в разделе 3.3.3.

2015-06-04

2015-06-04 340

340