Этот тип АЦП относят к комбинированным, т. к. принципы его функционирования сводятся к созданию мнгоразрядного преобразователя с использованием малоразрядных БИС АЦП, т. е. в конечном итоге – с использованием простой и распространенной элементной базы.

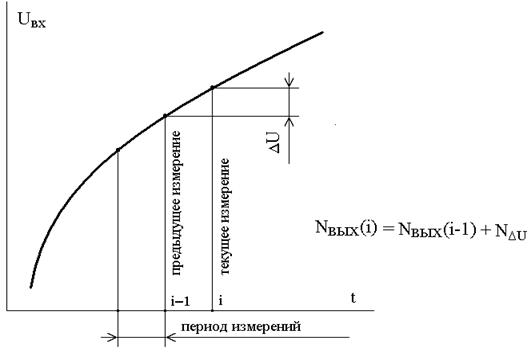

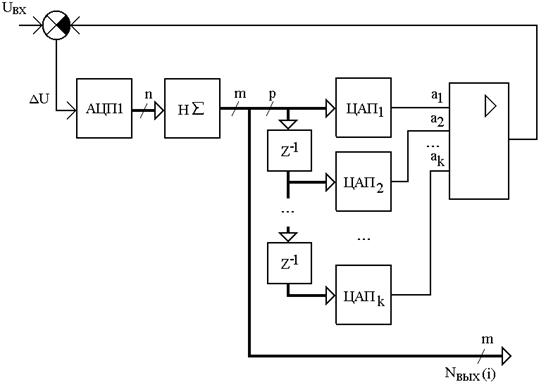

По организации работы такие преобразователи напоминают АЦП последовательных приближений с реверсивным счетчиком, т. к. и те и другие работают в соответствии со следящим алгоритмом. Следящий принцип работы АЦП предполагает проведение оценки приращения входного напряжения ΔU (рис.) между моментом начала текущего цикла кодирования и моментом начала предыдущего цикла (т. е. оценки того, насколько изменилось входное напряжение Uвх за время прошедшее с предыдущего измерения). При этом выходной код Nвых(i) в процессе текущего преобразования формируется как сумма выходного кода Nвых(i–1), полученного в предыдущем измерении, и кода NΔU, соответствующего приращению входного напряжения ΔU.

Р и с. Формирование выходного кода в следящих АЦП многоразрядных приращений

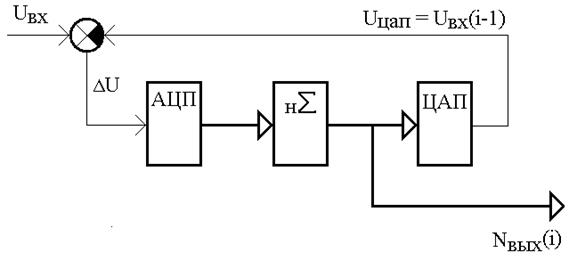

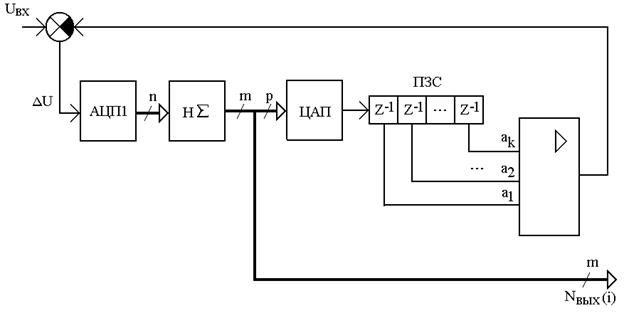

В отличие от АЦП с реверсивным счетчиком приращение входного напряжения ΔU в рассматриваемых преобразователях кодируется за один такт с помощью n - разрядной БИС АЦП. Такая форма получения выходного кода определила название рассматриваемых устройств – следящие АЦП многоразрядных приращений. Их обобщенная структура представлена на рис..

Р и с. Структура следящего АЦП многоразрядных приращений

Для формирования приращения ΔU необходимо на один вход вычитателя подать текущее значение входного напряжения Uвх, а на другой вход надо подать напряжение которое было на входе устройства в момент начала предыдущего цикла кодирования. Это напряжение формируется с помощью ЦАП, на который подается выходной код устройства Nвых(i–1), который был получен на предыдущем цикле кодирования.

Приращение сигнала ΔU с выхода вычитателя подается на вход БИС АЦП. Цифровая оценка приращения ΔU с выхода БИС АЦП суммируется со значением выходного кода Nвых(i–1), полученного на предыдущем цикле преобразования. Т. к входное напряжение Uвх могло за время прошедшее с предыдущего цикла кодирования как увеличиться, так и уменьшиться, то приращение ΔU может быть как положительным, так и отрицательным. Поэтому сложение кода приращения NΔU с предыдущем значением кода преобразователя Nвых(i–1) в сумматоре должно осуществляться с учетом знака приращения ΔU. Полученный код на выходе сумматора Nвых(i) при этом будет соответствовать текущему значению входного напряжения Uвх.

Величина приращения ΔU между соседними циклами кодирования будет зависеть от скорости изменения входного напряжения Uвх. При этом разрядность n БИС АЦП должна быть выбрана так, чтобы сумма весов ее разрядов перекрывала максимально возможную величину ΔU. Т. к. сумма весов всех m разрядов выходного кода устройства NВЫХ равна диапазону Uвх, а сумма весов n разрядов, формируемых БИС АЦП, равна UВХ МАХ / 2m–n, то выполнение указанного условия должно сводиться к выполнению нестрого неравенства UВХ МАХ / 2m–n ≥ ΔUМАХ. Разрядность БИС АЦП должна быть взята минимальному значению n, при котором это условие будет выполняться. Так, разрядность БИС АЦП определяется исходя из максимальной скорости изменения входного напряжения UВХ. Конечно предполагается, что поведение входного сигнала должно быть известно перед началом работ по проектированию устройства.

Каждая БИС АЦП имеет свой диапазон входных напряжений UБИС АЦП MАХ. Для приведения суммы весов n младших разрядов выходного кода к диапазону конкретной БИС АЦП между вычитателем и БИС АЦП необходим усилитель, имеющий коэффициент усиления равный UБИС АЦП MАХ / (UВХ МАХ /2m–n).

Очевидно, что такую структуру рационально применять тогда, когда изменения входного сигнала ΔU между циклами измерения небольшие. При кодировании небольших по величине приращений ΔU разрядность n БИС АЦП тоже будет небольшой, причем при этом она может быть существенно меньше разрядности m выходного кода устройства.

Проанализируем некоторые особенности функционирования рассматриваемых АЦП и вытекающие из них ограничения по их использованию.

После включения АЦП код на выходе сумматора в практических устройствах, будет принимать произвольное значение. При этом перед началом кодирования напряжение на выходе ЦАП может существенно отличаться от текущего значения входного напряжения Uвх и тогда разностный сигнал ΔU на выходе вычитателя будет превышать диапазон работы БИС АЦП. Код на выходе БИС АЦП при этом не будет соответствовать получившемуся разностному сигналу ΔU – он будет принимать свое максимально возможное значение. В такой ситуации правильного значения выходного кода на текущем цикле кодирования получено не будет. Более того, такая ситуация может продолжаться несколько циклов кодирования. Но при этом в каждом таком цикле кодирования код БИС АЦП будет накапливаться в сумматоре и код на выходе устройства будет приближаться к нужному значению. В конце концов, после очередного измерения разностный сигнал ΔU на выходе вычитателя войдет в допустимый диапазон работы БИС АЦП. При этом в текущем и во всех последующих циклах кодирования результат на выходе АЦП будет правильный. Таким образом, при включении АЦП он несколько циклов кодирования может «входить» в установившийся следящий режим работы. Насколько это допустимо должно рассматриваться в каждом конкретном случае применения таких АЦП.

Отметим, что рассматриваемые АЦП в отличие от следящих АЦП с реверсивным счетчиком в установившемся режиме имеют фиксированное время преобразования.

Следящий алгоритм работы АЦП многоразрядных приращений исключает их применение в многоканальных измерительных системах, в которых сигналы, поступающие с различных датчиков, коммутируются на один АЦП и последовательно кодируются один за другим.

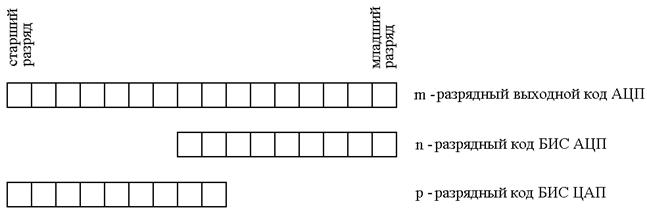

При подробном рассмотрении принципа работы следящих АЦП многоразрядных приращений становится ясно, что в их структурах на ЦАП можно подавать не все разряды выходного кода, а только часть старших. Если при этом кодировать не меняющееся по величине входное напряжение, то максимальный разностный сигнал на выходе вычитателя будет равен сумме весов младших отброшенных разрядов. Если входной сигнал от измерения к измерению будет меняться, то разностный сигнал будет складываться из двух составляющих – напряжения, равного сумме весов отброшенных разрядов, и напряжения, соответствующего изменению входного сигнала с момента предшествующего кодирования. Разрядность БИС АЦП должна выбираться так, чтобы сумма весов ее разрядов в любом случае покрывала максимально возможное значение сигнала на выходе вычитателя. В данном случае это условие будет выполняться, если шкала разрядов БИС АЦП и шкала разрядов БИС ЦАП будут перекрываться (рис.3). Можно условно считать, что при этом сумма весов не перекрывающихся разрядов БИС АЦП будет «уходить» на кодирование разностного сигнала, получаемого из-за того что на ЦАП подаются не все разряды выходного кода, а сумма весов перекрывающихся разрядов – на кодирование динамических изменений входного напряжения. Для правильного получения кода на выходе АЦП при такой его структурной организации нужно перед началом каждого кодирования в накапливающем сумматоре обнулять разряды, не подаваемые на БИС ЦАП.

Р и с. 3. Распределение разрядов БИС АЦП и БИС ЦАП в разрядной сетке

следящих АЦП многоразрядных приращений

Интересен подход рассмотрения работы таких АЦП, при котором считается, что ЦАП образует цепь предсказания входного сигнала, а при создании этой цепи используется самый простой принцип предсказания, на основании которого предполагается, что входной сигнал в текущем цикле измерения будет такой же, как и при проведении предыдущего кодирования. При этом можно говорить, что разностный сигнал равен ошибке формируется предсказания. В принципе в структуре АЦП могут использоваться и более сложные принципы предсказания. Это отразится во введении в структуру предсказывающих (интерполирующих) звеньев, аналогичных звеньям цифровых фильтров. Структура такого АЦП будет выглядеть так, как это показано на рис.4. Применение такой структуры при построении многоразрядных АЦП позволит, прежде всего, использовать БИС АЦП еще меньшей разрядности. Не трудно показать, что данная структура будет совмещать функции АЦП и цифрового фильтра.

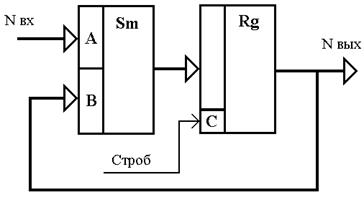

На рис. проиллюстрировано то, как можно реализовать схему накапливающего сумматора. Она включает в себя комбинационный сумматор и регистр с управлением по фронту.

Р и с. Структурная реализация накапливающего сумматора

…

Отметим также, что рассматриваемые АЦП в отличие от следящих АЦП с реверсивным счетчиком в установившемся режиме имеют фиксированное время преобразования.

2015-06-04

2015-06-04 1239

1239