Обработка информации в ЭВМ происходит путем последовательного выполнения элементарных операций. К ним относятся: установка, сдвиг, прием, преобразование, сложение и некоторые другие. Для выполнения каждой из этих операций сконструированы электронные узлы – регистры, счетчики, сумматоры, преобразователи кодов и т.д. Из этих узлов строятся интегральные микросхемы очень высокого уровня: микропроцессоры, модули ОЗУ, контроллеры внешних устройств и т.д. Сами указанные узлы собираются из основных базовых логических элементов – как простейших, реализующих логические функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и им подобных, так и более сложных, таких как триггеры.

Логический элемент компьютера - это часть электронной логической схемы, которая реализует элементарную логическую функцию.

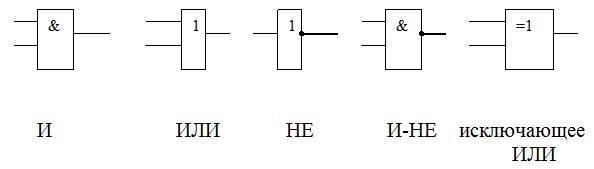

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Введем условные обозначения основных логических элементов.

Данные простейшие логические элементы можно реализовать аппаратно. Это означает, что можно создать электронные устройства на транзисторах, резисторах и т.д., каждое из которых имеет один или два входа для подачи управляющих напряжений и один выход, напряжение на котором определяется соответствующей таблицей истинности. На практике логическому «да» соответствует наличие напряжения, логическому «нет» - его отсутствие.

В качестве характерных устройств выберем два наиболее важных и интересных – триггер и сумматор. Триггер – это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Сумматор - это электронная логическая схема, выполняющая суммирование двоичных чисел.

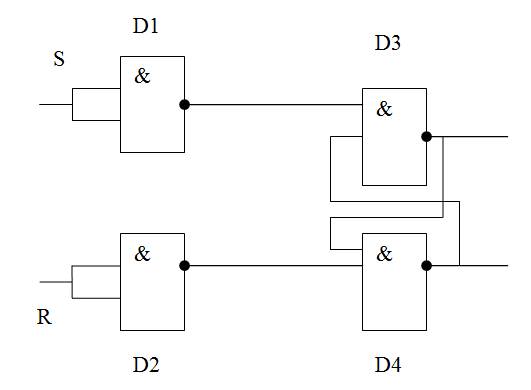

Простейший вариант триггера собирается из четырех логических элементов И-НЕ (рисунок 13). Он имеет два входа R, S и два выхода – прямой и инверсный. Термин триггер происходит от английского слова trigger - защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера - так называемый RS-триггер (S и R, соответственно, от английских set - установка, и reset -сброс).

Логическая схема триггера

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы И-НЕ.

1. Пусть на входе R установлена 1, а на входе S – 0. Логические элементы D1 и D2 инвертируют эти сигналы. В результате на вход элемента D3 поступает 1, а на D4 – 0. Поскольку на одном из выходов D4 уже есть 0, независимо от состояния другого входа на его выходе (он же инверсный выход триггера) обязательно установится 1. Эта 1 передается на вход элемента D3 и в сочетании с 1 на другом входе порождает на выходе D3 логический 0. Итак, при R=1 и S=0 на прямом выходе триггера устанавливается 0, а а на инверсном – 1. Обозначение состояния триггера принято связывать с прямым выходом: говорят, что триггер «устанавливается в 0» или «сбрасывается». Отсюда и вход, появление сигнала на котором приводит к сбросу триггера обозначают, R (“reset”).

2. При аналогичных рассуждениях для симметричного случая R=0 и S=1, можно убедиться, что триггер перейдет в единичное состояние – «установится» (“set”).

3. Наиболее распространенная и интересная ситуация, когда R=0 и S=0 – входные сигналы сняты. Состояние выхода будет полностью зависеть от состояния противоположных входов. Такое состояние будет устойчивым: 0 на одном из выходов будет поддерживать 1 на другом. Таким образом, при отсутствии входных сигналов триггер будет сохранять свое «предыдущее» состояние. Это свойство триггера и положено в основу хранения одного бита информации.

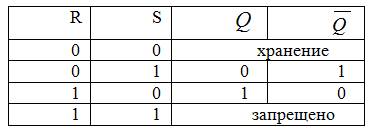

4. Последняя комбинация R=1 и S=1 приводит к тому, что на обоих выходах триггера установиться 1! Такое состояние логически недопустимо и крайне неустойчиво, поскольку снятие входных напряжений приведет к тому, что триггер случайным образом перейдет в одно из своих устойчивых состояний. Такая ситуация на практике является запрещенной. Ниже приведена таблица истинности триггера.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 * 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Таблица истинности RS-триггера

Сумматор - это электронная логическая схема, выполняющая суммирование двоичных чисел.

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

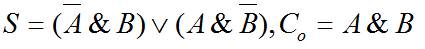

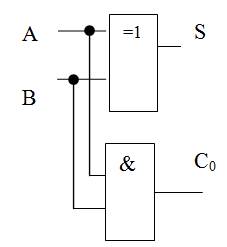

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров. Начнем с изучения логической структуры простейшего возможного устройства, являющегося звеном сумматора – полусумматора, который реализует сложение двух одноразрядных двоичных чисел. В результате получается двухразрядное двоичное число. Его младшую цифру обозначим S, а старшую, которая при сложении многоразрядных чисел будет перенесена в старший разряд, через Co (от английских слов “Carry out” – “выходной перенос”).

Обе цифры можно получить по следующим логическим формулам:

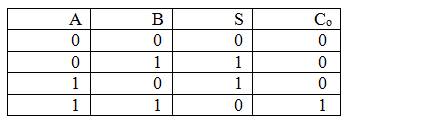

Составим для этих формул таблицу истинности.

Таблица истинности для полусумматора

Таким образом, для реализации полусумматора достаточно соединить параллельно входы двух логических элементов, как это показано на рисунке.

2015-07-14

2015-07-14 8206

8206