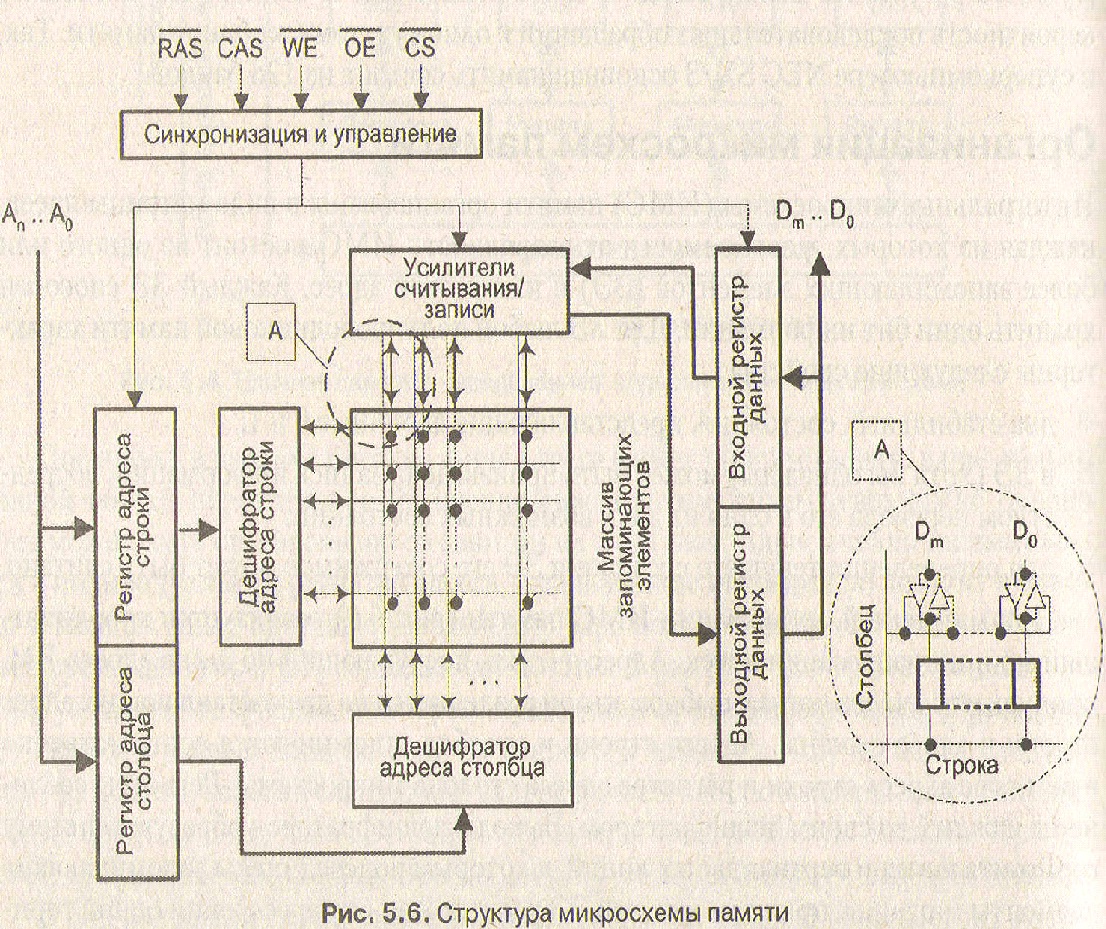

Интегральные микросхемы памяти организованы в виде матрицы ячеек, каждая из которых, в зависимости от разрядности, состоит из одного или более запоминающих элементов (ЗЭ) и имеет свой адрес. Каждый ЗЭ способен хранить один бит информации. При матричной организации ИМС памяти (см. рисунок ниже) реализуется координатный принцип адресации ячеек.

Адрес ячейки, поступающий по шине адреса ЭВМ, пропускается через логику выбора, где он разделяется на две составляющие: адрес строки и адрес столбца. Адреса строки и столбца запоминаются соответственно в регистре адреса строки и регистре адреса столбца микросхемы. Регистры соединяются каждый со своим дешифратором. Выходы дешифраторов образуют систему горизонтальных и вертикальных линий, к которым подсоединены запоминающие элементы матрицы, при этом каждый ЗЭ расположен на пересечении одной горизонтальной и одной вертикальной линии. ЗЭ, объединенные общим горизонтальным проводом, принято называть строкой (row). Запоминающие элементы, подключенные к общему вертикальному проводу, называют столбцом (column). Фактически вертикальных проводов в микросхеме должно быть, по крайней мере, вдвое больше, чем это требуется для адресации, поскольку к каждому ЗЭ необходимо подключить линию, по которой будет передаваться считываемая и записываемая информация. Совокупность запоминающих элементов и логических схем, связанных с выбором строк и столбцов, называют ядром микросхемы памяти. Помимо ядра, в микросхеме имеется еще интерфейсная логика, обеспечивающая взаимодействие ядра с внешним миром. В ее задачи, в частности, входит коммутация нужного столбца на выход при считывании и на вход - при записи. На физическую организацию ядра, как матрицы однобитовых ЗЭ, накладывается логическая организация памяти, под которой понимается разрядность микросхемы, то есть количество линий ввода/вывода. Разрядность микросхемы определяет количество ЗЭ, имеющих один и тот же адрес (такая совокупность запоминающих элементов называется ячейкой), то есть каждый столбец содержит столько разрядов, сколько есть линий ввода/вывода данных. Для уменьшения числа контактов микросхемы адреса строки и столбца в большинстве микросхем подаются через одни и те же контакты последовательно во времени (мультиплексируются) и запоминаются, соответственно, в регистре адреса строки и регистре адреса столбца микросхемы.

Мультиплексирование обычно реализуется внешней логикой. Для синхронизации процессов фиксации и обработки адресной информации адрес строки (RA) сопровождается сигналом RAS (RowAddressStrobe - строб строки), а адрес столбца (СА) - сигналом CAS (ColumnAddressStrobe - строб столбца). Чтобы стробирование было надежным, эти сигналы подаются с задержкой, достаточной для завершения переходных процессов на шине адресаj/I в адресных цепях микросхемы. Сигнал выбора микросхемы CS (CrystalSelect) разрешает работу схемы и используется для выбора определенной микросхемы в системах, состоящих из нескольких микросхем. Вход WE (WriteEnable - разрешение записи) определяет вид выыполняемой операции (считывание или запись). На все время, пока микросхемы памяти не использует шину данных, информационные выходы микросхемы переводятся в третье (высокоимпедансное) состояние. Управление переключением в третье состояние о6еспечивается сигналом ОЕ (OutputEnable - разрешение выдачи выходных сигналов). Этот сигнал активизируется при выполнении операции чтения. На рисунке (см. рисунок ниже) представлено изображение ОЗУ на принципиальных схемах.

2015-08-12

2015-08-12 2850

2850