Схема ускоренного переноса — логический узел ЭВМ, представляющий собой многоразрядный арифметический узел, состоящий из нескольких арифметических узлов меньшей разрядности, вырабатывающих сигналы переноса за меньшее время, чем в одноразрядных сумматорах.

Принцип работы

[Термины:

Lookahead Carry Unit (LCU) - схема ускоренного переноса

Carry Look-ahead Adder (CLA) - схема сумматора с ускоренным переносом

PG - групповой сигнал распространения переноса

GG - групповой сигнал генерации переноса

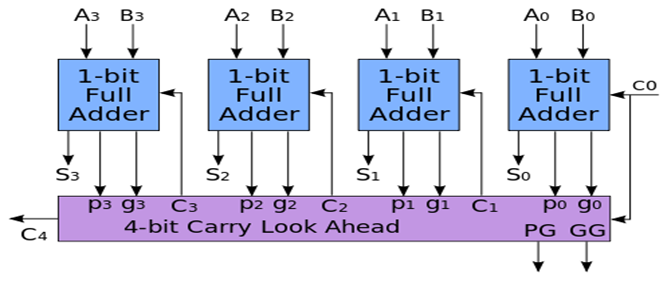

При использовании схемы ускоренного переноса (LCU) каждый одинарный разряд сумматора вырабатывает сигнал генерации переноса (g0) и сигнал распространения переноса (p0).

4-х битная схема

4-битный сумматор со схемой ускоренного переноса

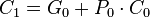

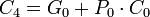

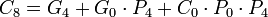

Одинарные разряды сумматора объединяются в группы по четыре одинарных разряда в каждой группе. Схема ускоренного переноса вырабатывает сигналы переноса C1, C2, C3, C4, групповой сигнал генерации переноса (GG) и групповой сигнал распространения переноса (PG).

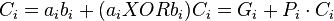

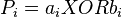

Для переноса в одном разряде:

, где

, где

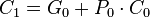

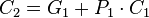

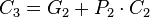

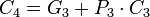

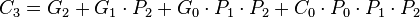

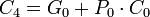

Для переносов в четырёх разрядах:

Подставив  в

в  , затем

, затем  в

в  , затем

, затем  в

в  получим расширенные уравнения:

получим расширенные уравнения:

4-х битная схема ускоренного переноса выпускается в интегральном исполнении: SN74182 (ТТЛ), MC10179 (ЭСЛ) и MC14582, 564ИП4[1] (КМОП).

16-ти битная схема

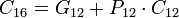

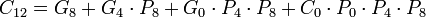

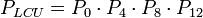

16-разрядный сумматор может быть создан путём объединения четырёх 4-битных сумматоров с четырьмя схемами ускоренного переноса (4-bit CLA Adder), дополненных пятой схемой ускоренного переноса, которая используется для обработки групповых сигналов генерации переноса — GG и распространения переноса — PG.

Принимаемые на входе сигналы распространения переноса ( ) и генерируемые каждой их четырёх схем сигналы (

) и генерируемые каждой их четырёх схем сигналы ( ). Затем, схема ускоренного переноса генерирует соответствующие сигналы.

). Затем, схема ускоренного переноса генерирует соответствующие сигналы.

Предположим, что  это сигналы

это сигналы  и

и  это

это  из iй, то выходные биты устанавливаются следующим образом:

из iй, то выходные биты устанавливаются следующим образом:

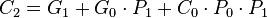

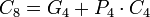

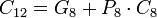

Подставляя  сперва в

сперва в  , затем

, затем  в

в  , затем

, затем  в

в  получаем следующее расширение выражения:

получаем следующее расширение выражения:

соответственно генерирует бит переноса на вход второй схемы;

соответственно генерирует бит переноса на вход второй схемы;  на вход третьей;

на вход третьей;  на вход четвёртой; и

на вход четвёртой; и  генерирует бит переполнения.

генерирует бит переполнения.

Кроме того, можно вычислить сигналы распространения переноса и генерации переноса для схемы ускоренного переноса:

16-разрядный сумматор со схемой ускоренного переноса

64-битная схема]

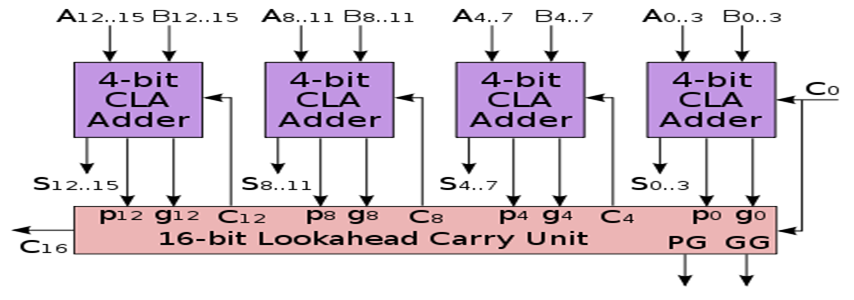

Объединив четыре схемы сумматора и схему ускоренного переноса вместе, получим 16-битный сумматор. Четыре таких блока могут быть объединены в 64-разрядный сумматор. Дополнительные схемы ускоренного переноса (второго уровня) необходимы, чтобы принимать сигналы распространения переноса ( ) и сигналы генерации переноса(

) и сигналы генерации переноса( ) от каждой схемы сумматора.

) от каждой схемы сумматора.

64-разрядный сумматор со схемой ускоренного переноса второго уровня

Достоинства: Высокая скорость работы.

Недостатки: Большие затраты оборудования

Схемы формирования параллельного переноса имеют серьёзное преимущество в скорости перед схемами последовательного переноса.

Тема: Встановлення і налаштування параметрів роботи HDD, дисководів та приводів оптичних носіїв.

Мета: Набути вмінь і навиків при встановленні та налаштуванні параметрів роботи HDD, дисководів та приводів оптичних носіїв.

2015-08-13

2015-08-13 3589

3589