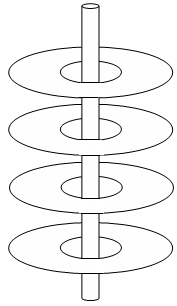

Второй основной составляющей компьютера (после процессора) является память. Система памяти конструируется в виде иерархии слоев (рис. 2.3.1). Верхний слой состоит из внутренних регистров центрального процессора. Внутренние регистры предоставляют возможность для хранения 32 битных данных на 32-разрядном процессоре и 64 битных на 64-разрядном процессоре, что, как правило, составляет меньше одного килобайта. Данные сохраняются в регистрах общего назначения, этот процесс управляется программой.

| Оперативная память |

| Магнитный диск |

| Оптический диск |

| Регистры |

| Кэш |

| Среднее время доступа |

| 1 нс |

| 2 нс |

| 5 нс |

| 10 мс |

| 150 мс |

| Средний объем |

| 1 Кбайт |

| 4 Кбайт |

| 512 Мбайт |

| 256 Гбайт |

Рисунок 2.3.1. Иерархическое представление памяти в компьютере

В следующем слое находится кэш-память (англ. cache), в основном контролируемая оборудованием. Наиболее часто используемые команды хранятся в высокоскоростной кэш-памяти, расположенной внутри центрального процессора или очень близко к нему. Когда программа должна прочитать слово из памяти, кэш-микросхема проверяет, есть ли нужная строка в кэше. Если это так, то происходит результативное обращение к кэш-памяти, запрос удовлетворяется целиком из кэша и запрос к памяти на шину не выставляется. Удачное обращение к кэшу, как правило, по времени занимает около двух тактов, а неудачное приводит к обращению к памяти с существенной потерей времени. Кэш-память ограничена в размере, что обусловлено ее высокой стоимостью. В некоторых машинах есть два или даже три уровня кэша, причем каждый последующий медленнее и больше предыдущего.

Далее следует оперативная память (ОЗУ – оперативное запоминающее устройство, англ. RAM, Random Access Memory – память с произвольным доступом). Это главная рабочая область запоминающего устройства вычислительной системы. Все запросы центрального процессора, которые не могут быть выполнены кэш-памятью, поступают для обработки в основную память.

|

| Головка чтения/записи |

| Направление движения вилки с головками |

| Поверхность 0 |

| Поверхность 1 |

| Поверхность 2 |

| Поверхность 3 |

| Поверхность 5 |

| Поверхность 7 |

| Поверхность 4 |

| Поверхность 6 |

| Рисунок 2.3.2. Устройство жесткого диска |

Следующим в структуре памяти идет магнитный диск (жесткий диск),структурная представление которого показано на рисунке 2.3.2. Дисковая память на два порядка дешевле ОЗУ в пересчете на бит и больше по величине, но доступ к данным, размещенным на диске, занимает примерно на три порядка больше времени. Причиной низкой скорости жесткого диска является тот факт, что диск представляет собой механическую конструкцию. Жесткий диск состоит из одной или нескольких металлических пластин, вращающихся со скоростью 5400, 7200 или 10800 оборотов в минуту. Информация записывается на пластины в виде концентрических окружностей. Головки чтения/записи в каждой заданной позиции могут прочитать кольцо на пластине, называемое дорожкой. Все вместе дорожки для заданной позиции вилки формируют цилиндр. Каждая дорожка разделена на некоторое количество секторов, обычно по 512 байт на сектор. На современных дисках внешние цилиндры содержат большее количество секторов, чем внутренние. Перемещение головки от одного цилиндра к другому занимает около 1 мс, а перемещение к произвольному цилиндру требует от 5 до 10 мс, в зависимости от диска. Когда головка располагается над нужной дорожкой, нужно ждать, пока двигатель повернет диск так, чтобы под головкой стал требуемый сектор. Это занимает дополнительно от 5 до 10 мс, в зависимости от скорости вращения диска. Когда сектор находится под головкой, процесс чтения или записи происходит со скоростью от 5 Мбайт/с (для низкоскоростных дисков) до 160 Мбайт/с (для высокоскоростных дисков).

Кроме описанных выше видов во многих компьютерах есть постоянная память с произвольным доступом (ПЗУ – постоянное запоминающее устройство, ROM, Read Only Memory – память только для чтения), которая не теряет свое содержимое при выключении питания вычислительной системы. ПЗУ программируется в процессе производства и после этого его содержимое нельзя изменить. На некоторых компьютерах в ПЗУ находятся программы начальной загрузки, используемые при запуске компьютера.

Электрически стираемое ПЗУ (EEPROM, Electrically Erasable ROM) и флэш-ОЗУ (flash RAM) также энергонезависимы, но в отличие от ПЗУ их содержимое можно стереть и переписать. Однако запись данных на них требует намного больше времени, чем запись в оперативную память. Поэтому они используются точно так же, как и ПЗУ.

Существует еще один вид памяти – CMOS-память, которая является энергозависимой и используется для хранения текущей даты и текущего времени. Память получает питание от аккумулятора, встроенного в компьютер, может содержать конфигурационные параметры (например, указание, с какого источника производить начальную загрузку операционной системы).

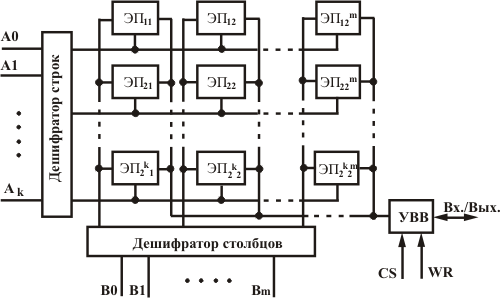

Статическая память, SRAM (англ. Static RAM) – энергозависимая память, обладает очень малым временем доступа, основана на использовании триггеров в качестве запоминающего элемента. Триггер может быть построен из 5-6 транзисторов. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах. Кроме того, статические ОЗУ применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ. Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их емкость относительно невелика, что является их недостатком по сравнению с динамической памятью (см. динамическая память). Структура статического ОЗУ представлена на рисунке 2.3.3, где ЭП – это элемент памяти, а УВВ - устройство ввода-вывода.

Рисунок 2.3.3. – Структура статического ОЗУ

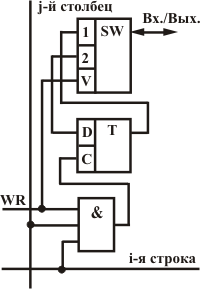

Запоминающие элементы заключены в матрице, размерностью 2n * 2m, где n, m – целые числа. Один элемент памяти может хранить бит информации. Вариант исполнения элемента памяти представлен на рисунке 2.3.4. Запоминающим устройством, на этом рисунке является D-триггер, который находится на пересечении i-ой строки и j-го столбца, которые являются выходами дешифраторов строк и столбцов соответственно. Сигнал WR является управляющим и указывает на вид операции (WR=1 – операция записи, WR = 0 – операция чтения). При записи в триггер записывается информация, которая поступает на вход D через шинный формирователь SW. При чтении информация появляется на выходе шинного формирователя, которая поступает с выхода триггера.

Рисунок 2.3.4. – Элемент памяти статического ОЗУ

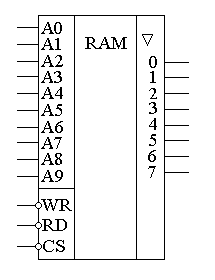

На рисунке 2.3.5 показано условно-графическое изображение ОЗУ. Сигнал записи показан как WR, сигнал чтения – RD. Сигнал CS (chip select – выбор кристалла) активирует схему памяти для использования, т.е. в пассивном состоянии схема памяти находится в режиме хранения информации.

Рисунок 2.3.5. – Условно-графическое изображение ОЗУ

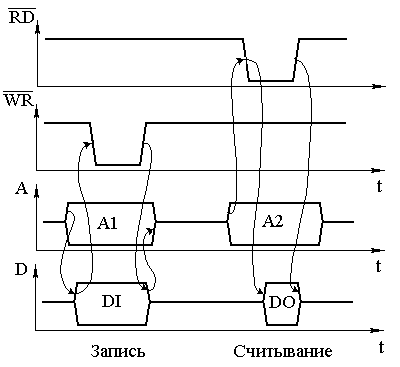

Временные диаграммы чтения и записи приведены на рисунке 2.3.6. На рисунке “а” изображена диаграмма обращения к ОЗУ для схем совместимая со стандартом от компании INTEL, на “б”, со стандартом от компании MOTOROLA.

| б |

| а |

Рисунок 2.3.6 – Временные диаграммы обращения к статической памяти

Стрелочками показаны последовательности, в которых должны формироваться управляющие сигналы. Сигнал DS (data strobe)– сигнал стробирования данных, который является активным в низком состоянии («0»). DI – (data in)- входные (записываемые в память) данные, DO (data out) – выходные (читаемые из памяти) данные.

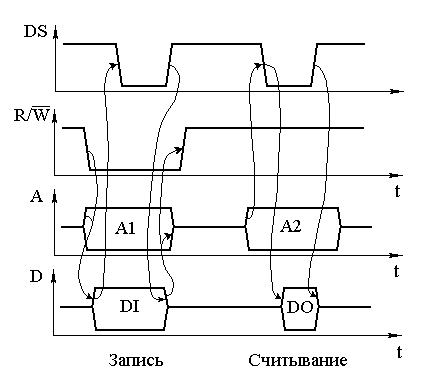

Динамическая память DRAM (англ. Dynamical RAM) в отличие от статической памяти, в динамической запоминающим элементом является конденсатор. Пример реализации запоминающего элемента представлен на рисунке 2.3.7. Запись и считывание информации производится путем открывания транзисторов Т1 и Т2 и подключением накопительной емкости С к шине данных.

Рисунок 2.3.7 – Схема запомниающего элемента динамической памяти.

Так как в конденсаторах присутствуют токи утечки, для долговременной работы динамической памяти необходимо восстановление заряда в накопительной емкости С. Поэтому в устройствах динамического ОЗУ присутствуют схемы регенерации информации, которое требуют дополнительного времени и немного усложняют схему. Схема регенерации состоит из триггерного элемента, который заряжает ячейку, будучи предварительно установленным значением, которое зависит от уровня заряда конденсатора. Однако, несмотря на это, модули динамической памяти более компактны относительно статической памяти (требуется 1-2 транзистора для хранения 1 бита информации), обладают большой емкостью и применяются в качестве основного ОЗУ в вычислительной технике.

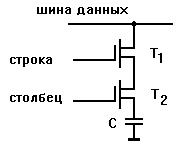

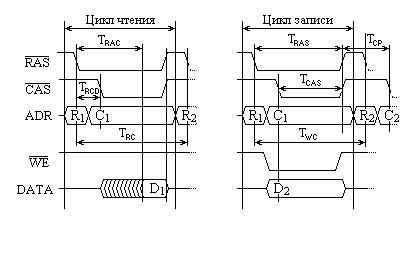

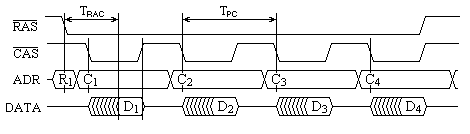

Первые ЗУ, которые впоследствии стали называть асинхронными динамическими ОЗУ, выполняли операции чтения и записи, получив лишь запускающий сигнал (обычно, сигнал строба адреса) независимо от каких-либо внешних синхронизирующих сигналов. Диаграмма циклов чтения и записи для таких ЗУ представлена на рис. 2.3.8, а) и 2.3.8, б) соответственно. Любой цикл (чтения или записи) начинается по спаду (фронту “1” →“0”) сигнала RAS #.

| б) |

| а) |

Рисунок 2.3.8. Временные диаграммы простых циклов чтения а) и записи б)

асинхронной динамической памяти.

Как видно из диаграмм, адрес на шины адреса поступает двумя частями: адрес строки (обозначенный как R 1 или R 2) и адрес столбца (C 1 и C 2). В момент, когда на адресной шине установилось требуемое значение части адреса, соответствующий сигнал строба (RAS # или CAS #) переводится в активное (нулевое) состояние.

Цикл записи начинается так же, как и цикл чтения, по спаду сигнала RAS # после подачи адреса строки. Записываемые данные выставляются на шину данных одновременно с подачей адреса столбца, а сигнал разрешения записи WE # при этом переводится в нулевое состояние (известен и несколько иной цикл “задержанной” записи). По истечении времени, достаточного для записи данных в элементы памяти, сигналы данных, WE #, RAS # и CAS # снимаются, что говорит об окончании цикла записи.

Помимо названного параметра TRAC – времени доступа по отношению к сигналу RAS # (его значение для микросхем второй половины 90-х годов XX столетия составляло от 40 нс до 80 нс), - на временной диаграмме, представленной на рисунке 2.3.8, указаны еще несколько времен:

TRCD – минимальное время задержки между подачей сигналов RAS # и CAS # (RAS-to-CAS Delay);

TRAS и TCAS – длительности (активного уровня) сигналов RAS # и CAS #;

TRC и TWC – длительности циклов чтения и записи соответственно;

TRP и TCP – времена регенерации строки и столбца соответственно (время регенерации определяет минимальную задержку, необходимую перед подачей очередного сигнала RAS# или CAS# после снятия (подъема в “1”) текущего).

Значения времен TRC и TWC для памяти (90-х годов) составляли порядка 50 – 100 нс, так что на одно (полное) обращение уходило от 5 до 7 циклов системной шины в зависимости от ее частоты, особенностей используемого чипсета и, собственно, быстродействия памяти. Так, для системной шины с частотой 66 Мгц длительность цикла составляет порядка 15 нс, что для 5 – 7 циклов дает диапазон 75 – 100 нс, если же частота системной шины составляла 100 МГц, то 5 циклов занимают 50 нс.

Поскольку адрес строки является старшей частью адреса, то для последовательных адресов памяти адрес строки одинаков (исключение составляет переход через границу строки). Это позволяет в (пакетном) цикле обращений по таким адресам задать адрес строки только для обращения по первому адресу, а для всех последующих задавать только адрес столбца. Такой способ получил название FPM (Fast Page Mode – быстрый страничный режим) и мог реализовываться обычными микросхемами памяти при поддержке контроллера памяти чипсета, обеспечивая сокращение времени обращения к памяти для всех циклов пакета, кроме первого. Получающаяся при этом временная диаграмма пакетного цикла чтения представлена на рисунке 2.3.9.

Рисунок 2.3.9. –Временная диаграмма цикла чтения последовательных адресов

динамической памяти DRAM в режиме FPM

Как видно из рисунка, цикл чтения первого слова пакета выполняется так же, как и одиночное обращение. Второй и последующие циклы чтения оказываются короче первого из-за отсутствия фазы подачи адреса строки, и их длительность определяется минимально допустимым периодом следования импульсов CAS # – TPC (Page CAS Time). Соотношение длительностей первого и последующих циклов при частоте системной шины может достигать 5: 3, откуда и обозначение 5-3-3-3, используемое как характеристика памяти, которая указывает, что первый из циклов пакета занимает по времени 5 циклов системной шины, а последующие – по 3 цикла.

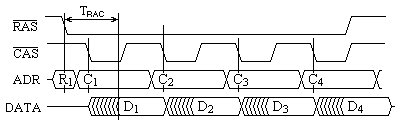

Длительность (низкого уровня) импульса CAS # определяется не только временем извлечения данных из памяти, но и временем удержания их на выходе микросхемы памяти. Последнее необходимо для фиксации прочитанных данных (контроллером памяти), так как данные присутствуют на выходе только до подъема сигнала CAS #. Поэтому следующей модификацией асинхронной динамической памяти стала память EDO (Extended Data Output – растянутый выход данных). В микросхеме EDO памяти на выходе был установлен буфер-защелка, фиксирующий данные после их извлечения из матрицы памяти при подъеме сигнала CAS # и удерживающий их на выходе до следующего его спада. Это позволило сократить длительность сигнала CAS # и соответственно цикла памяти, доведя пакетный цикл до соотношения с циклами системной шины 5-2-2-2 (т.е. сократить длительность второго и последующих циклов в 1,5 раза только за счет выходного регистра-буфера). Временная диаграмма для режима EDO показана на рисунке 2.3.10, а сам этот режим иногда называют гиперстраничным (Hyper Page Mode).

Рисунок 2.3.10 – Временная диаграмма цикла чтения последовательных адресов

динамической памяти DRAM в режиме EDO

Впоследствии появилась и еще одна (последняя) модификация асинхронной DRAM – BEDO (Burst EDO – пакетная EDO память), в которой не только адрес строки, но и адрес столбца подавался лишь в первом цикле пакета, а в последующих циклах адреса столбцов формировались с помощью внутреннего счетчика. Это позволило еще повысить производительность памяти и получить для пакетного цикла соотношение 5-1-1-1.

Однако у отечественных поставщиков этот тип памяти не получил широкого распространения, так как на смену асинхронной памяти пришла синхронная – SDRAM (англ. Synchronous Dynamic RAM).

В отличие от других типов DRAM, использовавших асинхронный обмен данными, ответ на поступивший в устройство управляющий сигнал возвращается не сразу, а лишь при получении следующего тактового сигнала. Тактовые сигналы позволяют организовать работу SDRAM в виде конечного автомата, исполняющего входящие команды. При этом входящие команды могут поступать в виде непрерывного потока, не дожидаясь, пока будет завершено выполнение предыдущих инструкций (конвейерная обработка): сразу после команды записи может поступить следующая команда, не ожидая, когда данные окажутся записаны. Поступление команды чтения приведёт к тому, что на выходе данные появятся спустя некоторое количество тактов — это время называется задержкой (англ. SDRAM latency) и является одной из важных характеристик данного типа устройств. Первый стандарт SDRAM с появлением последующих стандартов стал именоваться SDR (Single Data Rate — в отличие от Double Data Rate). За один такт принималась одна управляющая команда и передавалось одно слово данных. Типичными тактовыми частотами были 66, 100 и 133 МГц. Микросхемы SDRAM выпускались с шинами данных различной ширины (обычно 4, 8 или 16 бит), но как правило, эти микросхемы входили в состав 168-пинного модуля DIMM, который позволял прочитать или записать 64 бита (в варианте без контроля чётности) или 72 бита (с контролем чётности) за один такт.

Использование шины данных в SDRAM оказалось осложнено задержкой в 2 или 3 такта между подачей сигнала чтения и появлением данных на шине данных, тогда как во время записи никакой задержки быть не должно. Потребовалась разработка достаточно сложного контроллера, который не позволял бы использовать шину данных для записи и для чтения в один и тот же момент времени.

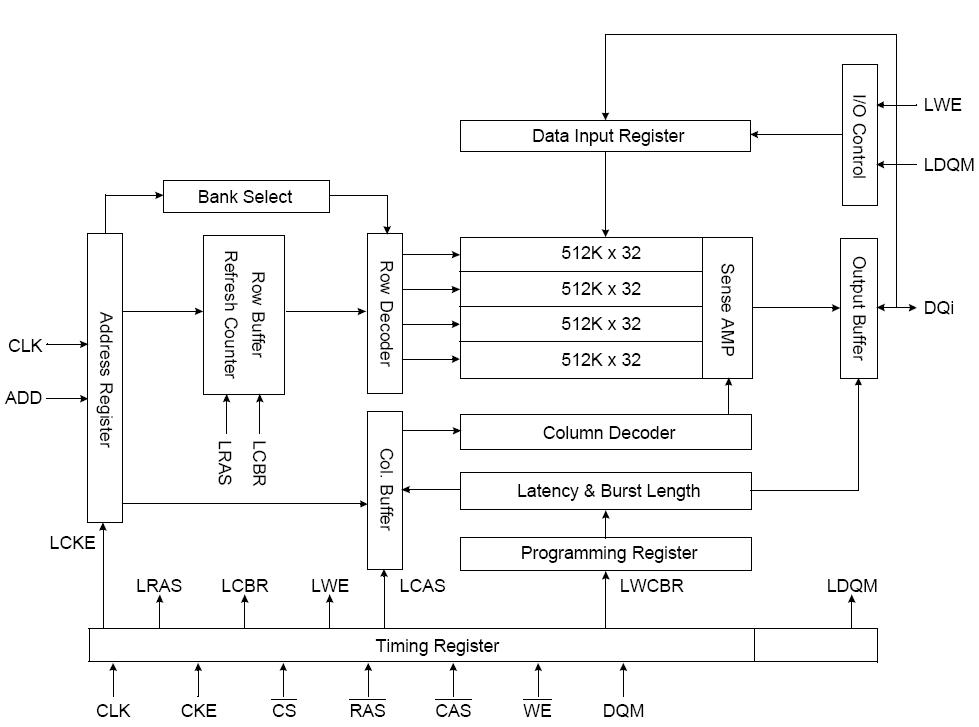

На рисунке 2.3.11 показана структурная схема модуля SDRAM компании «Samsung», KM432S2030C.

Рисунок 2.3.11 Структурная схема SDRAM модуля.

Основные блоки SDRAM модуля:

Address register (регистр адреса)производит считывание адреса с шины и сохраняет значение в регистре адреса. Адрес столбца или строки определяется сигналом LCKE.

Timing Register (регистр синхроимпульсов)–управляющее устройство (командный автомат), которое создает набор сигналов для синхронизации и управления основными функциональными блоками исходя из значений входных сигналов.

Bank Select (блок адресации банков памяти) производит активацию блока памяти.

Row Buffer/Refresh Counter (буфер строки/ счетчик регенерации) сохраняет адрес активированной строки и содержит значение счетчика регенерации для обновления данных.

Row Decoder (дешифратор строки) производит дешифрацию и активацию выбранной строки памяти для организации дальнейшего обращения.

Col Buffer (буфер столбца) хранит текущий адрес столбца памяти.

Column Decoder (дешифратор столбца) производит дешифрацию и активацию выбранного столбца памяти для организации ввода вывода.

Latency & Burst Length (устройство задержки и длины последовательного обращения) создает сигналы для синхронного управления блоками памяти в режиме ввода-вывода данных.

Programming Register (регистр управления) хранит конфигурационные значения, необходимые для синхронной работы памяти.

Sense AMP (блок усилителей) производит усиление и согласование уровней выходных данных.

Output Buffer (буфер выходных данных) производит хранение значений выходных данных в режиме чтения.

I/O Control (блок управления вводом-выводом) осуществляет управление потоком ввода-вывода.

Data Input Register (регистр входных данных) хранит значения входных данных для дальнейшей записи в память.

2015-08-21

2015-08-21 1130

1130