Команды, управляющие модулем памяти SDR SDRAM, подаются на контакты модуля по 7 сигнальным линиям. По одной из них подается тактовый сигнал, передние (нарастающие) фронты которого задают моменты времени, в которые считываются команды управления с остальных 6 командных линий. Имена (в скобках — расшифровки имен) шести командных линий и описания команд приведены ниже:

CLK (system CLocK) – системная синхронизирующая частота. Все процессы синхронизируются по переходу (переднему фронту) из «0» в «1».

CKE (Clock ENable) — при низком уровне сигнала блокируется подача тактового сигнала на микросхему. Команды не обрабатываются, состояние других командных линий игнорируется.

A0-A10 (Address) – адрес строки и столбца мультиплексируются на этих выводах (адрес строки RA0 - RA10, адрес столбца CA0 - CA7).

BA 0,1 (bank select address) – при помощи этих выводов производится активация выбранных банков в режиме установки адреса строки. В режиме чтения/записи производится однозначные операции в выбранных банках памяти.

/CS (Chip Select) — при высоком уровне сигнала все прочие управляющие линии, кроме CLK, CKE и DQM игнорируются. Действует как команда NOP (нет оператора).

DQM 0-3 (data input/output mask) — высокий уровень на этой линии запрещает чтение/запись данных. При одновременно поданной команде записи данные не записываются в DRAM. Присутствие этого сигнала в двух тактах, предшествующих циклу чтения приводит к тому, что данные не считываются из памяти.

/RAS (row address strobe) — позволяет получить доступ к строке. Указывает командному аппарату, что присутствующий адрес на шине является адресом строки.

/CAS (column address strobe) — позволяет получить доступ к столбцу. Указывает командному аппарату, что присутствующий адрес на шине является адресом столбца.

/WE (write enable) — указывает на тип проводимой команды (чтение = «1», запись = «0»).

Для управления SDRAM используются следующие команды:

Упрощенная таблица истинности для SDRAM

Таблица 2.3.1.

| /CS | /RAS | /CAS | /WE | BA n | A10 | A n | Команда |

| x | x | x | x | x | x | задержка команды (нет операции). | |

| x | x | x | нет операции. | ||||

| x | x | x | остановить текущую операцию пакетного чтения или записи. | ||||

| № банка | № столбца | считать пакет данных из активированного ряда. | |||||

| № банка | № столбца | как и предыдущая команда, по завершении произвести деактивацию ряда. | |||||

| № банка | № столбца | записать пакет данных в активированный ряд. | |||||

| № банка | № столбца | как и предыдущая команда, по завершении произвести деактивацию ряда. | |||||

| № банка | № строки | открыть ряд для операций записи и чтения. | |||||

| № банка | x | деактивировать текущий ряд выбранного банка. | |||||

| x | x | деактивировать текущий ряд всех банков. | |||||

| x | X | x | Операция регенерации данных. Все банки должны быть деактивированы. | ||||

| 0 0 | РЕЖИМ | произвести конфигурирование микросхемы данными с линий BA0,1, A0—A10. |

Конфигурирование микросхемы памяти производится путем записи соответствующих значений в поля регистра управления, как показано в таблице 2.3.2.

Таблица значений регистра управления

Таблица2.3.2.

| Адрес | BA0-BA1 | A10/AP | A9 | A8 | A7 | A6-A4 | A3 | A2-A0 |

| Функция | резерв | резерв | режим записи | задержка CAS | тип последователь-ного обращения | длина очереди |

Конфигурирование длины очереди (burst length)в режиме последовательного обращения представлено в таблице 2.3.3.

Для рассматриваемого устройства памяти (KM432S2030C) значение «страница» составляет длину очереди из 32 значений.

Таблица значений длины очереди

Таблица 2.3.3.

| Длина очереди | ||||

| A2 | A1 | A0 | BT=0 | BT=1 |

| резерв | резерв | |||

| резерв | резерв | |||

| резерв | резерв | |||

| страница | резерв |

Тип последовательного обращения (Burst Type) определяется значением A3. Если A3 = 0, то тип обращения устанавливается последовательный, если A3 = 1, то обращение будет чередующимся. Пример показан в таблицах 2.3.4, 2.3.5.

Последовательность обращений при длине очереди (burst length)= 4

Таблица 2.3.4.

| Начальный адрес | Последовательный режим | Чередующийся режим | |||||||

| A1 | A0 | ||||||||

Последовательность обращений при длине очереди (burst length) = 8

Таблица 2.3.5.

| Начальный адрес | Последовательный режим | Чередующийся режим | ||||||||||||||||

| A2 | A1 | A0 | ||||||||||||||||

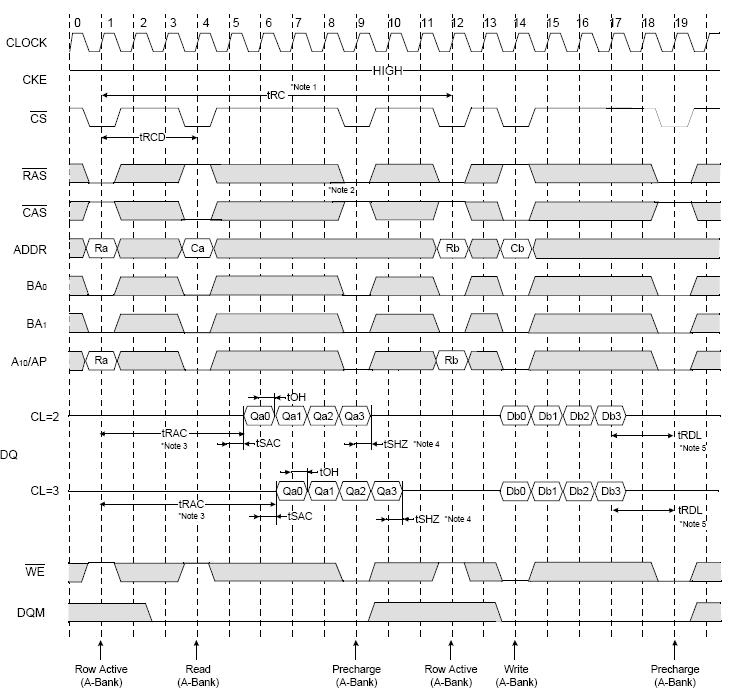

Задержка CAS устанавливается значениями A6-A4 и определяет количество тактовых импульсов от возникновения активного уровня CAS (адрес столбца) до возникновения данных на выходе в режиме чтения. Диаграмма чтения и записи с длиной очереди = 4 (burst length = 4), представлена на рисунке 2.3.12.

Режим записи устанавливается значением сигнала A9 и определяет либо очередной режим (A9=0), либо одиночный (A9=1).

Рисунок 2.3.12. – Диаграмма чтения и записи с длиной очереди =4

DDR SDRAM (англ. Double Data Rate Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных). При использовании DDR SDRAM достигается удвоенная скорость работы, нежели в SDRAM, за счёт считывания команд и данных не только по фронту, как в SDRAM, но и по спаду тактового сигнала. За счёт этого удваивается скорость передачи данных без увеличения частоты тактового сигнала шины памяти. Таким образом, при работе DDR на частоте 100 МГц мы получим эффективную частоту 200 МГц (при сравнении с аналогом SDR SDRAM). В спецификации JEDEC есть замечание, что использовать термин «МГц» в DDR некорректно, правильно указывать скорость «миллионов передач в секунду через один вывод данных».

Отличие DDR2 от DDR - вдвое большая частота работы шины, по которой данные передаются в буфер микросхемы памяти.

Отличие DDR3 от DDR2 уменьшено на 40% потребление энергии, что обусловлено пониженным (1,5 В, по сравнению с 1,8 В для DDR2 и 2,5 В для DDR) напряжением питания для ячеек памяти. Снижение напряжения питания достигается за счёт использования 90-нм (вначале, в дальнейшем 65-, 50-, 40-нм) техпроцесса при производстве микросхем и применения транзисторов с двойным затвором Dual-gate (что способствует снижению токов утечки).

DDR4 Будет поддерживать частоты от 2133 до 4266 МГц, при этом напряжение питания ячеек памяти снижено до 1.2 В.

Флеш-память (англ. flash memory) — разновидность твердотельной полупроводниковой энергонезависимой перезаписываемой памяти (ПППЗУ). Она может быть прочитана сколько угодно раз (в пределах срока хранения данных, типично — 10–100 лет), но писать в такую память можно лишь ограниченное число раз (максимально — около миллиона циклов). Распространена флеш-память, выдерживающая около 100 тысяч циклов перезаписи — намного больше, чем способна выдержать дискета или CD-RW. Не содержит подвижных частей, так что, в отличие от жёстких дисков, более надёжна и компактна.

TRAM (англ. Thyristor RAM) — тиристорная память с произвольным доступом, новый вид оперативной памяти, сочетающий в себе сильные стороны DRAM и SRAM: высокую скорость работы и большой объём. ПамятьTRAM является хорошо масштабируемой, и уже имеет плотность хранения данных в несколько раз превышающую её у SRAM памяти. В данный момент идёт разработка следующего поколения TRAM памяти, которая, как планируется, будет сопоставима по плотности записи с DRAM.

MRAM (англ. Magnetoresistive Random-Access Memory) — это запоминающее устройство c произвольным доступом, которое хранит информацию при помощи магнитных моментов, а не электрических зарядов.

Важнейшее преимущество этого типа памяти — энергонезависимость, то есть способность сохранять записанную информацию при отсутствии внешнего питания.

Технология магниторезистивной памяти разрабатывается с 1990-х годов. В сравнении с растущим объемом производства других типов компьютерной памяти, особенно флэш-памятью и памятью типа DRAM, она пока широко не представлена на рынке.

Ассоциативная память (АП) является особым видом машинной памяти, используемой в приложениях очень быстрого поиска. Известна также как память, адресуемая по содержимому, ассоциативное запоминающее устройство, контентно-адресуемая память или ассоциативный массив, хотя последний термин чаще используется в программировании для обозначения структуры данных.

В отличие от обычной машинной памяти (памяти произвольного доступа, или RAM), в которой пользователь задает адрес памяти и ОЗУ возвращает слово данных, хранящееся по этому адресу, АП разработана таким образом, чтобы пользователь задавал слово данных, и АП ищет его во всей памяти, чтобы выяснить, хранится ли оно где-нибудь в нем. Если слово данных найдено, АП возвращает список одного или более адресов хранения, где слово было найдено (и в некоторых архитектурах, также возвращает само слово данных, или другие связанные части данных). Таким образом, АП — аппаратная реализация того, что в терминах программирования назвали бы ассоциативным массивом.

Из-за того, что АП разработана, чтобы искать во всей памяти одной операцией, это получается намного быстрее чем поиск в RAM фактически во всех приложениях поиска. Однако, есть и минус в большей стоимости АП. В отличие от чипа RAM, у которого хранилища простые, у каждого отдельного бита памяти в полностью параллельной АП должна быть собственная присоединенная схема сравнения, чтобы обнаружить совпадение между сохраненным битом и входным битом. К тому же, выходы сравнений от каждой ячейки в слове данных должны быть объединены, чтобы привести к полному результату сравнения слова данных. Дополнительная схема увеличивает физический размер чипа АП, что увеличивает стоимость производства. Дополнительная схема также увеличивает рассеиваемую мощность, так как все схемы сравнений активны на каждом такте. Как следствие, АП используется только в специализированных приложениях, где скорость поиска не может быть достигнута используя другие менее дорогостоящие методы.

Для того, чтобы достигнуть другого баланса между скоростью, размером памяти и стоимости, некоторое реализации эмулируют функции АП путем использования стандартного поиска по дереву или алгоритмов хеширования реализованных аппаратно, также используя для ускорения эффективной работы такие аппаратные трюки как репликация и конвейерная обработка. Эти проекты часто используются в маршрутизаторах.

Двоичная АП — простейший тип ассоциативной памяти, который использует слова поиска данных, состоявшие полностью из единиц и нулей. В троичной АП добавляется третье значение для сравнения «X» или «не важно», для одного или более битов в сохраненном слове данных, добавляя таким образом большей гибкости поиску. Например, в троичной АП могло бы быть сохранено слово «10XX0», которое выдаст совпадение на любое из четырех слов поиска «10000», «10010», «10100», или «10110». Добавление гибкости к поиску приходит за счет увеличения цены двоичной АП, поскольку внутренняя ячейка памяти должна теперь закодировать три возможных состояния вместо двух. Это дополнительное состояние обычно осуществляется добавлением бита маски «важности»(«важно»/«не важно») к каждой ячейке памяти.

2015-08-21

2015-08-21 2927

2927