При работе в защищенном режиме каждый сегмент определяется специальной восьмибайтной структурой, которая называется дескриптор сегмента (Segment Descriptor).

| Права доступа AR |

| Базовый адрес G D X U Предел P DPL S Тип A Базовый 31-24 19-16 адрес 23-16 |

| Базовый адрес Предел 15-0 15-0 |

| 63 47 39 32 |

| 31 23 15 7 0 0 |

Поля дескриптора имеют следующие названия:

AR - Access Rights

DPL - Descriptor Privilege Level

D - Default size

U - User

A - Accessed

G - Granularity

P - Present

S - System(segment)

AVL - Available

Число дескрипторов в системе практически неограниченно. Если какую-то область адресного пространства не описать дескриптором, соответствующий диапазон адресов оказывается недоступным и процессор блокирует доступ к этим адресам.

Поля, необходимые для определения сегментов памяти:

1) Базовый адрес - это 32-х битное поле. Занимает 2,3,4,7 байты дескриптора и определяет начальный адрес сегмента в линейном адресном пространстве 4 Gb. Этот адрес формирует процессор при нулевом смещении.

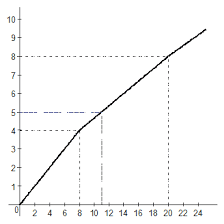

2) Предел - 0,1 байты и 4 бита - граница сегментаили еще называют размер сегмента(20 бит). Он равен размеру сегмента в байтах минус 1. Предел задает последнюю адресуемую единицу в сегменте. 20-битное поле предела позволяет определить размер в 1 Mb элементов.

3) Бит G (гранулярность) - определяет единицы измерения элементов памяти:

- G=0, то поле предела измеряется в байтах и соответственно имеет размер 1 Mb;

- G=1, то единицей измерения является страница, каждая из которых имеет размер 4Kb, следовательно, максимальный размер 1 M*4Kb = 4 Gb.

Бит A - бит доступа. Автоматически устанавливается в 1, когда производится обращение к памяти, описанной данным дескриптором. Этот бит можно использовать для того, чтобы определить те сегменты, к которым долго не было обращения.

Бит D - размер по умолчанию. Он используется для совместимости с процессором 286.

Бит U - пользовательский. Его называют AVL. Он предназначен для использования при системном программировании.

Бит AR - байт прав доступа. Байт прав доступа определяет тип сегмента и те возможности, которые предоставляются программе при работе с этим сегментом.

4) Для всех типов дескрипторов в байте доступа имеется бит P (присутствие):

P=1, когда описываемый дескриптором сегмент находится в физической памяти. В системе с виртуальной организацией памяти часть сегментов располагается на вешней дисковой памяти, бит P = 0, и если программа обращается к сегменту, у которого в дескрипторе бит Р = 0, то возникает особый случай неприсутствия сегмента. В таком случае ОС должна найти свободную область в ОП, скопировать с диска содержимое сегмента в эту область, загрузить в дескриптор новый базовый адрес сегмента, установить P = 1 и осуществить повторный запуск команды, вызвавшей особый случай. Процесс обращения к не присутствующему сегменту с последующими передачами сегмента между основной памятью и диском называется свопингом (подкачкой-swapping). Если свободного места для размещения сегмента в ОП нет, то ОС должна выгрузить некоторые сегменты из ОП на дескрипторы этих сегментов и Р = 0.

5) DPL – уровень привилегий дескриптора сегмента (2 бита). Определяет уровень привилегий, ассоциируемый с той областью памяти, которую описывает дескриптор. Поэтому его следовало бы назвать уровень привилегий сегмента. Наивысший уровень привилегий: DPL =00 (ноль), а наименьший – DPL =11 (три). Поле DPL - составная часть механизма защиты в процессоре.

6) Бит S (системный, бит сегмента). В дескрипторах сегментов памяти этот бит всегда равен 1. А в дескрипторах системных объектов S=0.

Трех битное поле типа определяет целевое использование сегмента, задавая допустимые в сегменте операции.

Тип:

000 – сегмент данных, разрешено только считывание;

001 – сегмент данных, разрешено считывание и запись;

010 – сегмент стека, разрешено только считывание;

011 – сегмент стека, разрешено считывание и запись;

100 – сегмент кода, разрешено только выполнение;

101 – сегмент кода, разрешено выполнение и считывание;

110 – подчиненный сегмент кода, разрешено только выполнение;

111 – подчиненный сегмент кода, разрешено выполнение и считывание.

С каждым сегментным регистром связан 64-битный теневой регистр. В него загружается дескриптор, на который указано содержание сегментного регистра.

Для хранения дескриптора выделяется участок памяти – специальной таблицы. Есть одна общая глобальная дескрипторная таблица, и может быть большое число локальных дескрипторных таблиц. Адрес и размер глобальной дескрипторной таблицы заносится в GDTR. Может храниться 8192 дескриптора. Есть дескрипторная таблица прерываний и много локальных таблиц.

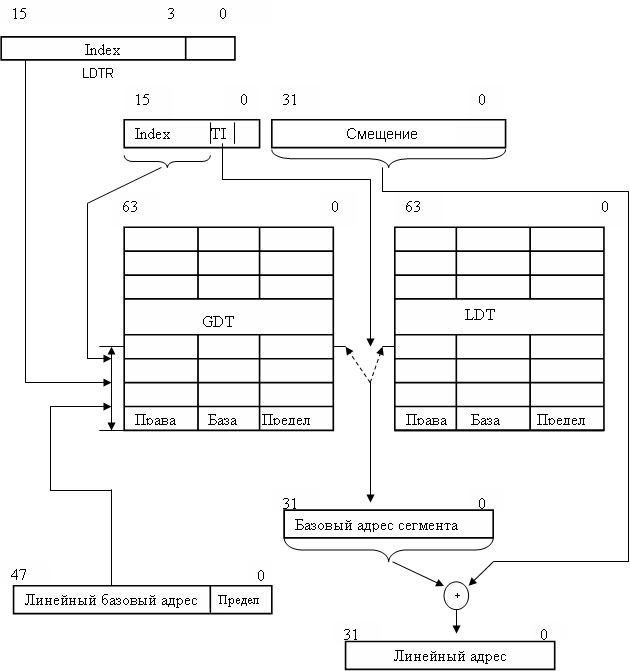

При работе в защищенном режиме сегментные регистры состоят из трех частей.

| Индекс TI RPL |

Схема преобразования адреса при работе в защищенном режиме:

Последовательность действий по преобразованию логического адреса в линейный адрес.

Взять селектор из сегментного регистра.

Если бит TI=0, то для преобразования задействована глобальная дескрипторная таблица. В этом случае:

1) Определяется адрес дескриптора в GDR. Для этого к линейному адресу GDR (хранится в GDTR) прибавляется значение индекса, умноженного на 8. Получится адрес выбранного дескриптора.

2) Из дескриптора выбирается базовый адрес сегмента (32бита)

3) К базовому адресу сегмента прибавляется смещение (эффективный адрес) и результат суммы является линейным адресом. Он же физический, если задействована только сегментная организация памяти.

Если бит TI=1, т.е. показывает на LDT, то:

1) Взять селектор сегмента LDT из регистра LDTR.

2) Выделить в селекторе поле индекса, умножить этот индекс на 8 и т.о. получить смещение внутри GDT, которое указывает на расположение дескриптора в LDTR.

3) Прибавить полученное значение к адресу GDT из регистра GDTR.

4) Считать из памяти адресуемый дескриптор.

5) Выделить из этого дескриптора базовый адрес сегмента, содержащего таблицу LDT, полученный адрес является адресом;

Выделить значение из поля исходного индекса селектора, умножить его на 8 и прибавить к адресу дескрипторной таблицы и считать дескриптор по этому адресу;

Выделить из дескриптора базовый адрес сегмента;

Прибавить значение смещения к базовому адресу сегмента, в результате получим линейный адрес

Осуществить обращение к памяти в соответствие с полученным линейным адресом

Если отмеченные действия производить каждый раз при преобразовании адреса, то время преобразования адреса было бы значительно больше, чем при работе процессора в реальном режиме.

Для ускорения таких преобразования адреса в процессоре имеются специальные теневые регистры, связанные с сегментными регистрами и LDTR. Размер этих регистров 64 бита и при загрузке нового значения либо в сегментный регистр, либо в LDTR, в соответствующий теневой регистр помещается в выбранный дескриптор из дескрипторной таблицы. Применение теневых регистров позволяет время преобразования адреса при работе в защищенном режиме сделать почти равным времени преобразования

В случае страничной организации памяти из линейного адреса происходит переход к физическому адресу.

PDE – Page Directory Entry.

PTE – Page Table Entry.

PDBR – Page Directory Base Register.

| ... PDE ... |

| ... PTE ... |

| Страничный кадр Байт |

| PDBR |

| Каталог Таблица Смещение |

| Каталог страниц |

| 31 0 |

| 31 … 0 |

| Физическая память |

| CR3 |

| 31 22 21 12 11 0 |

| 19 0 |

| Таблицы страниц |

В процессоре имеется специальная ассоциативная страница буфера. Таким образом, операция происходит в процессоре без обращения к памяти. На страничном уровне поддерживается только два уровня привилегий: системный и пользовательский.

2015-08-21

2015-08-21 820

820