Варіант 1. Розробити схему шифратора (8®3) для перетворення 8-розрядного вхідного коду в 3-розрядний двійковий код числа i, де i - номер позиції «0» (або «1») у вхідному коді.

Шифратором називають КС із декількома входами (Х) і виходами (Y), у якого кожної комбінації вхідних кодів Х=x0…xm (звичайно «один xi з m») відповідає комбінація вихідного двійкового коду Y=у0…уn. Шифратор виконує функцію зворотну тієї, котру реалізує дешифратор (див. варіант 8).

Повний двійковий шифратор має m = 2n входів і n виходів (при цьому m > n).

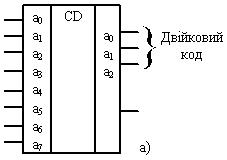

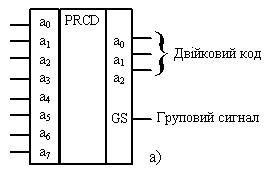

|

|

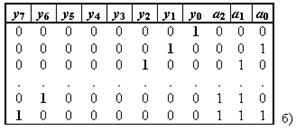

Рисунок 2.1 − Шифратор 8®3 з активним значенням на входах х0…х7 у вигляді «0» (а) і таблиця істинності (ТІ) його роботи (б).

На основі ТІ за рис. 2.1 можна записати відповідні структурні форми у вигляді ДНФ (КНФ) для восьми вхідних змінних (Х=x0…x7) і потім виконати необхідні дії для їхнього спрощення. Одержання МДНФ (МКНФ) для кожної з функцій Y шифратора за рис. 1.1 за допомогою класичних методів мінімізації викличе утруднення, тому що число аргументів Х функції дорівнює восьми (Х=x0…x7). Але в цьому випадку можна використати особливість виду вхідних змінних − їх регулярність (які в випадках, що нас цікавлять, мають значення x0…x7 рівне «0» − див. «діагональ» у ТІ) і представити змінні на виході Y= у0, у1, у2 (рівні «1») у вигляді:

Y 0 = x7 V x5 V x3 V x1 = x7 * x5 * x3 * x1;

Y 1 = x7 V x6 V x3 V x2 = x7 * x6 * x3 * x2;

Y 2 = x7 V x6 V x5 V x4 = x7 * x6 * x5 * x4.

При такому підході «прив’язка» до конкретних x0…x7 зі значеннями «0» і відповідність їм конкретних у0, у1, у2 зі значеннями «1» однозначно визначає їх ЛФ.

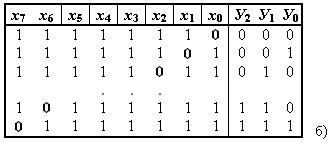

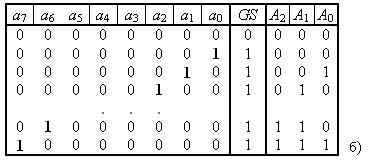

Позначення й таблиця істинності (ТІ) для пріоритетного шифратора PRCD (8®3) з активним значенням у вигляді «1» на входах а0…а7 і з додатковим виходом GS (груповий сигнал) наведена на рис 2.2.

Рисунок 2.2− Пріоритетний шифратор 8®3 з активним значенням у вигляді «1» на входах а0…а7 і груповим сигналом GS (а); ТІ його роботи (б).

Варіант 2. Розробити схему двійкового дешифратора 3®8 перетворення 3-розрядного двійкового коду в код «один з n».

Дешифратор відносять до перетворювачів кодів і називають КС із декількома входами (Х) і виходами (Y), у якого кожній комбінації вхідних двійкових кодів Х = x0…xn відповідає комбінація вихідного коду типу «один уi з m», тобто значення («1» або її інверсія «0») має тільки один визначений вихід уi (збуджується один з m ланцюгів на виході − код називається «унітарним»). Повний двійковий дешифратор має n входів і m = 2n виходів (при цьому m > n). Функції дешифратора й шифратора (див. варіант 1) взаємообернені.

Дешифратори класифікують за основними (-) та другорядними (--) ознаками:

- структурною організацією − одноступеневі й багатоступеневі;

- форматом вхідного коду − двійкові, двійково-десяткові, ін.;

- розрядністю коду, який дешифрується − 2, 3, 4,..., n;

- кількістю використаних із m виходів − повні й неповні дешифратори;

- формою подачі вхідного коду − з однофазним, парофазними входами;

- видом вхідних стробуючих сигналів (прямий «1», інверсний «0», ін.);

- типом використаної логіки − базис Буля, Шефера, Пірса;

У ЦА, комп’ютерах дешифратори використовують при виконанні таких операцій:

- дешифрування коду операції (записані в регістрі команд процесора) і вибір потрібної мікрокоманди;

- перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам’яті (запис та читання інформації);

- забезпечення візуалізації на зовнішніх пристроях;

- реалізація логічних операцій і побудова мульти- та демультиплексорів.

Рисунок 2.3 − Дешифратор 3®8 з активним значенням на виходах х0…х7 у вигляді «1» (а) і таблиця істинності (ТІ) його роботи (б). Позначення дешифратора DC від англійського слова decoder.

На основі ТІ за рис. 2.3 легко записати відповідні структурні форми у вигляді ДНФ (КНФ) для трьох вхідних змінних (Х = а0, а1, а3) і потім виконати необхідні дії для їхнього спрощення. Одержання МДНФ для кожної з функцій Y дешифратора по за рис. 2.3 за допомогою класичних методів мінімізації не викличе утруднення:

Y 0=  ; Y 1=...........; ……...; Y 7=.........

; Y 1=...........; ……...; Y 7=.........

Стандартний підхід «прив’язки» вхідних а0, а2, а3 у вигляді МДНФ і зіставлення ним конкретних у0, у1, …, у7 зі значеннями «1» однозначно визначає їх ЛФ. Для збільшення функціональних можливостей дешифраторів часто використовують сигнали керування (звичайно позначені буквами V або G) активні по «1» або «0» значенню. Наприклад, при відсутності сигналу G = «0» (що дозволяє дешифрацію вхідного коду а0 , а2, а3) на виходах Y встановлюється значення «1» (або «0»).

Варіант 3. Побудова повного однорозрядного суматора (ПОС) на основі реалізації його ТІ (на схемах одного з базисів − варіанти а, б, в).

Синтез комбінаційної схеми ПОС, що має позначення SМ, починають з аналізу його дії над вхідними змінними  . ПОС здійснює арифметичну дію додавання (рис. 2.4 а) паралельних n -розрядних кодів бінарних чисел

. ПОС здійснює арифметичну дію додавання (рис. 2.4 а) паралельних n -розрядних кодів бінарних чисел  та

та  за правилом: 0+0=0; 0+1=1; 1+0=1; 1+1=10 (1 − перенос

за правилом: 0+0=0; 0+1=1; 1+0=1; 1+1=10 (1 − перенос  ).

).

Схему, що реалізує правила додавання, не враховуючи розряд попереднього переносу, називається однорозрядним напівсуматором, позначається НS, має два входи ( − одноіменні розряди чисел

− одноіменні розряди чисел  ,

,  ) і два виходи (

) і два виходи ( − часткова сума

− часткова сума  по модулю два і

по модулю два і  − перенос

− перенос  в наступний розряд).

в наступний розряд).

SМ відрізняється від НS додаванням трьох однорозрядних чисел ( ), коли враховується перенос одиниці з молодшого розряду. Таблиця істинності (ТІ) його представлено на рис. 2.4 б. Пристрій, який побудований за цією таблицею є ПОС та має три входи і два виходи, де входи

), коли враховується перенос одиниці з молодшого розряду. Таблиця істинності (ТІ) його представлено на рис. 2.4 б. Пристрій, який побудований за цією таблицею є ПОС та має три входи і два виходи, де входи  − одноіменні розряди чисел

− одноіменні розряди чисел  і

і  ;

;  − перенос

− перенос  одиниці із попереднього розряду;

одиниці із попереднього розряду;  − часткова сума

− часткова сума  по модулю два і

по модулю два і  – перенос

– перенос  одиниці в наступний розряд.

одиниці в наступний розряд.

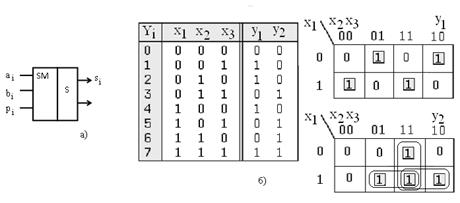

Рисунок 2.4 − Зображення ПОС (а), таблиця істинності ПОС та карти Карно функцій у1, у2 (б).

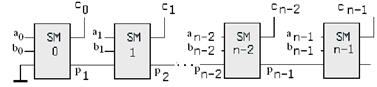

Сукупність ПОС із послідовним переносом одиниць переповнення рі для додавання n -розрядних бінарних чисел показана на рис. 2.5. Його недоліком є великий час затримки.

Рисунок 2.5 – ПОС із послідовним переносом переповнення

Суматор належить до арифметико-логічного устаткування, тому від його швидкодії залежить продуктивність всієї системи. Частіше за все застосовують комбінаційні суматори із паралельною схемою переносу одиниці переповнення  .

.

У звіті за ТІ (рис. 2.4) будується система ЛФ у вигляді ДДНФ (ДКНФ) функцій y 1=  і y 2=

і y 2=  для ПОС та проводиться її мінімізація. Мінімізувати ДДНФ (ДКНФ) функцій y 1, y 2 можливо аналітичним методом або за допомогою карт Карно.

для ПОС та проводиться її мінімізація. Мінімізувати ДДНФ (ДКНФ) функцій y 1, y 2 можливо аналітичним методом або за допомогою карт Карно.

Спочатку провести приводиться мінімізація ДДНФ функції y 2, бо вона може бути скорочена (про це свідчать суміжні клітини на карті Карно) і отримана ДНФ повинна значно скоротитися до виразу:  (в звіті привести рішення).

(в звіті привести рішення).

При мінімізації функції y 1 та її ДДНФ по картам Карно видно, що вона не може бути мінімізована у базисі Буля (АБО-НІ, НІ, І-НІ), Пірса (АБО-НІ, НІ) і Шеффера (І-НІ, НІ). Треба відмітити, що діагональні розташування одиниць (нулів) на картах Карно характерні для функції ∑ mod 2 (або проінвертованій «Рівнозначності»). При реалізації ПОС розробника цікавить мінімальна кількість схем, що входять в його архітектуру та збільшення швидкодії, а не прив’язка до якогось базису. Тому перейдемо від ДНФ для y 1 до схеми ∑ mod 2 (для переходу треба використати вираз, провівши спрощення і привести його рішення):

Варіант 4 включає побудову повного однорозрядного суматора (ПОС, позначення SМ) на основі реалізації його ТІ:

а) на одному з обраних базисів (а, б по варіантам);

б) на здвоєному мультиплексорі 4®1 (наприклад ІС імпортної серії 74153 або К155КП2 − аналог СНД) [13,14] і перевірка його функціонування відповідно до його ТІ.

Зображення суматора SМ, функціональної схеми мультиплексора 4®1 (74153 або К155КП2) і верхня половини його ТІ наведені на рис. 2.6 а, б, в (відповідно), де прийняті наступні позначення: ai і bi − одноіменні i -ті розряди що складають, si − розряд суми, рi − перенос із i -го розряду в суматор, рi +1- перенос в (i +1) розряд наступного суматора [1-12].

Рисунок 2.6 − Однорозрядний суматор − а; здвоєний мультиплексор 4®1 типу 74153 − б; ТІ однієї половини здвоєного мультиплексора К155КП2 − в.

Мультиплексор має входи інформаційні D 0 ...D 3 і адресні A 2, A 1. Двійковий код адреси означає номер того інформаційного входу, що комутується на вихід F 1 (F 2 ) (див. ТІ рис. 2.6 в). Адресні входи для здвоєного мультиплексора є загальними для обох половин схеми 74153.

Одним із корисних застосувань мультиплексора є використання його в якості універсального логічного модуля для відтворення булевих функцій. Як видно з таблиці істинності мультиплексора К155КП2 (мал. 1.2, г), рівняння, що описує його роботу для одного з виходів F1, має вигляд:

(2.1)

(2.1)

Поставлене вище завдання вимагає реалізації на даному мультиплексорі двох функції від трьох змінних (si = j1×(ai, bi, ci) і ci +1 = j2×(ai, bi, ci)). У загальному випадку на основі мультиплексора можуть бути відтворені булеві функції від числа змінних n ³ m, де m − число адресних входів мультиплексора. Випадок n = m вважається тривіальним на відміну від n > m, коли потрібне попереднє розкладання шуканої функції в ряд Шенона по m змінним.

Нехай n=m +1=3 (тобто m =2). Представимо довільну булеву функцію y = f (x3, x2, x1) її розкладанням по змінним x 2 і x 1 (тобто тим змінним, які задаються на адресні входи):

(2.2)

(2.2)

Тут f 0, f 1, f 2, f 3 – залишкові функції від одного аргументу − змінної x 3. Порівняння рівнянь (2.1) і (2.2), дозволяє виробити підхід до реалізації методу. На закінчення відзначимо, що функцію si потрібно одержати на виході F 1 мультиплексора, а функцію ci +1 - на виході F 2.

В звіті у випадку відсутності можливості мінімізації ДНФ (КНФ) функцій y 1, реалізувати її в наступній послідовності:

- для y 1 = сi використати схему ∑ mod 2 (для переходу використаємо вираз):

-провести спрощення, привести його рішення.

Варіант 5 включає побудову п’яти/шестирозрядного перетворювача прямого коду у обернений (а) і додатковий (б), при цьому один/два розряди виділені на знакову частину (два Sg 1, Sg 2 − для модифікованого коду), інші − на цифрові [1-12]. Необхідно пам’ятати, що позитивні числа мають однакове представлення в обох кодах.

Синтез схеми п'яти-/шестиразрядного перетворювача прямого коду у зворотний.

Правило перетворення. Зіставлення прямого й зворотного кодів операнду А показує, що останній (для негативних чисел при Sg 1= Sg 2=1) відрізняється від першого інверсними значеннями всіх цифрових розрядів (увага, знакові розряди завжди залишаються рівними для обох кодів). Дане правило відноситься до будь-якого цифрового n-розрядного коду (ai − розряд числа на вході перетворювача, bi − на виході) і його можна записати в наступному виді для довільного i -го цифрового розряду коду:

- для негативних чисел: bi = āi , при Sg 1= Sg 2=1;

- для позитивних чисел: bi = ai , при Sg 1= Sg 2=0.

Схема повинна бути єдиною й виконувати запропоновані їй функції незалежно від того, які числа подаються на її вхід − позитивні або негативні в якому-небудь із розглянутих кодів.

Пояснення до рішення. Інвертуванням цифрових розрядів αi керує знаковий розряд Sg 1= Sg 2= αs на основі використання логічної операції ∑ mod 2: αs Å αi, i =1, 2, 3, 4 для 4-х розрядного операнду А. При цьому необхідно реалізувати у звіті основний варіант рішення схеми й указати інші можливі варіанти.

Синтез схеми перетворювача прямого коду двійкових чисел у додатковий код.

Правило перетворення. Для перетворення прямого коду негативного числа в додатковий код необхідно проінвертувати цифрові розряди вихідного числа й до отриманого результату додати «1» у молодший розряд (увага, молодший цифровий і знаковий розряди завжди залишаються рівними для обох кодів). При цьому необхідно реалізувати у звіті основний варіант рішення схеми й указати інші можливі варіанти.

Пояснення до рішення. Інвертуванням цифрових розрядів αi керує знаковий розряд Sg 1= Sg 2= αs на основі використання логічної операції ∑ mod 2: αs Å αi, i=1, 2, 3, 4 для 4-х розрядного операнду А. Додавання одиниці можливо виконати із використанням 4-розрядного суматора на ІС 74283, 7483N (К155ИМ3), представлений на рис. 2.7 або іншим способом.

Рисунок 2.7 – Мікросхема К155ИМ3 – 4-розрядний двійковий повний суматор.

В роботі необхідно реалізувати опис функціонування перетворювача коду у вигляді логічної схеми (привести креслення) на основі ІС ∑ mod 2 (7486, 74136, ін.) або на основі ін. схем логіки.

Варіант 6 включає побудовуперетворювача коду 8-4-2-1 у 7-розрядний код семисегментного індикатора для подання, наприклад: 16-кових чисел 0, 1,..., 9, А, B, C, D, E, F; десяткових чисел 0,..., 9 і ряду букв російського, латинського алфавіту (звичайно не збігаються по виду із цифрами).

Індикатори являють собою набір світлодіодів (СД) розташованих таким чином, щоб світіння частини з них (або всіх) забезпечувало появу зображення необхідної цифри (0, 1,..., 9), букви (А, Б, …, Я), знака (!,?) або символу (±, ≠, …, ≥, …).

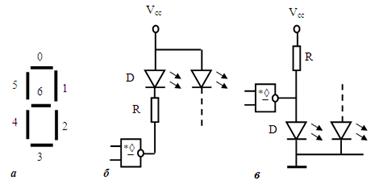

Для виводу чисел у двійковій, вісімковій, десятковій, шістнадцятковій і ін. системах числення застосовуються семисегментні індикатори, у яких сім сегментів − світлодіодів розташовані так, що при запалюванні певної їхньої комбінації засвічується той або інший символ (рис. 2.8 а). Сукупність індикаторів (більше одного) забезпечують появу декількох розрядів числа й/або цілого слова, що несе значеннєве навантаження (приклад: ПУТЬ 8).

Індикатори бувають 1, 2, 3, 4-х і багаторозрядні, діляться на цифрові (із крапкою, комою або без них), буквено-цифрові, символьно-буквено-цифрові й спеціалізовані (наприклад, для вказівки крену апарата, рівня рідини в ємностях, ін.).

Розповсюдженим прикладом використання зазначених пристроїв візуалізації інформації є семисегментні індикатори на СД (із крапкою, комою або без них), які випускаються у двох різновидах за схемним рішенням: із загальним анодом (рис. 2.8 б) або загальним катодом (рис. 2.8 в). Для керування сегментами індикатора за схемою рис. 2.8 б є зручними логічні елементи з виходом типу «загальний колектор». У цьому випадку підключається зовнішній резистор, опір R якого задає струм СД із урахуванням характеристик застосовуваних СД (сегмент засвічується, коли вихідний транзистор керуючого елемента відмикається − рис. 2.8 б). На рис. 2.8 в,сегмент у вигляді СД засвічується, коли вихідний транзистор керуючого елемента замикається. Перевагою (при зазначеній полярності підключення) володіють схеми індикаторів із загальним анодом (рис. 2.8 б) через відсутність споживання, коли вони не світяться.

Рисунок 2.8 – Семисигментний індикатор (а) і схеми керування сегментом із загальним анодом (б) і загальним катодом (в).

Перетворювач коду 8-4-2-1 в 7-розрядний код семисегментного індикатора для подання 16-их чисел 0,..., 9, А, b, C, d, E, F повинен працювати відповідно до таблиці істинності (табл. 2.1). Перевірку роботи дешифратора коду 8-4-2-1 у відповідний світний символ необхідно зробити шляхом підключення до його виходів обраного семисегментного індикатора із БМ програми EWB 5.12.

Таблиця 2.1 – Таблиця істинності перетворювача коду 8-4-2-1 в 7-розрядний код семисегментного індикатора

| 16-ва | Код 8-4-2-1 | 7-сегментний вихід |

| 7 6 5 4 - 3 2 1 0 | ||

| 0 1 1 1 - 1 1 1 1 | ||

| 0 0 0 0 - 0 1 1 0 | ||

| 0 1 0 1 – 1 1 0 1 | ||

| ... | ... | ... |

| A | 0 1 1 1 – 0 1 1 1 | |

| B | 0 1 1 1 – 1 1 0 0 | |

| ... | ... | ... |

| F | 0 1 1 1 – 0 0 0 1 |

Варіант 7. Перетворювач 4-розрядного двійкового коду типу 8-4-2-1 у код Грея й назад. Логічний базис − елемент ∑ mod 2.

У деяких випадках необхідний числовий код, побудований таким чином, щоб при переході від одного числа до наступного змінювався б завжди тільки один двійковий розряд. Цією властивістю володіє код Грея, що використається для розмітки координат кліток карт Карно, у перетворювачах кутового положення вала в цифровий код і в ін. випадках, де умовою його застосування є «плавний» перехід у вигляді зміни одного розряду при збільшенні (зменшенні) коду на одиницю від вихідного (див. табл. 2.2, наведена її верхня частина). Це ілюструє куб з 8-ма вершинами (х 1, х 2, х 3 − для 3-х змінних), де застосування коду Грея забезпечує «плавний» перехід від однієї вершини куба (000, 001, 011, …, 111) до іншої тільки по його ребрах (у відмінності від двійкового коду 4-2-1, у якому поряд з «плавними» є «неплавні» переходи по діагоналях площин і діагоналі куба). Код Грея не є позиційним, тобто ваги його розрядів не визначаються займаними ними місцями (як у звичайному позиційному двійковому коді, наприклад 8-4-2-1). Відповідність між 4-розрядним двійковим (зрівняти код 8-4-2-1 БКДС) і кодом Грея відображена в табл. 2.2.

Таблиця 2.2 – Верхня половина таблиці відповідності між 4-розрядним двійковим і кодом Грея.

| Двійковий код | Код Грея |

| α 1 α 2 α 3 α 4 | β 1 β 2 β 3 β 4 |

| 0 0 0 0 | 0 0 0 0 |

| 0 0 0 1 | 0 0 0 1 |

| 0 0 1 0 | 0 0 1 1 |

| 0 0 1 1 | 0 0 1 0 |

| 0 1 0 0 | 0 1 1 0 |

| 0 1 0 1 | 0 1 1 1 |

| 0 1 1 0 | 0 1 0 1 |

| 0 1 1 1 | 0 1 0 0 |

Слід зазначити, що аналіз даних табл. 2.1 показує, що значення старшого розряду обох кодів збігається повністю, а інших розрядів − іноді збігається, іноді ні. Використовуючи стандартну методику синтезу з мінімізацією на картах Карно, можна вирішити пряме завдання: перетворення двійкового коду 8-4-2-1 (х 1, х 2, х 3, х 4) у код Грея (y 1, y 2, y 3, y 4).

Рішення зворотного завдання (перетворення коду Грея у двійковий код 8-4-2-1) більш складне, проводиться у два етапи й полягає:

а) в одержанні МДНФ (МКНФ);

б) у перетворенні їх до виду, що використає операцію ∑ mod 2 через співвідношення b= х 1  V

V  х 2.

х 2.

Рішення трохи спрощується, якщо перетворення функції коду Грея у двійковий код 8-4-2-1 відразу проводити на основі операції ∑ mod 2, при цьому на підставі аналізу табл. 2.2 виявити закономірність одержання y =ai від b4, b3, b2, b1 що можна виконати двома способами:

а) починаючи від старших розрядів b4,b3 і т.д. одержати вираження для y =a3, потім використовуючи a3 і b2 – для y =a2, далі використовуючи a2 і b1 – для y =a1;

б) розглянути карти Карно для функцій виходів a i (i =1, 2, 3) як об’єкти. Для пояснення висловленого на рис.2.9 наведені карти Карно для функцій виходів a3 і a2 (не для a1), де еквівалентом вхідних (х 1, х 2) змінних є a3, b2, а вихідної функції у =a2. Порівняння цих карт Карно між собою дозволяє переконатися в перетворенні карти Карно для a3 у карту для a2на основі співвідношення: a2 = a3 Å b2 = a3  V

V  b2.

b2.

Аналогічно можна виконати перетворення для вихідної функції у =a1 (використати як еквівалент вхідних х 1, х 2 змінні a2 і b1).

Рисунок 2.9 – Карти Карно для змінних a2 і a3

В роботі необхідно побудувати схему перетворювача: код Грея в 4-розрядний двійковий код (8-4-2-1), для чого треба використати двувходову схему ∑ mod 2 – наприклад, К155... (СНД) або її імпортний аналог − ІС типу 7486 і провести перевірку його функціонування

Варіант 8. Розробити схему пристрою контролю парності (непарності) при передачі даних.

Складність цифрових пристроїв (ЦП), ЦА визначає важливість моніторингу переданої/одержуваної цифрової інформації (авіаційно-космічні пристрої, військові системи, керування потужними енергоустановками, цифрові потоки Internet, телеметрія, наземні й супутникові канали зв’язку, дані банківських операцій, медичних приладів, ін.).

Мета, завдання моніторингу: запобігання, контроль і діагностика, виправлення помилок.

Додавання функцій моніторингу завжди пов’язане з надмірністю − збільшенням кількості пристроїв, часу обробки для одержання інформації більш високої якості.

Запобігання помилок. Вирішується якістю розробки пристроїв, застосуванням у них високоякісних елементів − цифрових схем, ліній зв’язку й пристроїв, що забезпечують задану величину ймовірності виникнення помилок - BER при фіксованих границях несприятливих впливів − коливань напруги живлення, температури, рівня зовнішніх перешкод, власних шумів, ін. умов. Для звичайних систем цифрового зв’язку величина BER менш ніж 10-9, для особливих типів − 10-12 і менша.

Контроль і діагностика. Завдання виявлення помилок вирішуються різними схемо технічними способами (див. нижче). Після цього ЦП за заданим алгоритмом забезпечує, наприклад, повторну передачу/прийом інформації (при виявленні помилки при передаванні/прийманні ЦП посилає запит на передачу/прийом блоку, у якому вона була). До схем контролю відносять: мажоритарні елементи, ∑ mod 2 і схеми з використанням кодів Хемінга.

Виправлення (маскування) помилок. ЦП на передачі/прийомі автоматично діагностує і (у деяких випадках) виправляє помилки. Одним з перевірених способів є n -кратне резервування каналу зв’язку (n − непарне число: 3, 5, 7,...) з виробітком сигналу мажоритарного голосування (тобто дані вважаються безпомилковими з тих i -каналів з n, по яких відсутній сигнал помилки; при цьому i ≥ (n+1)/2).

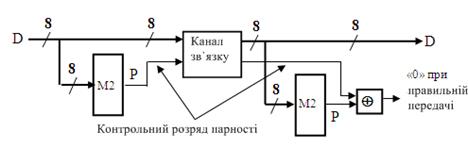

Рисунок 2.10 – Передача даних при перевірці на парність.

Найпростіший спосіб контролю (виявлення) непарної кількості помилок при передачі/прийомі даних полягає в передачі розряду перевірки на парність P пар. (непарність P непар.). На рис. 2.10 наведена спрощена схема контролю на парність 8-ми розрядного слова. У контрольний розряд (КР) парності (непарності) записується «0» («1»), якщо число одиниць в інформаційному слові парне (непарне) і навпаки, «1» («0») − у випадку непарного (парного) числа одиниць (якщо всі розряди Di приймають значення «0», те в КР записується «0»). При цьому загальна кількість переданих одиниць по каналу зв’язку, включаючи КР, завжди парне. На приймаючій стороні КР обчислюється тим же способом для розрядів Di і порівнюється з переданим КР. При розбіжності фіксується помилка передачі. Контроль на схемах ∑ mod 2 ефективний у ЦП, де ймовірність одиничної помилки набагато більша, ніж імовірність подвійної. Виправити помилку при цій системі контролю неможливо.

При виконанні завдання необхідно зробити:

- синтез блоку формування КР для 4-х розрядної шини Di;

- дослідження схеми 74280 (1533ИП5).

2015-09-06

2015-09-06 1814

1814