За формою зображення у просторі й часі коди бувають послідовними й паралельними. Послідовний код — це комбінація імпульсів (або їхніх еквівалентів) та пауз у часі (рис. 2.3, а) в одному просторовому елементі (проводі, радіолінії тощо). На папері коди записують в послідовній формі: кожному розряду — нове місце в різні моменти часу.

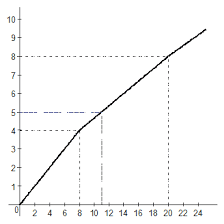

Час тривалості послідовного коду (рис. 2.3, а)

| t = nt 1 + nt 2 = n (t 1 + t 2), | (2.6) |

де t1 — довжина інформаційного сигналу (імпульсу); t2 — довжина паузи; n — довжина коду.

Якщо сума t1 + t2 дорівнює періоду імпульсів Т, то t = nT. При паралельному коді (рис. 2.3, б) його кожний елемент зображується окремим просторовим елементом (проводом, ланцюгом, лінією, радіолінією тощо). Час тривалості паралельного коду (рис. 2.3, б) має вигляд

| t = t 1 + t 2. | (2.7) |

Рис. 2.3. Послідовні й паралельні коди

Якщо t 1 + t 1 = Т, то t = T.

З порівняння виразів (2.6) і (2.7) випливає, що тривалість послідовного коду в n разів більша за тривалість паралельного коду, тобто паралельна форма коду має менший час передавання, але потребує великих просторових (апаратурних) витрат.

У СКК КІВ використовуються як послідовні, так і паралельні форми зображення кодів: під час сприйняття й передавання інформації використовуються послідовні коди, а під час зберігання й зображення — паралельні. Перетворення кодів однієї форми на іншу можна виконати на регістрах зсуву (рис. 2.4) й паралельних регістрах

(рис. 2.5, 2.6).

Рис. 2.4. Кодоперетворювач на регістрі зсуву

Перетворювач на регістрі зсуву містить вузол керування 1 і регістр зсуву 2. Вузол керування містить формувач початку перетворення 3, генератор імпульсів 4, тригер управління 5, кон’юнктор 6, лічильник 7, дешифратор 8. На вхід G (x) надходить послідовний код. При надходженні першого розряду коду на вході G (x) формувач 3 установлює тригер 5 в одиничний стан. Це забезпечує проходження синхронізувальних імпульсів з генератора 4 через кон’юнктор 6 на лічильник 7 і на вхід С регістра зсуву 2.

Під час надходження кожного синхронізувального імпульсу на вхід С регістра 2 в його перший (молодший) розряд записується інформація, яка надходить на його вхід V. Значення першого (молодшого) розряду записуються в другий (наступний) розряд. Лічильник 7 і дешифратор 8 забезпечують формування на виході кон’юнктора 6 кількості імпульсів, яка дорівнює довжині коду.

При збігу кількості імпульсів з довжиною n коду дешифратор 8 (в окремому випадку це один кон’юнктор, входи якого з´єднані з певними прямими й інверсними виходами лічильника 7) формує сигнал, яким тригер управління 5 і лічильник 7 приводяться у початковий стан. На виходах у 1, у 2, у 3 ,..., уn регістра 2 формується паралельний код. Перший елемент послідовного коду, який надходить на вхід V регістра 2, у паралельному коді знаходиться на виході уn, а останній — на

виході у 1.

Для перетворення паралельного коду, який міститься в регістрі 2, на послідовний необхідно на його вхід С подати n імпульсів. Ці імпульси формують вузол керування 1 після надходження керувального сигналу на вхід П формувача 3. Послідовний код формується на виході уn. З опису роботи перетворювача на регістрі зсуву випливає, що він забезпечує перетворення як послідовного коду в паралельний, так і паралельного в послідовний. Такий перетворювач є універсальним. Принциповою особливістю цього перетворювача під час роботи в режимі приймання (перетворення послідовного коду в паралельний) є те, що період надходження елементів коду (t = T) на вхід V регістра 2 має дорівнювати періоду синхронізувальних імпульсів, які надходять на вхід С регістра 2.

На рис. 2.5 наведено схему перетворювача послідовного коду на паралельний з використанням паралельного регістра.

Цей перетворювач містить вузол керування 1, регістр 2 і вузол комутації 9. Вузол керування 1 такий самий, як і в перетворювачі, зо

браженому на рис. 2.4. Відмінність полягає в тому, що дешифратор має n виходів. Регістр 2 являє собою набір DС- або RS- тригерів. Вузол комутації 9 містить набір з n кон’юнкторів. Перші входи всіх кон’юнкторів 9 з´єднані між собою і на них подається послідовний код G (x). Другі входи кон’юнкторів 9 з´єднані з відповідними виходами дешифратора 8. У перетворювачі частота надходження послідовного коду й частота генератора 4 є узгодженими (одинаковими). Під час надходження першого розряду коду на всі кон’юнктори вузла комутації 9 він надійде тільки на вхід S 1 регістра 2, тому що тільки на другому вході кон’юнктора 10 буде сигнал з виходу 1 дешифратора 8 Під час надходження другого розряду коду на кон’юнктори вузла комутації 9 він надійде тільки на вхід S 2 регістра 2 через кон’юнктор 11, тому що тільки на другому його вході буде сигнал з виходу 2 дешифратора 8 і т.д.

Паралельний код зберігається в регістрі 2 і формується на його виходах y 1, у 2 ,..., уn. Відмітною особливістю перетворювача є те, що він може забезпечувати запис будь-якого розряду послідовного коду в будь-який розряд регістра 2. Це досягається відповідним з´єднанням других входів кон'юнкторів 9 з виходами дешифратора 8. Недоліком цього перетворювача є те, що він тільки перетворює послідовний код на паралельний і не перетворює паралельний код на послідовний.

На рис. 2.6 зображено схему перетворювача паралельного коду на послідовний.

Рис. 2.6. Перетворювач паралельного коду на послідовний

Цей перетворювач містить вузол управління 1, вузол комутації 2 і диз'юнктор 3. Паралельний код надходить на перші входи кон'юнкторів вузла комутації 2, другі входи яких з´єднані з виходами дешифратора 8 вузла управління 1.

За наявності паралельного коду на входах y 1, у 2 ,..., уn і надходження сигналу пуску на тригер управління 5 імпульси з генератора 4 через кон'юнктор 6 надходять на лічильник 7.Змінення кодів на виходах лічильника 7 забезпечує через дешифратор 8 керуючі сигнали на виходах 1, 2,..., n вузла управління. Цим здійснюється послідовне підключення входів y 1, у 2 ,..., уn вузла 2 комутації через кон'юнктори 9, 10,..., (n + 8) і диз'юнктор 3 на вихід G (y), тобто перетворення паралельного коду на послідовний. Кінець перетворення забезпечується з´єднанням виходу n дешифратора 8 із входами R тригера управління 5 і лічильника 7. Перетворювач забезпечує тільки перетворення паралельного коду на послідовний.

Розглянуті кодоперетворювачі є елементами багатьох цифрових систем різного призначення.

2015-10-13

2015-10-13 3188

3188