| Входы | Выход | |||

| R | S | qt | Состояние qt+1 | Режим |

| Хранение | ||||

| Хранение | ||||

| Установка 0 | ||||

| Установка 0 | ||||

| Установка 1 | ||||

| Установка 1 | ||||

| ? | Запрещенное состояние | |||

| ? | Запрещенное состояние |

Содержание таблицы расшифровывается следующим образом. Элемент памяти может сохранять значение qt =0 или qt =1 в зависимости от установки ранее установленного состояния. При отсутствии входных сигналов на входах R и S (R=0 и S=0) значения qt +l в первой строке таблицы в точности повторяют значения qt. При поступлении сигнала R=l (сигнала установки «нуля») элемент независимо от своего состояния принимает значение, равное нулю, qt +l = 0. Если же на вход S поступает сигнал установки «единицы» (S=l), то qt +l=l независимо от предыдущего состояния qt. Одновременное поступление сигналов на входы R и S является запрещенной ситуацией, так как она может привести к непредсказуемому состоянию. В схемах формирования сигналов R и S должны быть предусмотрены блокировки, исключающие их совпадения, S=R=1.

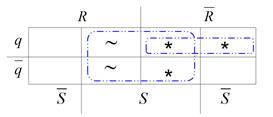

Для таблицы переходов может быть построена диаграмма Вейча (табл. 1.2).

Таблица 1.2

Диаграмма Вейча для таблицы переходов триггера

В этой таблице знаком «~» отмечены запрещенные комбинации входных сигналов и они могут быть использованы для упрощения логических зависимостей. Логическая зависимость, описывающая работу элемента памяти, принимает вид:

Для реализации полученной зависимости в базисе И-НЕ применим правило де Моргана и получим функцию

По данной зависимости можно построить схему элемента памяти — асинхронного RS-триггера. В этой схеме следует только соединить выход qt +1 со входом qt (рис. 1.1). Эта связь отмечена штриховой линией.

RS-триггер нашел широкое распространение в схемах ЭВМ. Одиночные триггеры этого типа часто используются в различных блоках управления. В асинхронных

RS-триггерах имеется один существенный недостаток, обусловленный самой логикой их построения, т.е. в них сигналы R и S должны быть разнесены во времени. Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS-, Т-, JK-, D-триггеры и целый ряд комбинированных RST-, JKRS-, DRS-триггеров [4].

Рис.◦1.1. Схема асинхронного RS-триггера: a — схема; б — обозначение на принципиальных электрических схемах; в — временная диаграмма

Прописные буквы в названиях триггеров обозначают:

- R (Reset — сброс) — вход установки триггера в нулевое состояние, Q = 0

- S (Set — установка) — вход установки триггера в единичное состояние, Q =1

- Т (Toggle —релаксатор) — счетный вход триггера

- J (Jerk — внезапное включение) — вход установки JK-триггера в единичное состояние, Q = l

- К (Kill — внезапное выключение) — Q = 0

- D (Delay — задержка) — вход установки триггера в единичное или нулевое состояние на время, равное одному такту

- С (Clock — часы) — вход синхронизирующих тактовых импульсов

На рис.◦1.2 показаны схемы синхронного однотактного (а) и двухтактного (б)

RS-триггеров.

а б

Рис. 1.2. Синхронные RS-триггеры

Синтез электрической функциональной схемы

Синтез состоит в построении функциональной электрической схемы по СДНФ из таблично-заданной функции, описывающей работу заданной схемы.

Порядок выполнения лабораторной работы

· изучить основные теоретические положения и описание лабораторной работы;

· оформить отчет по лабораторной работе;

В соответствие с заданием:

· составить таблицу истинности;

· написать СДНФ заданной функции;

· начертить схему электрическую функциональную в базисе Буля, Шеффера или Пирса;

Отчет должен содержать

Цель работы

Таблицу истинности

СДНФ, составленной по таблице истинности

Схемы электрические функциональные представленные в базисах: Буля, Пирса, Шеффера

Выводы о проделанной работе

2015-10-13

2015-10-13 1341

1341