Преобразование триггеров

Различные триггеры могут выполнять одинаковые функции за счет использования дополнительных связей.

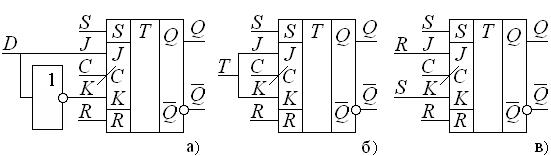

На основе JK -триггера можно получить любой другой триггер, например,синхронные D -триггер, T -триггер, RS –триггер с динамическими входами C (рис. 12, а, б, в).

Рис. Синхронные триггеры с динамическими входами:

а – D -триггер, б – T -триггер, в – RS –триггер

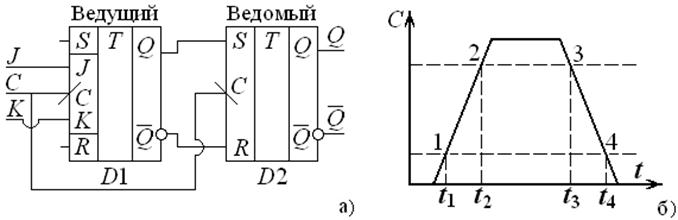

По принципу построения различают одноступенчатые триггеры, рассмотренные выше, и двухступенчатые триггеры. Последние состоят из двух ячеек памяти – последовательно включенных триггеров (рис. 13). Триггер D 1 имеет тактовый вход C, который реагирует на передний фронт импульса синхронизации C, а входы триггера D 2 реагирует на задний фронт этого импульса. Вначале информация записывается в первую ступень D 1, а затем переписывается во вторую D 2 и появляется на выходе.

Двухступенчатый триггер обозначается вместо символа T символами TT, управляется по обоим фронтам, реализуются по схеме «ведущий-ведомый» (вход C как у D 1).

Рис. MS -триггер:

а – принципиальная схема; б – временные диаграммы работы

Последовательность работы MS -триггера:

- на интервале времени t 1 – t 2 ведущий триггер D 1 сохраняет поступающую в него информацию, ведомый триггер D 2 отключен от D 1;

- на интервале времени t 2 – t 3 оба триггера отключены;

- на интервале времени t 3 – t 4 ведущий триггер D 1 отключен от информационных сигналов, ведомый триггер D 2 сохраняет поступающую в него информацию от D 1.

Двухступенчатые триггеры могут состоять из собственно триггера и динамической промежуточной ячейки памяти. Они управляются только одним фронтом тактового импульса – передним фронтом из 0 в 1.

Данные MS -триггеры используются в цифровых устройствах, где при поступлении тактового сигнала информация записывается в первый триггер и не должна проходить сразу во все триггеры, подключенные последовательно за первым (регистры).

Чтобы предотвратить такое сквозное прохождение сигнала, для одноступенчатых динамических триггеров нужно использовать импульсы синхронизации с очень крутыми (короткими по времени) фронтами.

Тогда благодаря задержке переключения первого триггера, подключенный к нему триггер успеет перейти в режим хранения до поступления на его вход новой информации, т.к. сигнал на тактовом входе, общий для всех триггеров, уже успеет переключиться в постоянное значение и отключит этот триггер.

Триггеры с MS структурой являются динамическими. Для исключения сбоев в работе, у этих триггеров нормируется минимально допустимый промежуток времени до появления фронта сигнала C, когда на входе данные не должны изменяться.

Также указывается аналогичный интервал – время удержания данных, после завершения фронта тактового импульса.

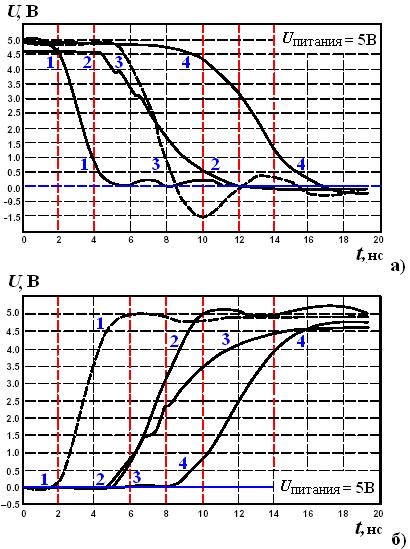

На рисунке представлены временные диаграммы передних и задних фронтов переключений различных типов логических элементов, полученные экспериментально.

Рис. Графики фронтов цифровых сигналов: а – заднего; б - переднего

На логические элементы, изготовленные по различной технологии, одновременно поступает входной сигнал в момент времени t =0 и начинается их переключение. График 1 соответствует эмиттерно-связанной логике (ЭСЛ); график 2: транзисторно-транзисторной логике с диодами Шотки (ТТЛШ); график 3: транзисторно-транзисторной логике (ТТЛ); график 4: логике на комплементарных полевых транзисторах метал-окисел-полупроводник (КМОП). Из временных диаграмм следует, что всякое переключение логических элементов сопровождается переходным процессом. Если тактовый сигнал появится во время, пока этот процесс не закончился, то возможна ошибка считывания информации.

2014-02-17

2014-02-17 4451

4451