Принцип действия регистров, срабатывающих по фронту тактового сигнала, ничем не отличается от принципа действия D-триггера.

По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С. То есть если триггер запоминает один сигнал (один двоичный разряд, один бит), то регистр запоминает сразу несколько (4, 6, 8, 16) сигналов (несколько разрядов, битов). Память регистра сохраняется до момента выключения питания схемы.

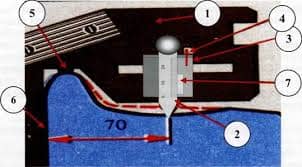

На Рис.4.11. представлена схема регистра на D триггерах, в котором данные в прямом коде подаются на входы D1,D … Dm.

Запись информации осуществляется фронтом сигнала Тзап (тактовый командный импульс) одновременно поступающего на входы С всех триггеров.

|

| Рис.4.11. Запись информации параллельным кодом |

На Рис.4.12. представлена схема регистра на JK триггерах. В данной схеме данные подаются парафазным кодом (прямой код D1,D … Dm – на вход J, обратный кода – на вход К).

|

| Рис.4.12. Запись информации парафазным кодом |

Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0... Dm новой цифровой комбинации (информации) при поступлении определенного уровня (регистр на асинхронных триггерах или запись осуществляется по установочным входам триггера) или фронта синхросигнала (синхроимпульса) Тзап=С на вход «С» регистра (синхронные триггера с записью по информационным входам).

Количество разрядов записываемой цифровой информации определяется разрядностью регистра, а разрядность регистра, в свою очередь, определяется количеством триггеров, образующих этот регистр.

В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры.

Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, тактовые входы которых присоединяют к шине синхронизации.

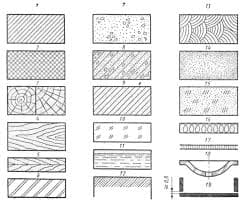

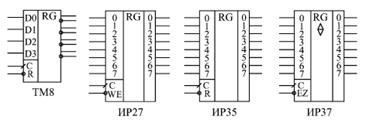

В стандартные серии входит несколько типов параллельных регистров, срабатывающих по фронту (Рис. 4.12).

Рис.4.12. Параллельные регистры стандартных серий, срабатывающие по фронту

Различаются они количеством разрядов, наличием или отсутствием инверсных выходов, наличием или отсутствием входа сброса (–R) или разрешения записи (–WE), а также типом выходных каскадов (2С или 3С) и, соответственно, наличием или отсутствием входа разрешения –EZ. Иногда на схемах тактовый вход С обозначается WR - сигнал записи в регистр.

В качестве примеров в табл. 4.3 приведена таблица истинности регистра ИР27, а в табл. 4.4 - регистра ИР37. По переходу тактового сигнала С из 0 в 1 (положительный фронт) оба регистра записывают в себя входную информацию.

| Таблица 4.3 Таблица истинности регистра ИР27 | Таблица 4.4 Таблица истинности регистра ИР37 | ||||||||

| Входы | Выходы | Входы | Выходы | ||||||

| -WE | C | D | Q | -EZ | C | D | Q | ||

| 0→1 | 0→1 | ||||||||

| 0→1 | 0→1 | ||||||||

| Х | Не меняется | X | Не меняется | ||||||

| Х | Не меняется | X | Не меняется | ||||||

| Х | Х | Не меняется | X | X | Z |

Все регистры, имеющие выход с тремя состояниями, обеспечивают повышенную нагрузочную способность. Задержка переключения регистров примерно соответствует задержке переключения триггеров.

Одно из основных применений регистров состоит в хранении требуемого кода в течение нужного времени.

Регистры могут также применяться в составе вычислителей, выполняя функцию накопителя результата вычисления.

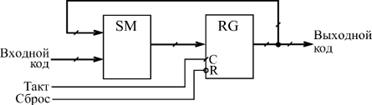

Рассмотрим пример схемы такого вычислителя – накапливающий сумматор..

В самом названии схемы отражена ее функция: она суммирует и накапливает результат. Накапливающий сумматор (Рис. 4.13) состоит из сумматора и выходного регистра, охваченных обратной связью.

То есть на один вход сумматора подается код с выходов регистра, а на другой вход - входной код. В результате с каждым следующим фронтом тактового сигнала в регистр записывается код суммы входного кода с предыдущим содержимым регистра, с

Рис. 4.13. Структура накапливающего сумматора

предыдущей суммой. Например, если входной код равен 3, а в регистре записан код 6, то в следующем такте в регистр будет записан код 9 (то есть 6 + 3), в следующем такте - код 12 (то есть 9 + 3) и т.д. Получается, что на выходе накапливающего сумматора формируется равномерно увеличивающийся двоичный код, и шаг этого увеличения можно менять. В данном случае удобно применять регистр со сбросом, например, ИР35.

2015-10-14

2015-10-14 2007

2007