Обратим внимание также на аспект обеспечения правильности функционирования автомата при записи кода S0, S1,…, Sp на Pг a(t + 1) через шифратор CD. Как видно из рис. 61, для установки Pг a(t + 1) все нулевые входы триггеров объединены в шину, управляемые сигналом с10. Это удобно для установки триггеров S0, S1,…, Sp в «0» состояние до начала работы автомата. Однако при таком способе «обнуления» для последующих тактов записи кодов по сигналу τ до появления кода S0, S1,…, Sp на входе Pг a(t + 1) нужно также подать сигнал с10. Т.е. для каждого τ и  сигнал с10 должен появиться ранее сигнала τ.

сигнал с10 должен появиться ранее сигнала τ.

Это условие можно выполнить за счет задержки сигналов τ и  до подачи их на схемы «И» 5, 6. Тогда сразу после схемы задержки (например, две последовательно включенных схемы НЕ) сигнал подается на с10. При этом вся остальная схема не меняется. Есть и другие пути решения этой «проблемы», которые рассматриваются не на структурном, а на более детальном уровне проектирования.

до подачи их на схемы «И» 5, 6. Тогда сразу после схемы задержки (например, две последовательно включенных схемы НЕ) сигнал подается на с10. При этом вся остальная схема не меняется. Есть и другие пути решения этой «проблемы», которые рассматриваются не на структурном, а на более детальном уровне проектирования.

На современной микроэлектронной базе автоматы управления могут быть реализованы на элементах средней, большой и сверхбольшой интеграции.

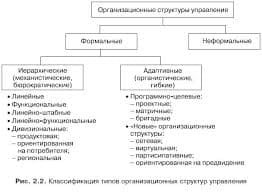

Рассмотрим структурные компоненты (подсистемы) в автомате управления в соответствии с моделью Ю.Ф. Мухопада.

Ф – функциональная подсистема, представляет собой комплекс блоков, предназначенных для формирования выходных сигналов { c }. В данном случае это комбинационная схема F1 и DC (1);

И – информационная подсистема представлена в виде регистров памяти автомата Pг a(t) и Pг a(t + 1) с парафазной связью и блоков преобразования кодов DC (2) и CD при унитарном кодировании. При двоичном кодировании DC(2) и CD отсутствуют.

А – адресная подсистема представлена устройством F2, вычисляющим новый адрес (код состояния) в виде унитарного кода f0, f1, …, fi по коду (адресу) в виде {Z} и { α }. При двоичном кодировании вычисляется код Z(t + 1) вместо { f }.

У – управляющая подсистема, в автомате представлена в виде генератора импульсов (ГИ), управляющего триггера (УП), двух схем «И» (5), (6) и двух схем «ИЛИ» (3), (7). ГИ для τ – типовая БИС, формирование  – тривиально.

– тривиально.

Л – логической подсистемы собственно в автомате нет, ее функции выполняет операционное устройство (ОУ).

Реализация подсистем Ф, И, А, У, Л определяется той ориентацией, которая будет выбрана по элементной базе.

На элементной базе малой и средней интеграции реализация подсистемы У не представляет затруднений. Для подсистем И выпускаются в виде единой микросхемы как DC, CD, так и единая микросхема памяти с 4 двойными триггерами и с парафазной связью между ними. Остается определить подсистемы Ф и А.

2015-10-22

2015-10-22 361

361