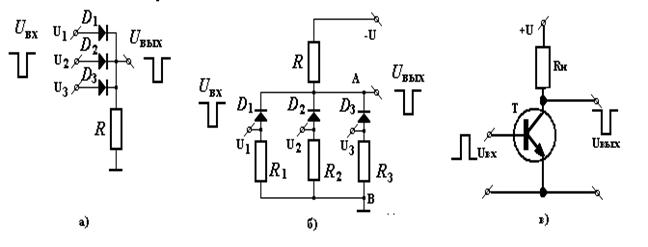

На рис.11.1а представлена схема ИЛИ, выполненная на диодах. Управляющий сигнал на выходе появляется при поступлении сигнала ИЛИ на один, ИЛИ на два других входа, одновременно или вместе.

Таблица 8.1 – Основные законы алгебры логики

| № | Название | Выражение |

| 1. | Закон универсального множества | 1V X 1V X 2V X 3… V X n=1 |

| 2. | Закон нулевого множества | 0L X 1L X 2L X 3… L X n=0 |

| 3. | Законы повторения | X V X V X V X … V X = X X L X L X L X … L X = X |

| 4. | Закон многократной инверсии |  и т.д. и т.д.

|

| 5. | Переместительный закон | X1VX2= X 2V X 1, X1LX2= X 2L X 1 |

| 6. | Сочетательный закон | X 1L(X 2L X 3)= (X 1L X 2)L X 3= X 2L(X 1L X 3) |

| 7. | Законы дополнительности |

|

| 8. | Распределительный закон | X 1L X 2V X 3= (X 1V X 2)L(X 2 V X 3) X 1V X 2 L X 3= (X 1L X 2)V(X 2L X 3) |

| 9. | Законы поглощения | X 1L X 1V X2 = X 1, X 1L X 1L X2 = X 1 |

| 10. | Законы склеивания | X 1L X 2V X 1L  = X 1

(X 1L X 2)V( = X 1

(X 1L X 2)V( )= X 1 )= X 1

|

| 11. | Законы отрицания: Пирса Шеффера |

|

Сигнал той же полярности появляется на выходе схемы ИЛИ в том случае, когда хотя бы на одном из входов: - ИЛИ на U1 ИЛИ на U2 ИЛИ на U3 будут логические сигналы (единицы).

На рис.8.1б приведена схема И, собранная на диодах. При поступлении сигнала только на один вход запирается соответствующий диод, а другие диоды остаются открытыми, в силу чего сопротивление между точками А и В остается малым и сигнал на выходе отсутствует. Таким образом, на выходе схемы И сигнал появится только тогда, когда на всех входах: И на U1 И на U2 И на U3 будут логические сигналы (единицы).

Логическая схема НЕ выполняется на транзисторе (рис.8.1в), или инвертирующем операционном усилителе. На выходе этой схемы сигнал инверсный тому, который присутствует на входе. Если на входе присутствует логическая единица (высокий сигнал), то на выходе - логический нуль (низкий сигнал) и наоборот.

Рассмотренные схемы на диодах имеют существенный недостаток, связанный с ослаблением сигнала при работе, что затрудняет осуществление каскадных соединений различных логических цепочек. От этого недостатка свободны схемы, дополненные транзисторами, выполняемыми по интегральным технологиям. Современная промышленность выпускает интегральные логические микросхемы с широкой гаммой логики.

Рассмотренные схемы на диодах имеют существенный недостаток, связанный с ослаблением сигнала при работе, что затрудняет осуществление каскадных соединений различных логических цепочек. От этого недостатка свободны схемы, дополненные транзисторами, выполняемыми по интегральным технологиям. Современная промышленность выпускает интегральные логические микросхемы с широкой гаммой логики.

Рисунок 8.1 – Исполнение логических элементов.

Для двух переменных имеют место 16 логических функций, математические соотношения и графические обозначения которых приведены в таблице 8.2.

Графическое изображение логических элементов осуществляется в виде прямоугольников, внутри которых ставятся условные символы: & - элементы с выполнением операции конъюнкции, 1 - элементы с выполнением операции дизъюнкции, =1 - исключающее ИЛИ.

С левой стороны прямоугольников изображают входы, а с правой - выходы (таблица 8.2). Входы или выходы, помеченные кружочками, соответствуют инвертированию сигнала. Входы или выходы, не несущие логической информации, например, входы расширения или питания, помечают крестиком х. На основе логических элементов может быть построена электронная схема любой сложности.

Таблица 8.2 – Некоторые функции двух переменных

| Логическое выражение | Условное обозначение | |

| Конъюнкция Z = X L Y |

| |

| Исключающее ИЛИ Z = X Å Y |

| |

| Дизъюнкция Z = X V Y |

| |

Функция Пирса

|

| |

Логическая равнозначность

|

| |

Инверсия

|

| |

Функция Шеффера

|

|

Переключательной функцией в алгебре логики называют функцию, представляющую собой зависимость выходного сигнала от входных, имеющих место в данный момент времени. Для составления переключательных функций вначале составляют таблицы истинности (таблица 8.3). Столбцы в таблице истинности обозначают наименованиями входных и выходных переменных, а в строках записывают всевозможные сочетания входных и выходных сигналов в соответствии со словесным описанием алгоритма работы синтезируемых устройств.

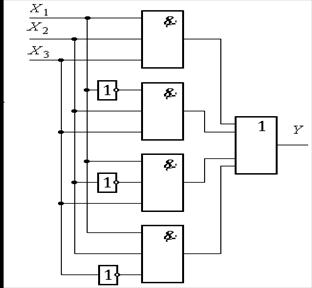

Покажем это на примере мажоритарного элемента (рис.8.2), имеющего три входа X 1, X 2, X 3 и один выход Y. Единичный сигнал на выходе у такого элемента должен появится в том случае, если на двух или на трёх входах имеют место единичные сигналы. В противном случае на выходе должен быть нуль. Ниже представлена таблица истинности для мажоритарного элемента. На основании таблицы истинности переключательная функция может быть записана в следующем виде:

. (8.1)

. (8.1)

Для построения мажоритарного элемента требуется: три инвертора для получения инверсных сигналов  четыре трёхвходовых элемента 3И и один четырёхвходовый элемент 4ИЛИ (рис.8.2).

четыре трёхвходовых элемента 3И и один четырёхвходовый элемент 4ИЛИ (рис.8.2).

В большинстве случаев, применяя основные законы булевой алгебры, переключательные функции удаётся минимизировать, что в свою очередь снижает аппаратные затраты на построение устройств. Так, например, применяя закон дополнительности, формулу (8.1) можно привести к следующему, более простому, виду:

. (8.2)

. (8.2)

Для построения того же мажоритарного элемента по формуле (8.2) требуется всего три двухвходовых элемента 2И и один трёхвходовый элемент 3ИЛИ.

Минимизация логических функций осуществляется с целью снижения аппаратных затрат при построении комбинационных устройств. Основными критериями при минимизации являются: сокращение числа членов в переключательной функции, числа входов у используемых логических элементов, числа межсхемных соединений, а также числа логических операций, необходимых для выполнения функции. При минимизации результирующее действие переключательных функций сохраняется постоянным. Для целей минимизации переключательных функций, имеющих до трёх переменных, используют аналитические методы с применением основных законов алгебры логики.

Таблица 8.3 – Таблица истинности

для мажоритарного элемента

| X 1 | X 2 | X 3 | Y |

Рисунок 8.2 – Мажиротарный элемент

2014-01-31

2014-01-31 871

871