Задание 1. Исследование работы D-триггера в статическом режиме

Собрать схему в пакете EWB, которая представлена на рис. 2.1.

Рисунок 2.1 – Схема D-триггера

Задание 2. Собрать D-триггер, который имеет следующую внутреннюю структуру (рис.2.2).

Рисунок 2.2 – Внутренняя структура D-триггера

Задание 3. Снять временную диаграмму этого триггера.

Для создания сложного элемента («макроса») необходимо выделить те элементы, которые он будет включать (см. рис.3.3). Далее выбрать меню " Circuit ® Subcircuit " (или нажать Ctrl+B). Появится следующие диалоговое окно (рис. 2.3), где необходимо:

1 – ввести имя элемента (SZ);

2 – создать элемент ввести его в схему;

3 – отменить.

Рисунок 2.3 –– Создание макроса для D-триггера

Задание 4. Исследование работы D-триггера в динамическом режиме.

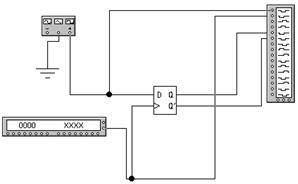

Собрать схему в пакете EWB, которая указана на рис. 2.4:

Рисунок 2.4 – Подключения D-триггера

С помощью объекта Генератор Импульсов (ГИ) на D-вход подать прямоугольные сигналы со следующими параметрами:

A= 4 В, f= 2 кГц, а на вход синхронизации с помощью объекта Генератор Сигналов – следующие:

T = 10 кГц.

С помощью объекта ЛА получить временную диаграмму.

Задание 5. Исследование работы асинхронного JK-триггера в статическом режиме.

Собрать схему в пакете EWB, которая представлена на рисунке 2.5:

Рисунок 2.5 – Схема JK-триггера

Задание 6. С помощью ЛА построить таблицу состояний (ТС), привести временную диаграмму.

Задание 7. Исследовать работу двухступенчатого JK-триггера в статическом режиме.

Создать свой «макрос» одноступенчатого JK-триггера с именем “jk” для схемы, представленной на рис. 2.6.

Рисунок 2.6 – Одноступенчатый JK-триггер

Собрать схему двухступенчатого JK-триггера, используя созданный «макрос» (рис. 2.7).

Рисунок 2.7 – Двухступенчатый JK-триггер

Исследовать этот JK-триггер (привести временную диаграмму).

Задание 8. Исследовать работу двухступенчатого JK-триггера в динамическом режиме.

Собрать схему в пакете EWB, которая представлена на рисунке 2.8.

Рисунок 2.8 – Двухступенчатый JK-триггер

Исследовать JK-триггер, который работает в режиме T-триггера (J=K=1). Для этого на синхровход подать прямоугольные сигналы со следующими параметрами (с помощью ГИ): A = 4 В, f = 10 кГц,

tu = 50 мкс.

Снять осциллограмму с входов и выходов.

Задание 9. Собрать D-триггер на основе JK-триггера и исследовать его работу.

Рисунок 2.9 – D-триггер на основе JK-триггера

Привести временную диаграмму функционирования данного D-триггера.

Вопросы для самоконтроля

1. Каким уравнением описывается работа D-триггера?

2. Составить таблицу состояний D-триггера.

3. Нарисуйте схему определенного преподавателем D-триггера.

4. Нарисуйте условное графическое изображение определенного преподавателем объекта D-триггера.

5. Классификация схем D-триггеров.

6. Объясните влияние помех на информационном входе D-триггера.

7. Определите основные динамические характеристики для определенного преподавателем D-триггера.

8. Как на базе D-триггера с прямым динамическим управлением построить D-триггер с обратным динамическим управлением?

9. Как построить D-триггер на базе JK-триггера?

10. Как построить D-триггер на базе RS-триггера?

11. Нарисуйте временную диаграмму с расчетом задержек логических элементов для определенного преподавателем D-триггера.

12. Различия между D- и DV- триггерами

13. Нарисовать таблицу состояний JK-триггера.

14. Нарисовать схему и объяснить принцип работы заданного преподавателем JK-триггера.

15. Принцип создания схем JK-триггеров на базе синхронных JK-триггеров

16. Почему в схемах асинхронных JK-триггеров используются линии задержки?

17. Определите основные динамические характеристики заданного преподавателем JK-триггера.

18. Нарисуйте условное графическое изображение заданного преподавателем JK-триггера.

19. Объясните причины влияния помех на информационных входах на состояние JK-триггера (на примере схемы заданной преподавателем).

20. Сравните по помехоустойчивости JK-триггер со статическим и динамическим управлением.

21. Как происходит управление состоянием триггера по асинхронным входам S, R? Особенности такого управления.

22. Как построить на базе JK-триггера триггеры RS, D, T типов?

23. Классификация JK-триггеров.

24. Определите нагружаемую способность заданного преподавателем JK-триггера.

25. Нарисуйте временные диаграммы (с расчетом задержек логических элементов) заданного преподавателем JK-триггера.

Лабораторная работа 3

CДВИГАЮЩИЕ РЕГИСТРЫ

Цель занятия

Ознакомление с работой регистров, которые сдвигают на примере регистров со сдвигом вправо с помощью инструментальных средств цифровой части пакета EWB: генератора слов (ГС), логический анализатор (ЛА), логический преобразователь (ЛП), вольтметр.

2018-03-09

2018-03-09 131

131