Рассмотрение архитектуры IA-32 начнем с микропроцессора i486. В нем впервые появились те блоки, которых не было на кристалле первого 32-разрядного микропроц-а i386, - кэш-память и процессор обработки чисел с плавающей точкой. Именно его архитектуру можно рассматривать как базовую для IA-32. Структура i486 на рис.

Процессор обработки чисел с фиксированной точкой содержит 32-разрядное АЛУ и блок регистров общего назначения. АЛУ предназначено для обработки двоичных чисел длиной 1, 2 или 4 байта без знака или со знаком, а также двоично-десятичных чисел, не превышающих 99. Двоичные числа со знаком представляются в дополнительном коде. Блок регистров общего назначения содержит восемь 32-разрядных регистров, часть из которых допускает 16- и 8-разрядное обращение.

Процессор обработки чисел с плавающей точкой состоит из 80-разрядного АЛУ, блока из восьми 80-разрядных регистров общего назначения, а также управляющих регистров. Главным образом он предназначен для обработки чисел с плавающей точкой, но также используется для обработки целых чисел со знаком длиной 8 байт и двоично-десятичных чисел величиной от 100 до 99…9 (18 цифр). На первых этапах развития SIMD-обработки регистры FPU использовались для хранения операндов, представленных в новых форматах.

|

|

|

Блок управления памятью (Memory Management Unit - MMU) состоит из двух основных блоков в соответствии с организацией памяти. В общем случае память в микропроцессоре делится на сегменты, которые, в свою очередь, делятся на страницы. В соответствии с этим, MMU содержит блок сегментации (или блок сегментного преобразования адреса) и блок страничного преобразования, в состав которого входит буфер ассоциативной трансляцииадресов страниц (TLB). Кэш-память представляет собой промежуточную ступень между ОП и регистрами МП и предназначена для хранения наиболее часто используемой инф-ы.

В состав блока управления входят:

- собственно устр-во управления, т.е. та классическая схема, которая под действием кода команды вырабатывает набор управляющих сигналов, поступающих на разные узлы как самого микропроцессора, так и на блок интерфейса внешней шины;

- управление защитой памяти: обеспечивает аппаратную защиту программ и данных при управлении памятью и по привилегиям;

- блок управления предвыборкой команд: реализует опережающее заполнение буфера команд, представляющего собой некоторую буферную память. Буфер команд имеет емкость 32 байта и заполняется командами из следующих ячеек памяти команд по мере своего освобождения. Этим обеспечивается ускорение обработки микропроцессором следующей команды. Данный блок подвергался, пожалуй, наиболее существенным переработкам по мере развития архитектуры IA-32 - причина в широком последующем использовании конвейерной организации работы МП и связанной с этим необходимости постоянного совершенствования блока предсказания адреса следующей команды.

Блок интерфейса внешней шины осуществляет электрическое согласование параметров внутренней магистрали с сигналами внешних магистралей, формирование необходимых сигналов на внешнюю магистраль и прием сигналов извне. Внешняя магистраль микропроцессора состоит из шины адреса, шины данных и сигналов управления:

|

|

|

- шина данных имеет ширину 32 разряда;

- 32-разрядный адрес передается по 34-разрядной шине А31...А2+(B3,B2,B1,B0). Чтобы с минимальными потерями согласовывать 32-разрядную шину данных с передачей данных меньшей разрядности, младшие разряды адреса (А1 и А0) передаются в дешифрированном виде (B3, B2, B1, B0). Они показывают, какие байты из 32-разрядной шины данных в данный момент реально востребованы: 1 байт, 2 младших байта, 2 старших байта либо все 32 разряда данных;

- шина управления - 32-разрядная. По ней передаются сигналы записи и чтения ОП и внешних устр-в, сигналы запросов прерываний, прямого доступа к памяти и т. д.

Особый интерес представляют три режима работы микропроц-а: реальный, защищенный и режим виртуального МП i8086. В реальном режиме обеспечивается совместимость на уровне объектных кодов с микропроцессором i8086 и микропроцессором i286, работающем в реальном режиме. В этом режиме архитектура 32-разрядного микропроцессора почти полностью идентична архитектуре 16-разрядного МП. Для программиста же он вообще представляется как МП i8086, выполняющий написанные программы с большей скоростью и обладающий расширенной системой команд и регистрами. Благодаря этим качествам фирма Intel сохранила прежних клиентов, которые хотели модернизировать свои системы, не отказываясь от имевшегося задела в области программного обеспечения, и привлекла тех, кому изначально требовалась высокая скорость обработки информации.

Одно из основных ограничений реального режима было связано с предельной емкостью адресуемой памяти, равной 1 Мбайт. От него свободен защищенный режим, позволяющий воспользоваться всеми преимуществами архитектуры нового МП. Размер адресного пространства в этом случае увеличивается до 4 Гбайт, а общий объем поддерживаемого адресного пространства - до 64 терабайт (1 Тбайт = 240 байт). МП, работающие в защищенном режиме, обладают более высоким быстродействием и возможностями организации истинной многозадачности.

Режим виртуального МП открывает возможность одновременного исполнения прог., написанных для МП i8086, i286 и i386. Емкость памяти, адресуемой микропроц-ом, не ограничена значением 1 Мбайт ® можно формировать несколько виртуальных сред i8086.

Достоинства и недостатки использования сегментированного адресного пространства. Структура логического адреса в сегментированном адресном пространстве универсального 32-разрядного микропроцессора. Селектор, дескриптор сегмента, смещение. Назначение и структура таблиц дескрипторов. Формирование линейного и физического адресов в сегментированном адресном пространстве.

Схема распределения памяти между задачами сводится к разделению свободной памяти на несколько непрерывных разделов по числу задач. Каждый раздел характеризуется началом и длиной. Это разбиение может быть статическим (фиксированным) или динамическим. При статическом разбиении памяти происходит разделение ОП на фиксированное число разделов. В каждом разделе в каждый момент времени может находиться одна программа. При недостаточном объёме памяти для размещения заданного количества разделов задача находится в режиме ожидания освобождения памяти. Недостатком такой организации распределения памяти является фрагментация (часть памяти раздела, порой значительная, не используется и её использование не представляется возможным). Динамическим называется такое распределение памяти, при котором каждое отображение выбирается непосредственно в ходе вычислительного процесса, исходя из предыдущего отображения. К такому распределению относятся разрывные методы распределения памяти. Они не требуют непрерывных областей пространства для размещения задачи, но они требуют для реализации соответствующей аппаратной поддержки в виде относительной адресации. К разрывным методам относятся Сегментная, страничная и сегментно-страничная организации памяти

|

|

|

В основе сегментной модели памяти лежит разделение ее на независимые адресные пространства переменной длины - сегменты. Для программы адресное пространство разделено на блоки смежных адресов, называемых сегментами, а программа может обращаться только к данным, находящимся в этих сегментах. Внутри сегментов применяется линейная адресация, то есть программа может обращаться к байту 0, байту 1 и т. д. Такая адресация осуществляется относительно начала сегмента, и физический адрес, ассоциируемый, например, с программным адресом 0, по существу, скрыт от программиста. Этот подход к управлению памятью опирается на тот факт, что программы обычно логически разделяются на области (сегменты) кода, данных и стека. Каждый сегмент имеет свое целевое назначение. Каждая задача имеет непосредственный доступ к трем основным сегментам: кода, данных и стека, определяемых сегментными регистрами CS, DS и SS соответственно, и к трем дополнительным сегментам данных, определяемых сегментными регистрами ES, FS, GS. Описания этих сегментов содержатся в их дескрипторах. Любая программа, независимо от уровня ее привилегий, не может обращаться к сегменту до тех пор, пока он не описан с помощью дескриптора, а сам дескриптор не помещен в таблицу дескрипторов.

В основе сегментной модели памяти лежит разделение ее на независимые адресные пространства переменной длины - сегменты. Для программы адресное пространство разделено на блоки смежных адресов, называемых сегментами, а программа может обращаться только к данным, находящимся в этих сегментах. Внутри сегментов применяется линейная адресация, то есть программа может обращаться к байту 0, байту 1 и т. д. Такая адресация осуществляется относительно начала сегмента, и физический адрес, ассоциируемый, например, с программным адресом 0, по существу, скрыт от программиста. Этот подход к управлению памятью опирается на тот факт, что программы обычно логически разделяются на области (сегменты) кода, данных и стека. Каждый сегмент имеет свое целевое назначение. Каждая задача имеет непосредственный доступ к трем основным сегментам: кода, данных и стека, определяемых сегментными регистрами CS, DS и SS соответственно, и к трем дополнительным сегментам данных, определяемых сегментными регистрами ES, FS, GS. Описания этих сегментов содержатся в их дескрипторах. Любая программа, независимо от уровня ее привилегий, не может обращаться к сегменту до тех пор, пока он не описан с помощью дескриптора, а сам дескриптор не помещен в таблицу дескрипторов.

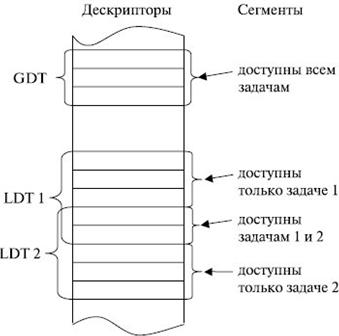

Дескрипторы хранятся либо в глобальной таблице дескрипторов (Global Descriptor Table - GDT), либо в локальных таблицах дескрипторов (Local Descriptor Table - LDT). В GDT содержатся дескрипторы сегментов, которые доступны всем активным задачам, имеющимся в системе на данный момент. GDT может содержать любые дескрипторы сегментов, за исключением дескрипторов прерываний и ловушек. Обычно GDT включает дескрипторы сегментов кодов и данных операционной системы, сегментов состояния задач и дескрипторы сегментов, содержащих локальные таблицы дескрипторов. МПС имеет единственную GDT. Локальная таблица дескрипторов LDT используется для хранения дескрипторов, доступных только данной задаче. Их количество определяется количеством активных задач в системе.

|

|

|

С точки зрения расположения в памяти локальные таблицы дескрипторов представляют собой обычные сегменты. Они могут накладываться друг на друга, частично пересекаться. Это приводит к тому, что отдельные сегменты, описанные дескрипторами в своих LDT, могут разделяться несколькими задачами (рис.).

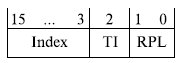

Для нахождения дескриптора в таблице дескрипторов используется селектор, который содержится в одном из сегментных регистров. Селектор представляет собой 16-разрядное слово, которое разбито на 3 поля:

Для нахождения дескриптора в таблице дескрипторов используется селектор, который содержится в одном из сегментных регистров. Селектор представляет собой 16-разрядное слово, которое разбито на 3 поля:

· TI (Table Indicator - индикатор таблицы ) показывает, к какой таблице идет обращение: TI = 0 - дескриптор находится в глобальной таблице дескрипторов GDT, TI = 1 - в локальной таблице LDT;

· Index: поле индекса - номер дескриптора в соответствующей таблице дескрипторов;

· RPL (Request privilege level - уровень привилегий запроса ). При обращении сравнивается с полем DPL в байте доступа дескриптора.

Обращение разрешается, если уровень привилегий запроса не ниже, чем уровень привилегий дескриптора.

Макс. количество дескрипторов, находящихся в таблице дескрипторов, определяется длиной поля Index селектора и = 213. Т.к. каждый дескриптор имеет длину 8 байт, максимальный объем любой таблицы дескрипторов составляет 216 байт. Каждая из таблиц дескрипторов имеет регистр (GDTR для глобальной таблицы и LDTR для локальной), определяющий ее положение в памяти. Регистр GDTR содержит 48 разрядов, из которых 32 задают базовый адрес глобальной таблицы дескрипторов, а 16 указывают ее объем в байтах (границу таблицы). Для определения положения дескриптора относительно начала таблицы его номер (поле Index селектора) умножается на 8, то есть реально сдвигается на три разряда влево, так как длина дескриптора составляет 8 байт. Если селектор обращается к дескриптору, содержащемуся в таблице GDT (при TI = 0 в селекторе), то полученное смещение сравнивается с хранящейся в GDTR границей таблицы. Если нарушения границы нет, то смещение прибавляется к содержащемуся в GDTR базовому адресу, в результате чего образуется физический адрес выбираемого дескриптора.

Нулевой дескриптор в GDT является пустым, не используемым. Селектор с нулевым значением разрядов 2….15 называется нуль-индикатором. Он обеспечивает обращение к нулевому дескриптору GDT. Так как этот дескриптор не используется, то при обращении к нему происходит прерывание. Одно из возможных применений пустых селекторов заключается в следующем. Перед инициированием задачи операционная система может загрузить в регистры DS и ES пустые селекторы. Если в последующем не инициализи-ровать эти регистры, то адресация памяти через них вызовет особый случай (прерывание). Загрузка в LDTR пустого селектора, для которого поле Index = 0, допустима. Такая операция сообщает процессору о том, что в задаче не будет использоваться локальная дескрипторная таблица. Это  характерно для небольших однопользовательских систем.

характерно для небольших однопользовательских систем.

Для обращения к локальной таблице дескрипторов предназначен 16-разрядный регистр LDTR. Он содержит селектор, определяющий размещение в GDT дескриптора используемой локальной таблицы дескрипторов.

Получение дескриптора, находящегося в GDT ® рис. 3

Такая структура упрощает работу с таблицами LDT. Благодаря описанию LDT с помощью селектора эти таблицы превращаются в обычные сегменты памяти и, в частности, могут размещаться в любых областях памяти, участвовать в свопинге и т. п. Внутри процессора с регистром LDTR ассоциируется так называемый "теневой регистр", в котором и хранится дескриптор LDT текущей задачи. Это ускоряет в последующем обращение к локальной таблице дескрипторов текущей задачи. При переключении с одной задачи на другую для замены используемой LDT достаточно загрузить в регистр LDTR селектор новой LDT, а процессор уже автоматически загрузит в теневой регистр дескриптор новой LDT при первом обращении к нему.

Если в селекторе индикатор таблицы TI = 1, то дескриптор сегмента выбирается из локальной таблицы дескрипторов. Процесс определения адреса сегмента в этом случае представлен на рис. 4.

Он более сложен по сравнению с получением дескриптора из глобальной таблицы дескрипторов и проходит следующие этапы:

1. Анализируем, к какой из двух возможных таблиц дескрипторов идет обращение. Если в селекторе TI = 1, то обращение идет к локальной таблице дескрипторов.

2.  Находим дескриптор локальной таблицы дескрипторов в глобальной таблице дескрипторов.

Находим дескриптор локальной таблицы дескрипторов в глобальной таблице дескрипторов.

3. Считываем дескриптор LDT в "теневой" регистр регистра LDTR МП. После считывания дескриптора в "теневой" регистр дальнейшее обращение к сегменту аналогично обращению к GDT, где вместо GDTR используются поля базового адреса и предела из дескриптора LDTR, находящегося в "теневом" регистре.

4. По адресу локальной таблицы дескрипторов, находящемуся в ее дескрипторе, и номеру дескриптора из обрабатываемого селектора находим дескриптор сегмента в локальной таблице дескрипторов.

5. Записываем дескриптор сегмента в "теневой" регистр сегментного регистра микропроцессора для ускорения последующих обращений к искомому сегменту.

Таким образом, при обращении к сегменту через таблицу LDT появляется дополнительный уровень вложенности, снижающий быстродействие микропроцессора. "Теневые" регистры микропроцессора частично обеспечивают решение этой проблемы.

Поле адреса дескриптора, полученного из локальной или глобальной таблицы дескрипторов, определяет начало искомого сегмента. При суммировании полученного базового адреса сегмента и смещения в сегменте получается линейный адрес искомой ячейки памяти.

В случае если режим страничной адресации выключен (в регистре CR0 бит PG = 0), полученный линейный адрес равен физическому адресу искомого операнда или команды.

Рассмотрим подробнее процесс получения адреса операнда на примере команды

MOV EAX, [ECX+ESI+20h].

В этой команде нет специальных указаний об использовании сегмента, поэтому она обращается к текущему сегменту данных, селектор которого по умолчанию находится в сегментном регистре DS. Пусть (DS) = 0000000000011.0.XXb.

Формирование физического адреса операнда включает следующие действия (для сегментированного ЛАП):

1)Образовать эффективный адрес (вычислить смещение в сегменте): EA = (ECX)+(ESI)+20h.

2)Выбрать 3-й дескриптор (Index = 3) из GDT (TI = 0). Для этого:

o считать базовый адрес глобальной таблицы дескрипторов ( ) из GDTR;

) из GDTR;

o вычислить  ;

;

o обратиться по полученному адресу в память и считать нужный дескриптор.

3)Получить линейный адрес:  , где

, где  -базовый адрес сегмента из считанного дескриптора с номером 3.

-базовый адрес сегмента из считанного дескриптора с номером 3.

4)Так как при сегментной организации адресного пространства линейный адрес равен физическому, следует обратиться к памяти по сформированному адресу и передать двойное слово в EAX.

При TI = 1 потребовалось бы еще одно обращение к памяти для счтывания дескриптора LDT из GDT.

Чтобы сократить число обращений к памяти (а такой процесс должен проходить и при считывании кода каждой команды), в микропроцессорах с архитектурой IA-32 применяется так называемое кэширование дескрипторов. Кэширование опирается на тот факт, что обращение к памяти производится гораздо чаще, чем изменение используемых сегментов и переключение задач. Поэтому с каждым регистром, содержащим селекторы тех или иных сегментов (сегментные регистры, а также регистры локальной таблицы дескрипторов LDTR и регистр задач TR), ассоциируются "теневые", или кэш-регистры.

При первом считывании дескриптора, определяемого данным селектором, процессор автоматически считывает (кэширует) нужный дескриптор в соответствующий "теневой" регистр. Поскольку теперь дескриптор находится внутри МП, для получения линейного адреса памяти потребуется только сформировать эффективный адрес и просуммировать его с базовым адресом сегмента из нужного "теневого" регистра.

Так как программа обычно редко модифицирует регистры с селекторами, в защищенномрежиме она будет выполняться примерно с такой же скоростью, как и в реальном режиме.

Помимо локальной и глобальной таблиц дескрипторов в микропроцессорной системе используется также дескрипторная таблица прерываний (IDT). Она содержит дескрипторы специальных системных объектов, которые определяют точки входа в процедуры обработки прерываний.

IDT служит заменой таблицы векторов прерываний 16-разрядного микропроцессора. Обращение к ней проводится только аппаратными средствами МП при возникновении аппаратных прерываний или особых случаев при выполнении программы. Программы самостоятельно не могут обратиться к IDT, так как единственный бит индикатора таблицы в селекторе сегмента идентифицирует только GDT или LDT.

До перевода процессора в защищенный режим необходимо создать таблицы GDT и IDT и соответственно инициализировать регистры GDTR и IDTR. Таблицы GDT и IDT определяются при загрузке в соответствующие регистры GDTR и IDTR базового адреса и предела. Это действие осуществляется только один раз в ходе подготовки к переходу в защищенный режим, и в дальнейшем содержимое GDTR и IDTR не изменяется. Это значит, что местонахождение таблиц GDT и IDT в известном смысле фиксировано, и они не могут участвовать в свопинге.

При данном виде распределения памяти (разрывном и сегментном) реализуется мультипрограммный режим работы, но появляется проблема защиты памяти. Чтобы приложения не испортили саму ОС и друг друга, необходимо, чтобы модификация таблиц сегментов была доступна только ОС. Для этого код ОС должен выполняться в привилегированном режиме, позволяющем манипулировать с дескрипторами сегментов. А выход за пределы сегмента обычной программы должен вызывать прерывание по защите памяти.

Недостатками сегментного подхода организации памяти являются:

– длительность доступа к искомой ячейке: сначала нужно найти и прочитать дескриптор сегмента (эти данные используются для нахождения сегмента в физическом адресном пространстве, а затем ячейки в пределах сегмента). Для уменьшения этого времени применяется копирование дескрипторов в кэш (теневые регистры);

– длительность доступа к искомой ячейке: сначала нужно найти и прочитать дескриптор сегмента (эти данные используются для нахождения сегмента в физическом адресном пространстве, а затем ячейки в пределах сегмента). Для уменьшения этого времени применяется копирование дескрипторов в кэш (теневые регистры);

– фрагментация ОП

– проблема защиты памяти

Достоинства сегментной организации очевидны – адресация пространства до 4 Гб

– упрощается изоляция программ друг от друга в мультипрограммном режиме работы.

Организация виртуальной памяти на основе страничного представления памяти. Структура линейного адреса в страничном адресном пространстве универсального 32-разрядного микропроцессора. Трансляция линейного адреса в физический при страничной организации памяти. Назначение и структура каталога таблиц страниц и таблиц страниц.

Страничная организация памяти применяется только в защищенном режиме, если в регистре управления CR0 бит PG = 1.

Основное применение страничного преобразования адреса связано с реализацией виртуальной памяти, которая позволяет программисту использовать большее пространство памяти, чем физическая основная память.

Принцип виртуальной памяти предполагает, что пользователь при подготовке своей программы имеет дело не с физической ОП, действительно работающей в составе компьютера и имеющей некоторую фиксированную емкость, а с виртуальной (кажущейся) одноуровневой памятью, емкость которой равна всему адресному пространству, определяемому размером адресной шины (Lша) компьютера::  .

.

Для 32-разрядного микропроцессора:

Программист имеет в своем распоряжении адресное пространство, ограниченное лишь разрядностью адресной шины, независимо от реальной емкости оперативной памяти компьютера и объемов памяти, которые используются другими программами, параллельно обрабатываемыми в мультипрограммной ЭВМ.

Виртуальная память, обеспечивая программисту возможность обращаться к очень большому объему непрерывного адресного пространства, предоставляемого в его монопольное распоряжение, обладает обычными свойствами: побайтовая адресация, время доступа, сравнимое со временем доступа к оперативной памяти.

На всех этапах подготовки программ, включая загрузку в память, программа представляется в виртуальных адресах, и лишь при выполнении машинной команды виртуальные адреса преобразуются в физические. Для каждой программы, выполняемой в мультипрограммном режиме, создается своя виртуальная память. Каждая программа использует одни и те же виртуальные адреса от нулевого до максимально большого в данной архитектуре.

Для преобразования виртуальных адресов в физические физическая и виртуальная память разбиваются на блоки фиксированной длины, называемые страницами. Объемы виртуальной и физической страниц совпадают. Страницы виртуальной и физической памяти нумеруются. Отсутствующие в физической памяти страницы обычно хранятся во внешней памяти. Фиксированный размер всех страниц позволяет загрузить любую нужную виртуальную страницу в любую физическую.

При страничном представлении памяти виртуальный (логический) адрес представляет собой номер виртуальной страницы и смещение внутри этой страницы. В свою очередь, физический адрес - это номер физической страницы и смещение в ней.

Правила перевода номеров виртуальных страниц в номера физических страниц обычно задаются в виде таблицы страничного преобразования. Такие таблицы формируются системой управления памятью и модифицируются каждый раз при перераспределении памяти. Операционная система постоянно отслеживает состояние виртуальных страниц той или иной программы и определяет, находится ли она в оперативной памяти, и если находится, то в каком конкретно месте. Прикладные программы не касаются процесса страничного преобразования адреса и могут использовать все адресное пространство. Процессор автоматически формирует особый случай неприсутствия, когда программа  обращается к странице, отсутствующей в физической памяти. При обработке этого особого случая ОС загружает затребованную страницу из внешней памяти, при необходимости отправляя некоторую другую страницу на диск (процесс свопинга).

обращается к странице, отсутствующей в физической памяти. При обработке этого особого случая ОС загружает затребованную страницу из внешней памяти, при необходимости отправляя некоторую другую страницу на диск (процесс свопинга).

Рассмотрим страничное преобразования адреса в МП с архитектурой IA-32 при объеме страницы в 4 Кбайт. Основой страничного преобразования служит 32-разрядный линейный адрес, полученный на этапе сегментного преобразования логического адреса. Страничное преобразование выполняется при значении бита PG = 1 в управляющем регистре CR0.

В этом случае старшие 20 разрядов линейного адреса фактически представляют собой номер виртуальной страницы. Однако при прямом одноступенчатом преобразовании этого номера в номер физической страницы необходима таблица из 220 элементов длиной 4 байта каждый (20-разрядный номер страницы плюс некоторая дополнительная информация), т. е. 4 Мбайт. В мультипрограммной среде такая таблица может потребоваться для каждой задачи. Эта таблица должна постоянно храниться в ОП, чтобы не увеличивать существенно время формирования физического адреса. Для этих целей потребуется постоянное резервирование существенной части емкости ОЗУ, что на этапе появления первых ЭВМ на основе МП с архитектурой IA-32 было практически невозможно.

Вместо этого микропроцессор использует двухступенчатое страничное преобразование адреса. Корневая страница, называемая каталогом таблиц страниц (КТС), содержит 1024 32-разрядных элемента каталога таблиц страниц (ЭКТС - PDE page directory entry). Каждый из них адресует подчиненную таблицу страниц (ТС), то есть всего допускается до 1024 подчиненных таблиц страниц. Каждая из таблиц страниц содержит 1024 32-разрядных элемента таблицы страниц (ЭТС - PTE page table entry), каждый из которых и адресует физическую страницу. Таким образом, общее количество адресуемых физических страниц равно 220, то есть все виртуальное адресное пространство (4 Кбайт * 220 элементов = 232 байт). Каждая таблица занимает 1024 *4 = 4 Кбайт, то есть ровно 1 страницу. Общий объем таблиц, используемых для страничного преобразования, не уменьшился, а даже несколько возрос за счет использования каталога таблиц страниц. Однако, во-первых, практически всегда в системе этот размер можно существенно уменьшить за счет того, что некоторые линейные адреса никогда не будут сформированы (а эту информацию дают таблицы дескрипторов сегментов), и для них не нужно создавать таблицу страниц. А во-вторых, в оперативной памяти должны постоянно находиться лишь каталог таблиц страниц и таблица страниц выполняемой в настоящее время программы. Остальные таблицы страниц могут временно храниться во внешней памяти.

Вместо этого микропроцессор использует двухступенчатое страничное преобразование адреса. Корневая страница, называемая каталогом таблиц страниц (КТС), содержит 1024 32-разрядных элемента каталога таблиц страниц (ЭКТС - PDE page directory entry). Каждый из них адресует подчиненную таблицу страниц (ТС), то есть всего допускается до 1024 подчиненных таблиц страниц. Каждая из таблиц страниц содержит 1024 32-разрядных элемента таблицы страниц (ЭТС - PTE page table entry), каждый из которых и адресует физическую страницу. Таким образом, общее количество адресуемых физических страниц равно 220, то есть все виртуальное адресное пространство (4 Кбайт * 220 элементов = 232 байт). Каждая таблица занимает 1024 *4 = 4 Кбайт, то есть ровно 1 страницу. Общий объем таблиц, используемых для страничного преобразования, не уменьшился, а даже несколько возрос за счет использования каталога таблиц страниц. Однако, во-первых, практически всегда в системе этот размер можно существенно уменьшить за счет того, что некоторые линейные адреса никогда не будут сформированы (а эту информацию дают таблицы дескрипторов сегментов), и для них не нужно создавать таблицу страниц. А во-вторых, в оперативной памяти должны постоянно находиться лишь каталог таблиц страниц и таблица страниц выполняемой в настоящее время программы. Остальные таблицы страниц могут временно храниться во внешней памяти.

Старшие 20 разрядов линейного адреса разбиваются на два 10-разрядных поля: поле номера элемента каталога таблиц страниц и поле номера элемента таблицы страниц. Так как и каталог таблиц страниц, и каждая таблица страниц занимают ровно 1 страницу и выровнены по границе страницы, то младшие 12 разрядов их базового адреса равны нулю, и для определения их физического адреса достаточно 20-разрядного поля.

Для каталога таблиц страниц его 20-разрядный адрес находится в регистре управления CR3. КТС постоянно находится в памяти и не участвует в свопинге.

Старшие 20 разрядов физического адреса таблицы страниц извлекаются из ЭКТС. Структуры элемента КТС и элемента ТС схожи:

Старшие 20 разрядов физического адреса таблицы страниц извлекаются из ЭКТС. Структуры элемента КТС и элемента ТС схожи:

Старшие 20 разрядов элемента дают базовый адрес таблицы страниц (в ЭКТС) или физической страницы (в ЭТС). Биты P, A, R/W и U/S имеют определенное сходство с аналогичными атрибутами дескриптора сегмента, другие биты имеют специфическое назначение.

Бит присутствия P показывает, отображается ли адрес страничного кадра (таблицы страниц или страницы памяти) на страницу в физической памяти. При P = 1 страница присутствует в ОЗУ. При P = 0страницы в памяти нет, и обращение к этой странице вызывает прерывание типа "страничное нарушение".

Бит доступа А устанавливается микропроцессором в состояние А = 1 при обращении к данному страничному кадру для записи или чтения информации.

Бит модификации D (Dirty - "грязный") устанавливается процессором равным 1 в элементе ЭТС при записи на данную страницу. Для элементов каталога таблиц страниц значение бита D является неопределенным. При загрузке страницы в память операционная система сбрасывает бит D. Если при необходимости выгрузки страницы во внешнюю память оказывается, что для нее D = 0, это означает, что к странице в памяти не было обращений на запись, во внешней памяти есть ее точная копия, и реально передавать страницу из памяти на диск не нужно. Тем самым экономится время при свопинге.

Бит чтения-записи R/W и бит U/S (user/supervisor - пользователь/супервизор) определяют права доступа к таблице страниц или к странице для программ с различными уровнями привилегий. Для страниц существует только 2 уровня привилегий: уровень супервизора (U/S = 0), соответствующий значению DPL сегмента 0, 1, 2, и уровень пользователя (U/S = 1), соответствующий DPL = 3. Если к странице осуществляется запрос с уровнем привилегий 3 (программы пользователя), то при значении U/S = 0 ему запрещается доступ к соответствующей таблице или странице. Если U/S = 1, то при значении R/W = 0 разрешается только чтение таблицы или страницы, а при R/W = 1 - и чтение, и запись.

При запросах с большими привилегиями (системные программные уровни 0, 1, 2) допускается з0апись и чтение таблиц и страниц при любых значениях U/S, R/W (табл. 1).

| U/S | R/W | Допустимо для уровня 3 | Допустимо для уровней 0, 1, 2 |

| 0 | Х | Ничего | Чтение/запись |

| 1 | 0 | Чтение | Чтение/запись |

| 1 | 1 | Чтение/запись | Чтение/запись |

Биты PWT и PCD используются для управления работой кэш-памяти при страничной адресации. Бит PCD - запрещение кэширования страницы. При PCD = 1 кэширование запрещено. Бит PWT - бит обратной записи страниц. Определяет метод обновления внешней кэш-памяти (кэш 2-го уровня). При PWT= 1 - обновление проводится методом сквозной записи (как для внутреннего кэша), при PWT = 0 - методом обратной записи.

Биты 9…11 в ЭКТС и ЭТС зарезервированы за операционной системой. Процессор никогда не использует и не изменяет эти биты. Разработчики ОС могут привлечь эти биты для хранения информации о "старении" страниц, чтобы определять страницы, подлежащие замене из внешней памяти, и для других целей.

Старшие 10 разрядов линейного адреса совместно с содержимым регистра управления CR3 определяют необходимый элемент каталога таблиц страниц. Следующие 10 разрядов линейного адреса содержат номер элемента в выбранной таблице страниц.

Так как и ЭКТС, и ЭТС имеют длину 4 байта, для получения смещения начала элемента относительно начала соответствующей таблицы необходимо его номер умножить на 4.

Последние 12 разрядов линейного адреса содержат смещение в странице. Таким образом, сумма смещения в странице и базового адреса страницы, извлеченного из ЭТС, дает физический адрес искомого байта.

Основным достоинством страничного подхода распределения памяти является практическое отсутствие фрагментации: на каждую задачу может приходиться лишь по одной не полностью заполненной странице (последней): ~4К при объемах памяти в единицах Гигабайт.

Недостатками этого способа являются:

− существенные накладные расходы − таблицы страниц нужно также размещать в памяти и обрабатывать их;

− разбивка программы на страницы производится без учёта логической взаимосвязи элементов кода, и тогда межстраничные переходы могут возникать чаще, чем межсегментные.

Второй недостаток устраняется использованием сегментно-страничного способа размещения памяти (правда, при дальнейшем росте накладных расходов).

2018-02-14

2018-02-14 2804

2804