Индикаторы SIMATIC S7-300 приведены на рисунке 1.3

Рисунок 1.3 – Индикаторы в S7-300 Рисунок 1.3 – Индикаторы в S7-300 | SF – Суммарная ошибка, программная ошибка в CPU или ошибка от модуля с внутренней диагностикой. BF – Ошибка сети PROFIBUS DP (для модулей с дополнительным интерфейсом DP). Светится постоянно – при коротком замыкании кабеля или неправильной конфигурации. Мигает – при отсутствии связи с каким-либо участником по PROFIBUS DP. |

DC5V – Индикация о наличии 5V.

FRCE – Индикация об установленном режиме Force (по меньшей мере, один вход или выход управляется принудительно в соответствии с таблицей значений).

RUN – Run-режим: мигает при старте CPU, светится постоянно в Run-режиме.

STOP – Stop-режим: медленно мигает, если требуется сброс (например, при отсутствии модуля ММС); быстро мигает во время сброса, светится постоянно в Stop-режиме.

ТИПОВАЯ АРХИТЕКТУРА ПРОЦЕССОРА S7

Области памяти CPU

Память S7-CPU может быть разделена на четыре области (см. рисунок 2.1):

‒ Загрузочная память используется для хранения программы пользователя без символов и комментариев. Загрузочная память может быть выполнена в виде RAM или FLASH EPROM;

‒ Рабочая память (встроенная RAM) используется для хранения соответствующей части S7-программы, необходимой для выполнения программы. Программа выполняется исключительно в рабочей памяти;

‒ Область ввода-вывода разрешает прямой доступ ко входам и выходам связанных с ней сигнальных модулей;

‒ Системная память (RAM) содержит области отображения входного и выходного процессов, меркеры, таймеры и счетчики. Кроме того, она содержит локальный стек, стек блоков и стек прерываний.

Рисунок 2.1 – Области памяти CPU

Совокупность программно доступных адресов модулей ввода-вывода образуют адресное пространство CPU (I/O addresses area). В системе памяти S7-CPU это система адресов разделена на 2 равные области – для чтения и записи. Размеры адресного пространства зависят от типа CPU и занимают от 1 Kbyte до 16 Kbyte.

Таблица 2.1 показывает обозначения периферийных адресов в Step 7 Lite.

Таблица 2.1 – Обозначение периферийных адресов в Step 7 Lite

| Область адресов | Доступ | Запись в Step 7 Lite |

| Периферийная область: входы | Периферийный входной байт Периферийное входное слово Периферийное входное двойное слово | PIBx PIWx PIDx |

| Периферийная область: выходы | Периферийный выходной байт Периферийное выходное слово Периферийное выходное двойное слово | PQBx PQWx PQDx |

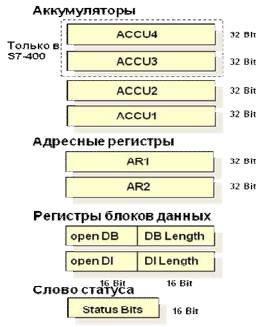

Регистры CPU

Регистры CPU используются для адресации или обработки данных. Данные могут быть обменены между областями памяти CPU и регистрами с помощью соответствующих команд. CPU содержит следующие программно доступные регистры (см. рисунок 2.2):

‒ Аккумуляторы (ACCU). Два (в S7-300) или четыре (в S7-400) аккумулятора используются для арифметики, сравнений с байтами, словами или двойными словами;

‒ Адресные регистры (регистры AR1, AR2). Два адресных регистра используются как указатели для косвенной адресации памяти;

‒ Регистры блоков данных (регистры DB, DI). Регистры блоков данных содержат номера открытых блоков данных. Таким образом, возможно, что открыты одновременно два DB: один DB с помощью регистра DB, другой как экземпляр DB с помощью регистра DI. Когда DB открыт, его длина (в байтах) автоматически загружается в связанный с ним регистр;

‒ Слово статуса (регистр STW). Содержит различные биты, которые отражают результат или статус отдельных инструкций во время выполнения программы.

Рисунок 2.2 – Регистры CPU

Для создания программ управления необходимо знать назначение отдельных бит некоторых регистров.

2.2.1 Master Control Relay (MCR) – Главное реле управления

MCR – это «самый главный» выключатель, управляющий подачей энергии на элементы технологического процесса и, в случае аварии, позволяющий их обесточить. В Step 7 есть возможность в зависимости от состояния MCR-бита просто запретить прохождение ненулевых сигналов на выходы контроллера, т.е. заблокировать выходы.

Управление MCR происходит посредством стека шириной в один бит и глубиной восемь записей (см. рисунок 2.3). MCR активизирован (соответствует заблокированному главному реле управления) до тех пор, пока все восемь записей в стеке не станут равными 1.

Рисунок 2.3 – Управление MCR

2.2.2 Регистр STW – Слово состояния

Выполнение команды может изменить соответствующие биты слова состояния CPU. Эти биты могут использоваться как результат операции, а также как информация о результате выполнения той или иной команды. Регистр STW хранит 9 битовых признаков выполнения операций (см. рисунок 2.4).

Рисунок 2.4 – Биты слова состояния

‒ Первичный опрос

Бит состояния /FC управляет бинарной логикой внутри логической системы управления. Шаг битовой логики всегда начинается с /FC = «0» и инструкции бинарной проверки, первичного опроса. Первичный опрос устанавливает /FC = «1».

Шаг битовой логики завершается присваиванием бинарного значения (например, единичной катушки или назначения), условным переходом или сменой блока. Эти элементы устанавливают /FC = «0»;

‒ Результат логической операции

Бит состояния RLO – это промежуточный буфер в операциях бинарной логики. В ходе начальной проверки CPU пересылает результат считывания (проверки) в RLO, комбинирует результат считывания с хранимым RLO в каждое последующее считывание и сохраняет результат, в свою очередь, в RLO.

Вы можете сохранить RLO с помощью катушки / блочного элемента SAVE в бинарном результате. При помощи RLO управляются функции для работы с памятью, таймеры и счетчики, а также выполняются некоторые функции перехода;

‒ Состояние сигнала

Бит состояния STA соответствует сигнальному состоянию считанного бинарного операнда. В случае функций для работы с памятью значение STA то же, что и записанное значение, или (если операции записи не было произведено, например, если RLO = «0» или MCR активировано) STA соответствует значению адресованного (и не модифицированного) бинарного операнда.

В случае оценок фронта FP или FN значение RLO перед оценкой фронта записывается в STA. Все остальные бинарные функции устанавливают STA = «1»;

‒ Бит состояния OR

Бит состояния OR хранит результат выполненной последовательной схемы или выполненного условия AND и показывает следующим обрабатываемым параллельным схемам или функции OR, что результат уже определен. Все другие бинарные функции сбрасывают бит состояния OR;

‒ Двоичный результат

Бит состояния BR (двоичный результат) помогает реализовать механизм EN/ENO для вызовов блоков (в сочетании с графическими языками). Вы также можете самостоятельно устанавливать, сбрасывать или считывать бит состояния BR;

‒ Переполнение

Бит состояния OV отображает ошибки, возникающие при выполнении математических команд или команд сравнения для чисел с плавающей точкой (REAL). Бит OV устанавливается этими командами после того, как имела место ошибка (переполнение, недопустимая операция, сравнение невыполнимо). Бит состояния OV сбрасывается после исчезновения ошибки;

‒ Переполнение с запоминанием

Бит состояния OS хранит установленный бит состояния OV. Всякий раз, когда CPU устанавливает бит состояния OV, он также устанавливает бит состояния OS. Однако, если следующая корректно выполненная операция сбрасывает OV, OS остается установленным. Это дает возможность обнаружить выход за границы диапазона или операцию с недействительным числом REAL, даже позже по ходу программы.

Бит состояния OS доступен для прямого чтения. Смена блока сбрасывает бит состояния OS;

‒ Кодовые биты условия СС0, СС1

Биты состояния CC0 и CC1 предоставляют информацию о результате функции сравнения, арифметической или математической функции, побитовые логические операции или о бите, выдвинутом функцией сдвига. Вы можете непосредственно считывать комбинации СС0 и СС1.

2018-02-20

2018-02-20 2700

2700