МЕЖДУНАРОДНЫЙ ИНСТИТУТ КОМПЬЮТЕРНЫХ ТЕХНОЛОГИЙ

ФАКУЛЬТЕТ ИНФОРМАЦИОННЫХ И ЭНЕРГЕТИЧЕСКИХ СИСТЕМ

КАФЕДРА информатики и вычислительной техники

ЗАДАНИЕ

На курсовой проект

по дисциплине " ТЕОРИЯ АВТОМАТОВ"

Тема проекта: "Синтез синхронного управляющего автомата"

Студент группы ВМо-072 Волокитина Надежда Александровна

фамилия, имя, отчество

Номер варианта___ 9 – 2.14 ____________________________________

Технические условия: тип управляющего автомата – Мура; способ кодирования внутренних состояний автомата –эффективный 2 способ; тип триггерных схем – комбинированные синхронные двухтактные RS - триггеры; элементная база логического преобразователя – двухуровневая программируемая логическая матрица; количество входных сигналов УА – 6; количество выходных сигналов (микроопераций) УА – 7; количество микрокоманд УА – 10; количество микроопераций в каждой микрокоманде – 2..5; количество операторных вершин ГСА – 13; количество условных вершин ГСА – 8; разновидность УА – инициальный.

Содержание и объем проекта

расчетно - пояснительная записка – страниц формата А4, поясняющие текст, рисунки, расчеты, таблицы, схема электрическаяфункциональная УА.

_

Задание принял студент гр. ВМо-072 / Н.А.Волокитина /

подпись, дата инициалы, фамилия

Руководитель / C.H. Плотников /

подпись, дата инициалы, фамилия

Замечания руководителя.

Содержание

ОСновная часть……………………………………………………………...….6

1. Основные особенности теории синхронных автоматов…….………..….…6

2. Общие принципы построения и реализации синхронных

управляющих автоматов………………………………………..…..……...7

2.1 Обобщённая структура и принцип функционирования

синхронных управляющих автоматов.……………….…..……..…........7

2.2 Последовательность синтеза синхронных управляющих

автоматов………………………………………………………..…..…….8

2.3 Начальная формализация задачи синтеза УА……………..……….…9

3. Исходные данные для курсового проектирования…………….…..…......11

4. Автоматное описание управляющего автомата………………..…..……..12

5. Анализ граф _- схемы алгоритма синтезируемого управляющего

автомата и детализация его структурной схемы. Исходные данные

для курсового проектирования………………………….…..………..…......14

5.1 Анализ и разметка граф-схемы алгоритма…………..……..………..14

5.2 Описание управляющего автомата с помощью таблиц переходов

и выходов. …………………………………………….……………….15

6. Структурный синтез управляющего автомата со схемной

реализацией логики управления. ………………..………….…………....16

6.1 Тип элементов памяти. ………….…..…………………..…………...16

6.2 Структурное кодирование входных, выходных сигналов и

состояний автомата. ………….…..………..……………..…………..17

6.3 Детализация блока памяти…………………………………………...19

6.4 Составление расширенной структурной таблицы

переходов и выходов………………………………………………...20

6.5. Составление логических уравнений для выходных сигналов и

функций возбуждения блока памяти ……………………………....21

6.6 Минимизация логических функций возбуждения и выходов….….22

7. Разработка и оформление схемы электрической функциональной

синтезированного синхронного управляющего автомата…………………23

ЗАКЛЮЧЕНИЕ……………………………………………………….……….……25

Литература………………………………………………………….………….26

Основные особенности теории синхронных автоматов

Математической моделью дискретного устройства является абстрактный автомат, определяемый как шестикомпонентный кортеж, или вектор [4 - 11]:

S = (Z, A,W, δ, λ, a1), (1)

у которого:

Z={z1,…zf…zF} - множество входных сигналов автомата (входной алфавит);

A={a1,…am…aM} - множество состояний автомата (алфавит состояний);

W={w1,…wg…wG} – множество выходных сигналов автомата (выходной алфавит);

δ: A х Z ® A – функция переходов автомата, реализующая отображение Dδ  A х Z на A.

A х Z на A.

Другими словами, функция δ некоторым парам состояние - входной сигнал (am, zf) ставит в соответствие состояние автомата as = δ (am, zf), as  A;

A;

λ: A х Z ® W – функция выходов, реализующая отображение D  A х Z на W, которая некоторым парам состояние - входной сигнал (am, zf) ставит в соответствие выходной сигнал автомата wg = λ (am, zf);

A х Z на W, которая некоторым парам состояние - входной сигнал (am, zf) ставит в соответствие выходной сигнал автомата wg = λ (am, zf);

a1  A – начальное состояния автомата.

A – начальное состояния автомата.

Под алфавитом здесь понимается непустое множество попарно различных символов. Элементы алфавита называются буквами, а конечная упорядоченная последовательность букв - словом в данном алфавите.

Абстрактный автомат имеет один вход и один выход. Автомат работает в дискретном времени, принимающем целые неотрицательные значения t = 0,1,2,… В каждый момент t дискретного времени автомат находится в некотором состоянии a(t) из множества состояний автомата, причем в начальный момент времени t(0) автомат может находиться в начальном состоянии a(0) = a1. В момент t, будучи в состоянии a(t), автомат способен воспринять на входе букву входного алфавита z(t)  Z. В соответствии с функцией выходов он выдает в тот же момент времени t букву выходного алфавита w(t) = λ (a(t), z(t)) и в соответствии с функцией переходов перейдет в следующее состояние a(t +1)=δ (a(t), z(t)), причем a(t +1)

Z. В соответствии с функцией выходов он выдает в тот же момент времени t букву выходного алфавита w(t) = λ (a(t), z(t)) и в соответствии с функцией переходов перейдет в следующее состояние a(t +1)=δ (a(t), z(t)), причем a(t +1)  A, а w(t)

A, а w(t)  W. Смысл понятия абстрактного автомата состоит в том, что он реализует некоторое отображение множества слов входного алфавита Z в множество слов выходного алфавита W. Иначе, если на вход автомата, установленного в начальное состояние a1, подавать буква за буквой некоторую последовательность букв входного алфавита z(0), z(1), z(2), … - входное слово, то на выходе автомата будут последовательно появляться буквы выходного алфавита w(0), w(1), w(2), … - выходное слово. Каждому входному слову соответствует определенное выходное слово, структура которого определяется функциями переходов и выходов.

W. Смысл понятия абстрактного автомата состоит в том, что он реализует некоторое отображение множества слов входного алфавита Z в множество слов выходного алфавита W. Иначе, если на вход автомата, установленного в начальное состояние a1, подавать буква за буквой некоторую последовательность букв входного алфавита z(0), z(1), z(2), … - входное слово, то на выходе автомата будут последовательно появляться буквы выходного алфавита w(0), w(1), w(2), … - выходное слово. Каждому входному слову соответствует определенное выходное слово, структура которого определяется функциями переходов и выходов.

Таким образом, на уровне абстрактной теории понятие "работа автомата" понимается как преобразование входных слов в выходные слова. Структурной моделью нулевого уровня абстрактного автомата является модель, представленная на рис. 1.

|

Z W

Рис. 1 Структурная модель абстрактного автомата

(нулевой уровень)

Чтобы задать конечный автомат S, необходимо описать все компоненты вектора S = (Z, A,W, δ, λ, a1), т.е. входной и выходной алфавиты и алфавит состояний, а также функции переходов и выходов. Среди множества состояний может быть выделено начальное состояния автомата a1, в котором автомат находится в момент t = 0.

По способу организации автоматного времени все автоматы делят на два больших класса: синхронные автоматы и асинхронные автоматы. Для синхронных автоматов моменты времени, в которых фиксируются изменения состояния автомата, задаются специальным устройством - генератором синхронизирующих сигналов (синхросигналов). Генератор формирует синхронизирующие сигналы через определенные промежутки времени, длительность которых может быть постоянной или переменной. В асинхронных автоматах моменты перехода автомата из одного состояния в другое заранее не определены, так как их продолжительность целиком определяется временем переходных процессов, происходящих в автомате.

При реальной работе любого автомата необходимо учитывать такие негативные явления, которые получили название "гонки" или "состязания". Эти явления обусловлены ограниченным быстродействием различных физических элементов автомата, конечным временем распространения электрических сигналов по линиям связи, различной длиной линий связи. В синхронных автоматах борьба с такими негативными явлениями осуществляется путем выбора (определения) минимально возможного такта работы автомата. В асинхронных автоматах устранения гонок или состязаний добиваются специальными, весьма сложными, видами кодирования входных, выходных сигналов и внутренних состояний автомата.

Надежную работу автомата легче обеспечить, если его выполнить в виде синхронного автомата, однако максимальным быстродействием обладают асинхронные автоматы. В то же время основой всех синхронных автоматов являются асинхронные автоматы.

2. Общие принципы построения и реализации синхронных управляющих автоматов.

2.1 Обобщённая структура и принцип функционирования синхронных управляющих автоматов.

Управляющий автомат (УА) генерирует последовательность управляющих сигналов из множества у1... уm (сигналы у1... уm называются микрооперациями, каждый из сигналов может принимать только одно из значений 1 или 0), предписанную микропрограммой У; и соответствующую значениям логическим условий х1...хn. При выполнении процессором пакета микропрограмм на его входы последовательно подаются коды операции, которые соответствуют той или иной микропрограмме. На входы процессора

могут поступать внешние сигналы логических условий, а с выходов сниматься сигналы для управления внешними устройствами.

Переход на новый шаг алгоритма осуществляется только с приходом специального сигнала синхронизации (S).

Выходные сигналы у1...уm могут иметь различную длительность. Математической моделью управляющих автоматов, формирующих короткие выходные сигналы, является модель Мили, а для автоматов, формирующих длинные выходные сигналы - модель Мура.

2.2 Последовательность синтеза синхронных управляющих автоматов.

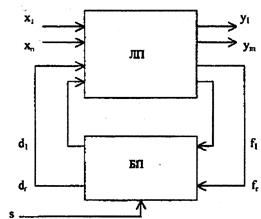

Синтезируемый УА на уровне «чёрного ящика» представим так, как показано на рисунке 2.

Рис. 2.

В данном курсовом проекте синхронный управляющий автомат,

реализуется некоторым алгоритмом функционирования, который формально задаётся таким начальным языком описания как граф - схема алгоритма (ГСА).

ГСА - это ориентированный связный граф, включающий вершины четырёх типов: начальную, конечную, операторную и условную (рисунок 3). Конечная, операторная и условная вершины имеют по одному входу, начальная вершина входов не имеет. У начальной и операторной вершин по одному выходу, у условной - два выхода, помеченных символами 1 и 0. конечная вершина выходов не имеет.

ГСА удовлетворяет следующим условиям:

1) входы и выходы вершин соединяются друг с другом с помощью дуг, направленных всегда от выхода ко входу;

2) каждый выход соединён только с одним входом;

3) любой вход соединяется, по крайней мере, с одним выходом;

4) любая вершина ГСА лежит, по крайней мере, на одном пути из начальной вершины к конечной;

5) в каждой условной вершине записывается один из элементов множества Х={ х1...хn } логических условий (разрешается в различных условных вершинах запись одинаковых элементов множества Х);

6) один из выходов условной вершины, помеченный «0» или «1», может соединяться с её входом;

7) в каждой операторной вершине записывается оператор (микрокоманда) У; - подмножество множества микроопераций У={ у1...уm } (разрешается запись в различных операторных вершинах одинаковых микрокоманд).

а), б) - начальная и конечная вершины; в) - операторная вершина;

г) - условная вершина.

Рис. 3 Графическое представление вершин ГСА.

На первом этапе формализации алгоритм функционирования УА разбивается на ряд шагов, выполняемых последовательно. В процессе такого разбиения выделяются все операции по выполнению алгоритма, а также условия выполнения этих операции на каждом конкретном шаге.

Выполняемые операции заносятся в операторные вершины ГСА, а условия перехода от одного оператора к другому - в условные вершины.

2.3 Современная элементная база для реализации логических преобразователей и блоков памяти управляющих автоматов.

Структура управляющего автомата во многом зависит от принципа его построения.

Принцип схемной логики (жёсткая логика) предусматривает реализацию множества состояний автомата блоком памяти (БП) на запоминающих элементах (триггеры), а функции выходов и переходов формируются логическим преобразователем (ЛП). Алгоритм функционирования УА в этом случае полностью определяется схемой соединения его элементов.

Рис. 4. Первый уровень структурной реализации УА.

ЛП представляет собой комбинационную схему. БП содержит r элементов памяти, которыми для синхронных автоматов являются специально разработанные синхронные элементарные автоматы с памятью, которые стали называть триггерами.

Наибольшее распространение получили несколько разновидностей синхронных триггеров, которые получили следующие наименования: RS - триггер, D - триггер, Т - триггер, JK - триггер. Отличаются данные триггеры количеством информационных и управляющих сигналов, а также способами записи в них хранимой информации.

Блок памяти на своих выходах d1..dr должен формировать двоичный код, который соответствует номеру текущего шага алгоритма УА, или текущему внутреннему состоянию автомата. Предварительно все возможные внутренние состояния УА обозначаются некоторыми абстрактными символами, которым затем ставятся в однозначное соответствие двоичные структурные коды. На входы блока памяти должны воздействовать сигналы f1... fr, которые формируются ЛП и в совокупности образуют двоичный код, соответствующий структурному коду следующего внутреннего состояния УА. Совокупность одновременно формируемых сигналов f1... fr принято называть функцией возбуждения блока памяти, а каждый отдельный сигнал f1... fr - функциями возбуждения элементов памяти.

Задачей логического преобразователя является формирование выходных сигналов УА и функций возбуждения элементов памяти как некоторой системы логических функций, аргументами которых являются переменные х1,...хn, d1...dr. Такую систему логических функций принято называть каноническими логическими уравнениями УА, которые и должны реализоваться логическим преобразователем.

В качестве элементного базиса для реализации ЛП выбрана двухуровневая программируемая логическая матрица (ПЛМ). Это обусловлено тем, что в настоящее время ПЛМ являются весьма доступными, для широкого пользователей, высоко экономичными как для серийного, так и для разового производства изделий вычислительной техники, ориентированы на реализацию системы логических функций, представленных в дизъюнктивных нормальных формах (ДНФ).

Весьма существенным является также и то, что при использовании ПЛM в качестве элементного базиса для ЛП предоставляется возможность реализации в рамках данного курсового проекта УА достаточной сложности при компактном его графическом изображении в виде схемы электрической функциональной.

Принцип программируемой логики (гибкая логика) предусматривает для реализации отдельных функций наличие хранимых программ, составленных из команд, каждая из которых, в свою очередь, включает одну или несколько элементарных операций.

Принцип программного управления, используемый повторно для реализации отдельных сложных операций как последовательности элементарных микроопераций, получил название принципа микропрограммного управления.

2020-01-14

2020-01-14 251

251