При реализации системы логических функций на программируемой логической матрице наиболее эффективен метод групповой минимизации.

Он состоит в следующем: в системе логических уравнений для функций возбуждения и функций выходов отыскиваются группы одинаковых элементарных конъюнкций. Для каждой группы вводится фиктивная переменная с каким - либо индексом. Далее все исходные логические уравнения переписываются в терминах фиктивных переменных. Затем на ПЛМ реализуют элементарные конъюнкции, соответствующие каждой фиктивной переменной и их дизъюнкции в соответствии с уравнениями, содержащими фиктивные переменные.

Введём для одинаковых конъюнкций фиктивные переменные z1 – z22.

Пусть:

z1 =

z2 =

z3 =

z4 =

z5 =

z6 =

z7 =

z8 =

z9 =

z10 =

z11 =

z12 =

z13 =

z14 =

z15 =

z16 =

z17 =

z18 =

z19 =

z20 =

z21 =

z22 =

z23 =

z24 =

z25 =

z26 =

z27 =

Тогда функции возбуждения примут вид:

f1= z4 + z6 + z7 + z8 + z9 + z11+ z12+ z13+ z14+ z20+ z21+ z22

f2= z1+ z4 + z5 + z8 + z10 + z13 + z17 + z18 + z19+ z20+ z21

f3= z3+ z5 + z7 + z8 + z9 + z10 + z12 + z13 + z17

f4= z3+ z16 + z17 + z18+ z19

А функции выходов:

y1= z20 + z22 + z9

y2= z24 + z25 + z14 + z26 + z17 + z27 + z21

y3= z14 + z21 + z22

y4= z23 + z14 + z26 + z21

y5= z23 + z9 + z25 + z26 + z27 + z20

y6= z24 + z14 + z26 + z21

y7= z23 + z14 + z26 + z22

7. Разработка и оформление схемы электрической функциональной синтезированного синхронного управляющего автомата.

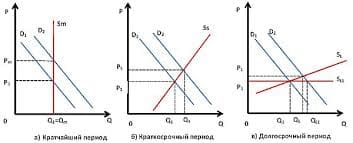

Схема электрическая функциональная синтезируемого УА состоит из объединённых схем функциональных блока памяти (рисунок 7) и логического преобразователя, реализованного на двухуровневой программируемой логической матрице (ПЛМ).

ПЛМ – это интегральные схемы, позволяющие оперативно реализовывать достаточно сложные многовыходные логические преобразователи, закон функционирования которых изначально представляется в естественной для человека форме.

Схема электрическая функциональная управляющего автомата изображена на рисунке 8.

Рис. 7

Как видно из рисунка 7, ПЛМ состоит из блока инверторов входных логических переменных (х1...х6) и двух матриц. Матрица И реализует на шинах z1...z22 элементарные конъюнкции с любым набором прямых и инверсных значений логических переменных х1...х6, а матрица ИЛИ реализует элементарные дизъюнкции с элементарными конъюнкциями, сформированными на шинах z1...z22. Матрицы И и ИЛИ представляют собой систему перпендикулярных проводников, в узлах пересечения которых располагаются полупроводниковые элементы, реализующие с резисторами нагрузки операции И и ИЛИ. Операция И реализуется при помощи диодов, а операция ИЛИ - при помощи триодов.

2020-01-14

2020-01-14 175

175