А.А.Бошляков, В.И.Рубцов

Методические указания к лабораторному практикуму по курсу «Управление в технических системах» (микропроцессорные системы управления)

Рассмотрены принципы работы микропроцессорной системы управления на основе микроконтроллера PIC16F877 и этапы разработки программного обеспечения для неё.

Для студентов, изучающих курс «Управление в технических системах».

Рецензент: Нечаев Л.Д.

Введение

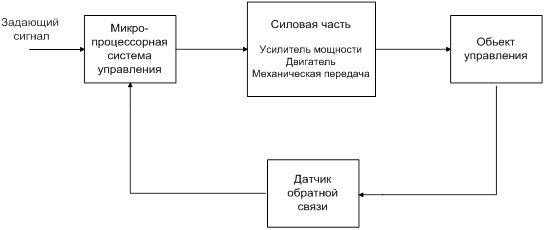

Структура замкнутого привода с микропроцессором в контуре управления показана на рис.1.

Рис.1

Изучение основ работы с микропроцессорной системой управления проводится на примере одной из наиболее производительных моделей микроконтроллеров, имеющую развитую систему модулей для связи с объектом управления, PIC16F877 фирмы Microchip. В методических указаниях использована техническая документация фирмы Microchip.

Цель работы:

1. Изучение принципов работы микроконтроллера (МК).

2. Знакомство с этапами разработки программного обеспечения МК.

Характеристика микроконтроллера PIC16F877.

Характеристика вычислительного ядра МК:

· выполнено по высокоскоростной RISC технологии. Высокая производительность достигается за счет применения конвейерной архитектуры и малого числа команд (всего 35);

· тактовая частота МК составляет 20 МГц, при этом время длительности машинного цикла достигает 200 нс;

· 8Кх14 слов FLASH памяти программ;

· 368х8 байт памяти данных (ОЗУ);

· 256х8 байт EEPROM памятью данных;

· систему прерываний (14 источников).

Характеристика периферийных модулей:

· два 8-разрядных таймера/счетчика;

· один 16-разрядный таймер/счетчик с возможностью подключения внешнего резонатора;

· два модуля захват/сравнение/ШИМ:

- 16-разрядный захват (максимальная разрешающая способность 12.5 нс);

- 16-разрядный сравнение (максимальная разрешающая способность 200нс);

- 10 разрядный ШИМ;

· 8-канальное 10-разрядное АЦП;

· последовательный синхронный порт;

- ведущий/ведомый режим SPI;

- ведущий/ведомый режим I2C;

· последовательный асинхронный приемопередатчик USART c поддержкой детектирования адреса;

· ведомый 8-разрядный параллельный порт PSP с поддержкой внешних сигналов #RD, #WR, #CS.

Аппаратная составляющая микроконтроллера

Архитектура микроконтроллера.

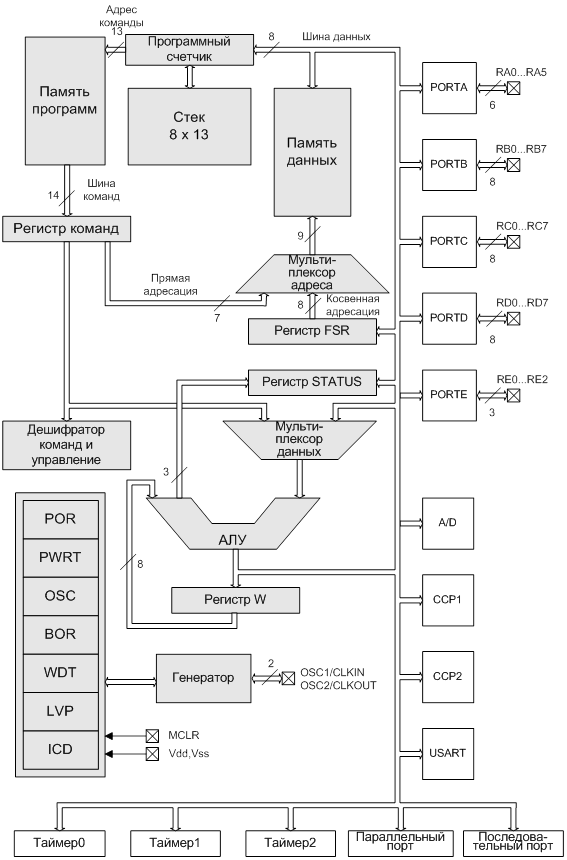

Архитектура МК показана на рис.2. МК можно условно разделить на две части: вычислительное ядро (серый цвет) и периферийные модули (белый цвет).

Рис.2. Архитектура МК

Вычислительное ядро работает следующим образом. Программа работы МК находится в FLASH памяти программ. Программа выполняется последовательно до тех пор, пока не встретится команда перехода. Регистр команд (РК) содержит текущую команду на время ее дешифрации и выполнения, а программный счетчик (ПС) предназначен для хранения адреса следующей команды. Когда текущая команда завершена, то:

1. по адресу из ПС производится выборка команды из памяти программ в РК;

2. пока дешифрируется эта команда, производится инкремент ПС на единицу и ПС адресует следующую команду;

3. когда выполнение данной команды заканчивается, содержимое ПС выдается памяти программ и цикл повторяется.

Команды безусловного перехода позволяют изменить естественный порядок следования команд путем замещения содержимого ПС (т. е. адреса следующей по порядку команды) адресом, определяемым самой командой перехода.

Команды условных переходов замещают или не замещают содержимое ПС в зависимости от признаков результатов предыдущих команд. Признаки результатов предыдущих команд находится в регистре STATUS. В этом регистре имеются биты, показывающие такие условия, как получение в предыдущих операциях положительного, отрицательного или нулевого результата. Когда реализован переход, начинается новая последовательность команд с адреса, к которому осуществлен переход.

Циклы реализуются с помощью команд условных переходов.

Действия, связанные с вызовом подпрограммы, требуют специальной разновидности перехода. Как и в других переходах, вызов подпрограммы также заменяет содержимое ПС на адрес перехода, но при этом запоминается текущее содержимое ПС в специальной области памяти, называемой стеком. Команда возврата должна восстановить в ПС адрес возврата, чтобы после завершения подпрограммы продолжалось последовательное выполнение основной программы.

Арифметико-логическое устройство (АЛУ) выполняет арифметические и логические операции над данными. Входные данные АЛУ в зависимости от кода операции могут находиться:

а. в регистре W;

б. либо в РК, либо в памяти данных.

Структура памяти данных показана на рис. 4.

Мультиплексор данных подключает к входу АЛУ в соответствии с кодом операции либо РК (в режиме непосредственной адресации), либо память данных (в режиме прямой и косвенной адресации).

Мультиплексор адреса в зависимости от режима адресации позволяет адресовать ячейки памяти данных либо от РК (в режиме прямой адресации), либо от регистра косвенной адресации FSR (в режиме косвенной адресации).

Биты конфигурации задают режим функционирования МК:

· сброс по включению питания (POR);

· таймер включения питания (PWRT);

· таймер запуска генератора (OSC);

· сброс по снижению напряжения питания (BOR);

· сторожевой таймер (WDT);

· режим низковольтного последовательного программирования (LVP);

· режим внутрисхемной отладки (ICD).

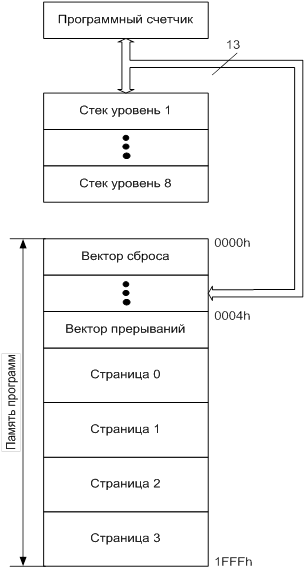

Организация памяти команд

Структура памяти команд показана на рис.3.

Микроконтроллеры PIC16F877 имеет 13-разрядный программный счетчик ПС, способный адресовать 8К х 14 бит памяти программ.

Адрес вектора сброса - 0000h.

Адрес вектора прерываний - 0004h.

Рис.3. Структура памяти программ и стека

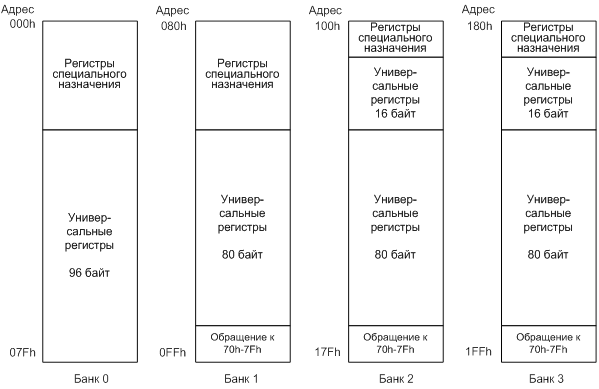

Организация памяти данных

Структура памяти данных показана на рис.4.

Память данных разделена на четыре банка, которые содержат регистры общего и специального (SFR) назначения. Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками данных. В таблице 1 показано состояние управляющих битов при обращении к банкам памяти данных.

Таблица 1. Обращение к банкам памяти данных

| RP1 | RP0 | Банк |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 2 |

| 1 | 1 | 3 |

Объем банков памяти данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения выполненные как статическое ОЗУ. Все банки содержат регистры специального назначения. Часто используемые регистры специального назначения отображаться в других банках памяти. Старшие 16 байт памяти данных в банках 1, 2 и 3 отображены в банке 0.

Рис.4. Структура памяти данных

Периферийный модуль – порт ввода/вывода PORTB

Познакомимся в работой периферийных модулей МК на примере порта ввода/вывода PORTB.

PORTB - это 8-разрядный двунаправленный порт. Любой разряд порта можно конфигурировать как выход или вход. Запись "1" в соответствующие разряды регистра TRISB переводит разряды порта в режим входа; запись "0" – режим выхода.

Пример 5-2: Инициализация порта В

CLRF PORTB ; обнуление регистра выходных данных

BANKCELL TRISB ; обращение к банку,;содержащему регистр ;TRISB.

MOVLW 0x0F ;константа для инициализации порта

MOVWF TRISB ;установка RB <3:0> как входов,

;RB <7:4> как выходы.

Все разряды PORTB могут быть подтянуты к высокому уровню внутренними ключами для подключения к длинным линиям связи. Включение ключей выполняется записью "0" в разряд 7 регистра OPTION (бит RBPU). Ключи выключаются при:

· программировании разряда порта как выход;

· после "Сброса".

Четыре разряда PORTB (RB7-RB4) формируют прерывание при изменении состояния. Только разряды сконфигурированные как входы могут вызывать это прерывание. Состояние сигналов на них сравнивается со старым значением, записанным при последнем чтении PORTB. Несовпадение текущего состояния со старым вызывает прерывание – поднимается флаг RB1F (INTCON < 0>).

Можно сбросить флаг прерывания в программе обработки прерывания, выполнив следующие операции:

· считать PORTB, что закончит условие несоответствия;

· сбросить флажок RBIF.

Прерывание по изменению состояния и программируемое подключение разрядов к высокому уровню этих четырех контактов позволяет создать простой интерфейс клавиатуры.

Опрос PORTB не рекомендуется при использовании прерывания при изменении состояния.

RB0/INT вход внешнего источника прерываний, настраиваемых битом INTEDG (OPTION_REG<6>).

2020-01-14

2020-01-14 245

245