Как правило все современные ОУ выполняются по двухкаскадной схеме. Это позволяет уменьшить число компонентов усилителя, а следовательно и источники дополнительных погрешностей, снизить задержку прохождения сигнала в усилительном тракте, упростить балансировку усилителя и т.д. В связи с этим входной каскад должен обладать как можно большим коэффициентом усиления (свыше 1000), которого невозможно добится применяя базовую схему ДК, т.к. требуемое падение напряжения в коллекторных сопротивлениях врежиме покоя должно было бы составлять несколько десятков вольт.

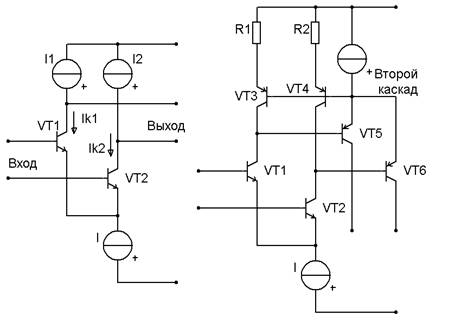

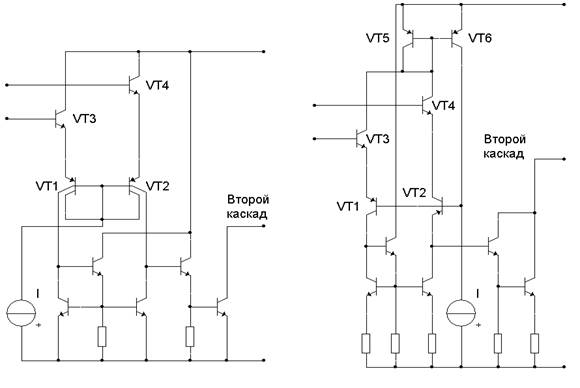

Одно из решений вопроса — замена коллекторных резисторов на источники тока I1, I2 (рис.11,а). Эти источники должны иметь пренебрежимо малую проводимость в сравнении с коллекторной проводимостью транзисторов VT1 и VT2. Как правило усиление такого каскада не зависит от величины тока I. Для практической реализации схемы требуется связать источники тока I1, I2 с основным источником тока I. Обычно этого добиваются, делая так, чтобы эти источники отслеживали коллекторные токи Iк1, Iк2.

На рис.11,б источники I1, I2 выполнены на комплементарных транзисторах VT3, VT4. Необходимое смещение для их объединенных баз отводится с использованием контура ООС через переходы база— эмиттер транзисторов VT5, VT6, второго комплементарного дифференциального каскада.

На рис.11,в контур ОС замкнут через пассивные компоненты (резисторы R3,R4). Эта схема имеет один недостаток — уменьшенный коэффициент усиления.

а) б)

в) г)

Рис.11

Наиболее часто используемая конфигурация показана на рис.11,г. Контур ОС, замкнутый через эмиттерный повторитель VT5, реагирует только на изменения коллекторного тока левого по схеме входного транзистора VT1 и преобразует их в равные изменения коллекторного тока транзистора VT4. Поскольку здесь имеет место инверсия сигнала, данная конфигурация называется инвертором тока. Второй эмиттерный повторитель VT6 уравнивает нагрузку входного каскада. В целом данный каскад обеспечивает также преобразование дифференциального сигнала в однополярный, что необходимо для правильного возбуждения выходною каскада (транзистор VT7), сохраняя при этом наиболее ценные свойства каскада с дифференциальным выходом, такие, например, как чисто дифференциальное усиление и подавление изменений синфазного сигнала.

|

а)

|

б) в)

Рис.12

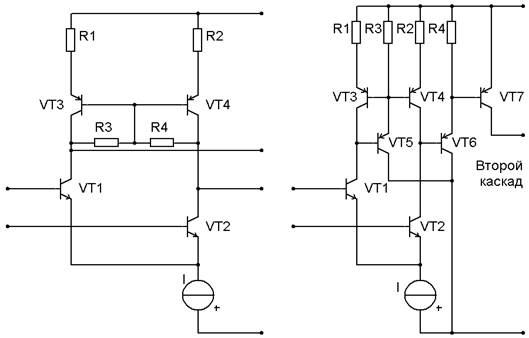

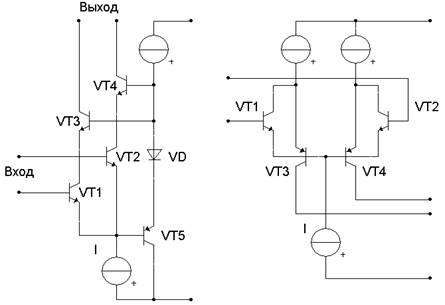

Составной ДК

Каскад, показанный на рис.12,а, является основой наиболее широко используемых интегральных ОУ. Дифференциальный каскад с общей базой (VT1, VT2), которому предшествуют эмиттерные повторители (VT3, VT4), функционально эквивалентен комплементарной модификации базовой схемы. Кажущееся ненужным усложнение схемы исключает трудности, связанные с малым усилением по току боковых интегральных транзисторов pnp-типа, и в дополнение к этому имеет то преимущество, что допускает подачу на вход больших синфазных и дифференциальных напряжений.

Фактическая реализация усилительного каскада призвана подавлять зависимость коллекторных токов входных транзисторов в рабочей точке от технологического разброса коэффициентов усиления по току боковых рпр-транзисторов. На рис.12,6 (ОУ типа LM101A) коэффициент усиления по току каждого pnp-транзистора стабилизирован на значении 4 путем разделения их коллекторов на два сегмента с отношением площадей 4:1 и подключения меньшего сегмента обратно к базе. Коллекторная нагрузка формируется токовым инвертором.

На рис.12,в (ОУ μА741) усиление обоих транзисторов VT1, VT2 не контролируется, и рабочие токи входного каскада стабилизируются контуром ОС, замыкаемым через токовый инвертор (VT5, VT6).

а) б)

в) г)

|

д) е)

Рис.13

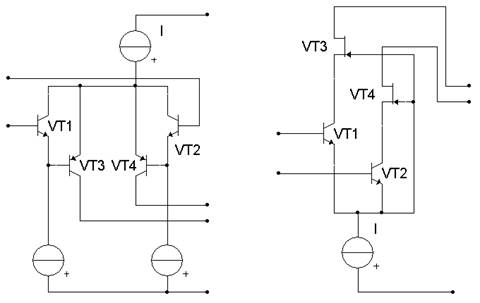

ДК со следящей ОС

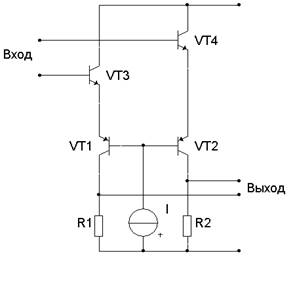

Следящая ОС представляет собой метод, при котором напряжение коллектора или стока отслеживается напряжением на базе или затворе транзистора. Применение этого метода к входному каскаду ОУ влечет за собой повышение КОСС и входного синфазного сопротивления и уменьшение входной синфазной емкости и входного тока смещения.

На рис.13,а дифференциальная каскодная схема со следящей ОС образована входными транзисторами VT1, VT2 и вспомогательными транзисторами VT3, VT4, которые отслеживают напряжение на эмиттерах VT1, VT2 через эмиттерный повторитель VT5 и диод VD. Показанная на рис.13,б комплементарная каскодная схема — всего лишь упрощенный вариант описанной выше схемы.

Представленный на рис.13,в каскад, собранный по схеме Дарлингтона на комплементарных транзисторах, сохраняет преимущества каскада со следящей ОС и в дополнение к этому быстрее отрабатывает большие сигналы за счет больших рабочих токов во внутреннем дифференциальном каскаде (VT3, VT4).

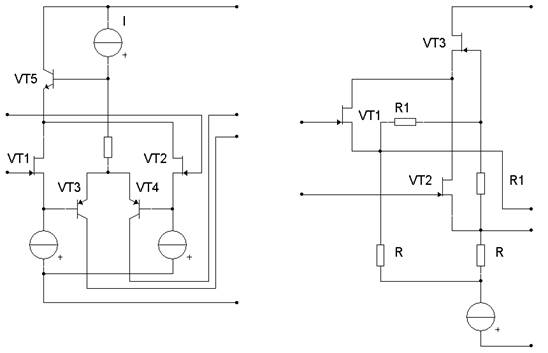

Получению очень простого решения смешанной каскодной схемы, показанной на рис.13,г, способствует отрицательное напряжение затвор — исток полевого транзистора. Этот метод применим также и в каскаде с ПТ на входе.

Для расширения диапазона входных синфазных напряжений подходящим методом является включение входных ПТ по схеме истоковых повтрителей (рис.13,д). Другой пример показан на рис.13,е; резисторы R расщепляют здесь рабочий ток I, а резисторы Rl восстанавливают уровень синфазного напряжения на входе.

2020-01-14

2020-01-14 489

489