Роль выходного каскада ОУ заключается в обеспечении достаточного размаха напряжения и тока на выходе и в изоляции предшествующих каскадов усиления от изменяемой внешней нагрузки. В наиболее часто используемой конфигурации выходной каскад состоит из каскада усиления напряженияи выходного токового бустера.

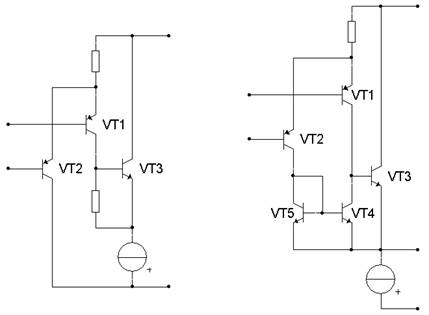

Выходной каскад усиления, показанный на рис. 17, состоит из транзистора VT1,возбуждаемого сигналом, уровень которого отсчитывается от отрицательного напряжения питания, и работающего на источник тока I. Такая конфигурация обладает высоким достижимым усилением и постоянной крутизной,не зависящей от большого размаха выходного напряжения.

Ток, отдаваемый в нагрузку токовым бустером, формируется комплементарным эмиттерным повторителем, состоящим из выходных транзисторов VT1 и VT2,которые смещены в прямом направлении диодами VD1 и VD2. Эмиттерные резисторы R1 и R2устанавливают уровень постоянного тока в режиме покоя, ограничивая мощность, рассеиваемую в этом режиме, и предотвращая неудержимый рост выделяемого тепла.

Коэффициент усиления выходного каскада по напряжению зависит от величины эквивалентного сопротивления r, которое определяется коллекторными проводимостями всех трех транзисторов и внутренней проводимостью источника тока I. Может достигать K=-1000.

ВАХ выходного каскада нелинейна, и выходное сопротивление Rвых не имеет фиксирванного значения. Это является следствием различных условий работы выходного бустера в зависимости от величины и полярности тока.

Различие между значениями выходного сопротивления при отрицательной и положительной полярностях выходного сигнала может достигать значительной величины, особенно у монолитных ОУ, вследствие малого усиления их выходных рпр-транзисторов. На рис.18 показаны различные схемных модификации устраняющие этот недостаток.

|

Рис.17

В схеме рис.18 аиспользован простой каскад, собранный на транзисторах VT2, VT3 по схеме Дарлингтона, в схеме б) добавлен npn-транзистор VT3 схеме в)вместо диода VD1 использован обеспечивающий усиление по току транзистор VT3, чтобы ограничить ток покоя выходного бустера, VD2 включают последовательно с базой VT3. В схеме г) выходному бустеру предшествует эмиттерный повторитель VT3. Полностью активное исполнение диодов VD1 и VD2, представленных комплементарными транзисторами VT3, VT4 показано на рис.18, д. Модификация е) делает возможным выбор произвольного смещения за счет изменения отношения сопротивлений R1/R2

Выходной каскад на рис.18, ж),схема которого собрана на комплементарных транзисторах, имеет дифференциальный вход со стороны баз транзисторов VT1, VT2 и однополярный выход, обеспечивающий усиление по току за счет эмиттерного повторителя VT3. Модификация схемы для монолитного исполнения (рис.18, з) включает в себя токовый инвертор (VT4, VT5),отслеживающий выходной сигнал. В выходном каскаде используется также активная коллекторная нагрузка (схема и); два входа этой схемы удобно использовать для суммирования постоянной и переменной составляющих сигнала в случае организации параллельных каналов. Еще один метод такого суммирования показан на схеме к).Каскодная схема, такая как каскад на транзисторах VT, VT1 на рис.18, л),предназначена для широкополосных ОУ и для ОУ с быстрым установлением. При больших и быстрых изменениях выходного напряжения емкость коллекторного перехода Ск1 транзистора VT1перезаряжается через низковольтный стабилитрон VS и не нагружает предварительный усилительный каскад.

а) б) в)

г) д) е)

Рис.18

|

ж) з)

и) к) л)

Рис.18

2020-01-14

2020-01-14 223

223