Архітектура MAJC розроблена фірмою Sun і призначена для використовування в системах обробки мультимедійних даних і виконання Internet - додатків.

MAJC 5200 складається з двух 128-розрядних VLIW (Very - Long Instruction Word) мікропроцесорних ядра, інтегрованих на одному кристалі. В даному мікропроцесорі реалізовано 4 рівні паралелізму (мультитредова структура кристала, мультитредове виконання програми, VLIW - паралелізм на рівні команд, SIMD обробка даних). Система команд RISC - процесорів орієнтована на потокову обробку мультимедійної інформації і апаратну підтримку високорівневої конструкції мови Java. Сама назва MAJC утворена від " Microprocessor Architecture for Java Computing - микропроцессорна обробка для обчислень на Java". Дана архітектура є тією, що масштабується. На одному кристалі MAJC може розташовуватися декілька ідентичних процесорів залежно від конкретної реалізації, кожний з яких містить від одного до чотирьох функціональних блоків - RISC - процесорів і кеш - команд. Кожний з розташованих на кристалі процесорів може виконувати до 4 команд за такт.

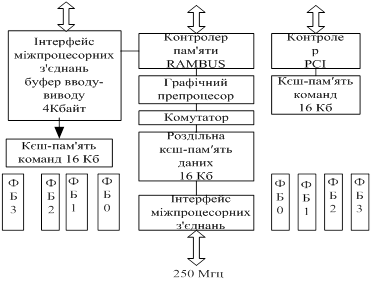

Структурна схема MAJC та призначення функціональних блоків

Крім функціональних блоків і кєшів команд (16 Кб) на кристалі розташовані: загальний для процесорів кєш даних (16 Кб), контролер PCI, контролер Rambus - пам'яті, графічний препроцесор, 64-розрядні високошвидкісні інтерфейси для між процесорних з'єднань і підключення графічної підсистеми, а також комутатор, об'єднуючий процесори і всю решту компонентів кристала.

Малюнок 4. Структурна схема MAJC

Командне слово MAJC об'єднує від однієї до чотирьох 32-розрядних команд, кожна з яких призначена для одного з 4 процесорів. У тому випадку, коли не представляється можливим одночасно задіяти всі процесори, окремі команди можуть бути відсутні, тому командне слово MAJC може мати змінну довжину. Для вказівки кількості команд в слові використовуються його перші два біти: 00 - 1 команда, 01 - 2 команди, 10 - 3 команди, 11 - 4 команди. Призначення команд здійснюється в порядку номерів функціональних блоків.

Один з функціональних блоків (номер 0) відрізняється по виконуваних командах від трьох інших (номери з 1 по 3). Крім АЛП команд, він виконує команди завантаження/збереження і команди переходів. АЛП команди виконуються над даними у форматах: цілочисельному (8-,16-,32-.64 - біт), з фіксованою крапкою (16 біт) і рухомою крапкою (32-,64-бит), а також бітовими послідовностями. Є команди SIMD-обробки пар даних у форматі з фіксованою точкою 16-біт.

Кожний процесор має файл локальних регістрів, логіку управління (декодування) команд, і регістри стану. Є також глобальні регістри доступні для всіх процесорів. Реалізована в мікропроцесорі апаратна підтримка мультітредового виконання програми передбачає можливість одночасного виконання до 4-х потоків команд.

2020-04-20

2020-04-20 129

129