Вступ

Тема реферату "Мікропроцесори архітектури ALPHA, SPARC, MAJC, SHARC" з дисципліни "Мультимікропроцесорні системи".

Мультимікропроцесорні системи (ММПС) - це системи, що мають два й більше компонент, які можуть одночасно виконувати команди. Підпорядкованими процесорами можуть бути спецпроцесори, розраховані на виконання певного типу завдання або процесори широкого застосування. Спецпроцесори - співпроцесори, процесори вводу-виводу.

Мета роботи - розглянути структуру та принцип дії мікропроцесорів архітектури ALPHA, SPARC, MAJC, SHARC.

Мікропроцесори архітектури ALPHA

Концепція розробки даної архітектури отримала назву Spead Daemon - досягнення високої продуктивності за рахунок збільшення тактової частоти при відносно простій логіці функціонування. Перший мікропроцесор ALPHA 21064 (1993 р.) призначався для високопродуктивних робочих станцій і серверів. По нинішній час компанія DEC є лідером при порівнянні продуктивності власних мікропроцесорів і мікропроцесорів фірми Intel. При розробці застосовується концепція Brainiac, яка припускає складний механізм динамічного виконання команд.

Виконання команд мікропроцесора включає наступні цикли - вибірка команд з урахуванням прогнозів переходів, передача даних для команди в пристрій перейменування (відображення) регістрів, виконання перейменування (відображення) регістрів, вибір команд із черг на виконання, виконання команд з фіксованою або плаваючою крапкою, запис результатів виконання.

Структура мікропроцесора 21264 и особливості виконання команд

Для динамічного виконання розглядається відразу 80 команд (більше, ніж у будь-якого іншого мікропроцесора). Після декодування команда потрапляє в необхідну їй чергу. Команди, отримавши необхідні їм операнди для виконання, конкурують за доступ до виконавчих пристроїв і більший пріоритет мають команди, що знаходяться в черзі довше за всіх. Одночасно можуть виконуватися відразу шість команд.

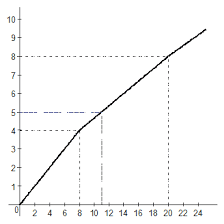

Малюнок 1. Структура мікропроцесора ALPHA 21264

Структура мікропроцесора 21364 у організації ММПС

Наступний представник даного сімейства мікропроцесор 21364, але оскільки в його розробці брали участь відразу декілька фірм (DEC, Compag, Hewlett Packard), основним його власником є фірма Hewlett Packard. Випуск даного мікропроцесора здійснений в 2002-2003 рр. Ядром є ядро мікропроцесора 21264 і внесені різні структурні поліпшення.

Малюнок 2. Структура мікропроцесора ALPHA 21364

Кеш-пам'ять другого рівня є 6-ти входовою множинно-асоціативною, місткістю 1,75 Мб. Контролер пам'яті - 8-канальний, динамічний, тип обслуговуваємой пам'яті - Direct Rambus. Швидкість обміну мікропроцесора з оперативною пам'яттю - 12,8 Гбайт/с. Завдяки вбудованому мережному інтерфейсу спрощується об'єднання мікропроцесорів у високопродуктивну мультипроцесорну систему. Мережний інтерфейс підтримує 4 лінка, швидкість роботи кожного - 6,4 Гбайта/с. Затримка обмінних операцій через лінк, не більше 15 ns. Реалізований протокол когерентності в МПС, а також асинхронний обмін даними.

Малюнок 3. Схема з'єднання 12 мікропроцесорів 21364 в ММПС

2020-04-20

2020-04-20 164

164