Сумісне виробництво фірм Analog Devices і Intel і перший представник сімейства мікропроцесорів Blackfin, з мікросигнальною архітектурою (поєднання в одному мікропроцесорі можливостей сигнальної обробки, SIMD обробки мультимедійних даних і RISC подібного набору команд.

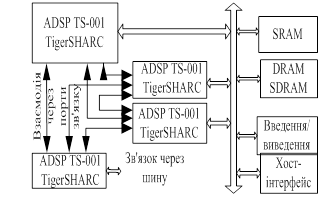

Малюнок 5. Використання ADSP-TS001 в багатопроцесорних системах

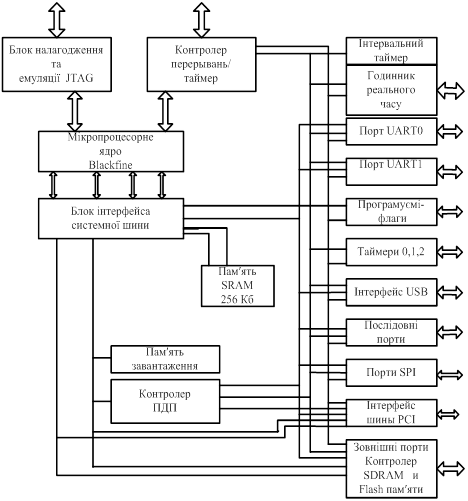

Структура мікропроцесора Blackfin (ADSP-21535)

Ядро ADSP-21535 складається з трьох компонентів: пристрій обчислення адреси, пристрої управління, і пристрої обробки даних. Пристрій обчислення адреси містить два генератори адреси (DAG0, DAG1), використовуючі загальний регістровий файл. Регістровий файл включає 4 набори регістрів: індексний, модифікатор, довжини, бази. Вісім додаткових 32-розрядних регістра можуть використовуватися спільно з основними індексними регістрами як покажчики позицій стека і пам'яті. Пристрій управління містить блок формування послідовності команд, блоки виділення і декодування команд, а також буфер команд циклу (для локального збереження команд з метою скорочення числа звернень до пам'яті команд). Пристрій обробки даних містить 9 обчислювальних пристроїв: два блоки виконання операцій множення з накопиченням, два 40-розрядних АЛП, 4 видео - АЛП і пристрій барабанного зсуву. Обчислювальні пристрої обробляють 8-, 16-, 32-розрядні дані, що містять в регістровому файлі.

На кристалі, крім процесорного ядра, містяться 256 Кб статичної пам'яті, контроллер ПДП, контроллер переривань, блок інтерфейсу системної шини, пам'ять завантаження, таймери, контроллер зовнішньої пам'яті, контролер шини PCI, інтерфейс USB, універсальний асинхронний інтерфейс UART, блок емуляції і відладки JTAG.

Малюнок 6. Структура мікропроцесора Blackfin

У мікропроцесорі реалізована модифікована гарвардська архітектура в комбінації з ієрархічною структурою пам'яті. Вся пам'ять мікропроцесора розглядається як уніфікований адресний простір розміром до 4 Гб. Перший рівень ієрархії пам'яті працює на частоті ядра і має мінімальний час доступу. Місткість пам'яті команд цього рівня - 16 Кб. Пам'ять даних цього рівня (два банки по 16Кб) містить, разом з даними, стек і локальні змінні. До цього ж рівня відноситься внутрішня пам'ять проміжних результатів розміром 4 Кб. Пам'ять першого рівня може бути конфігурована як швидка пам'ять прямого доступу або як кєш-пам'ять. Пам'ять другого рівня - внутрішня SRAM (256 Кб), доступ до якої здійснюється за декілька процесорних тактів. Пам'ять цього рівня є загальною як для команд так і для даних.

Висновок

У роботі були розглянути структурні схеми та архітектура мікропроцесорів архітектури ALPHA, SPARC, MAJC, SHARC, принцип дії.

Література

1. Б.В. Шевкопляс Микропроцессорные структуры. Инженерные решения М.: Радио и связь, 1990

2. В. Шевкопляс Микропроцессорные структуры. Инженерные решения. Дополнение первое. М.: Радио и связь, 1993

3. М. Гук Аппаратные средства IBM PC С. Петербург ²Питер² 2000

4. В. Корнеев, А. Киселев Современные микропроцессоры Санкт-Петербург, ² БХВ - Петербург ² 2003

5. Локазюк В.М. и др Микропроцессоры и микроЭВМ в производственных системах Киев Издательский центр ² Академия ² 2002

6. В.В. Сташин, А.В. Урусов, О.Ф. Мологонцева Проектирование цифровых устройств на однокристальных микроконтроллерах Л. Энергоатомиздат

7. Под ред. А.Д. Викторова Руководство пользователя по сигнальным микропроцессорам семейства ADSP-2100 Санкт - Петербургский государственный электротехнический университет. Санкт - Петербург 1997

8. М. Предко Руководство по микроконтроллерам в 2-х томах М: Постмаркет, 2001

2020-04-20

2020-04-20 138

138