Металлизированные соединения элементов налагают важные ограничения на конструкцию ИМС. В схемах с регулярным расположением блоков, имеющих только короткие связи с соседними блоками, вклад площади проводников в общую площадь кристалла не зависит от степени интеграции. В логических ИМС с нерегулярной структурой увеличивается вклад проводников в общую площадь кристалла с повышением сложности схемы. Это происходит за счет увеличения числа и протяженности связей дальнего порядка, т.е. соединяющих не соседние элементы.

Рассмотрим связь между площадью проводников и числом логических элементов на примере регулярного массива из N элементов, организованных в матрицу I × I = N. На основе этого массива логических элементов реализована схема произвольной логики. Пусть элементы расположены с шагом l, т.е. минимальная длина логической связи l, число выводов – m, а коэффициенты объединения по входам и выходам равны Fi и F0 соответственно. Общее число связей в схеме равно

. (2.1)

. (2.1)

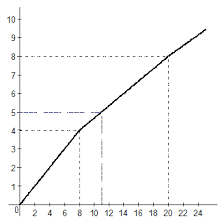

На основе статистики реальных проектов был проведен анализ распределения логических связей по их длине для схем с произвольными логическими функциями. Если измерять длину проводников в единицах l (шаг размещения элементов), то длины проводников в схеме изменяются от 1 до I. Связи с длиной более I шагов практически отсутствуют. В сложных схемах (N ³ 1000) длины логических связей подчиняются определенной статистике. В этом случае зависимость числа связей длиной K от величины K определяется эмпирической формулой

, (2.2)

, (2.2)

причем  , а величина 1 < g < 2.

, а величина 1 < g < 2.

Легко найти коэффициент A:

. (2.3)

. (2.3)

Общая длина всех проводников схемы L:

. (2.4)

. (2.4)

Величина g найдена для класса быстродействующих КМОП-схем на основе обработки статистики распределения связей по длине и равна 1,5. В этом случае

. (2.5)

. (2.5)

Из выражения 2.5 получим площадь связей, приходящихся на один логический элемент:

. (2.6)

. (2.6)

где M – шаг размещения проводников. В свою очередь, шаг размещения элементов связан с площадью проводников. Приняв, что вся площадь элемента покрыта связями, получим

, (2.7)

, (2.7)

где Q – число уровней разводки логических связей. Минимальная площадь на кристалле для одного логического элемента, обеспечивающая проведение всех связей, получается из двух приведенных выше условий:

;

;

. (2.8)

. (2.8)

Согласно формуле (2.8) площадь кристалла должна возрастать значительно быстрее, чем количество логических элементов в БИС. Единственным способом преодолеть это конструктивное ограничение является увеличение числа уровней разводки сигнальных связей. Сохранить отношение площади полупроводниковых приборов ко всей площади кристалла БИС возможно при увеличении числа уровней разводки Q пропорционально  .

.

Совершенствование системы металлизации идет по пути уменьшения шага разводки и наращивания числа уровней соединений. В современных микросхемах число уровней электрических соединений достигает восьми.

2020-04-12

2020-04-12 225

225