|

Это операция применяется в случаях, когда требуется иметь противоположные значения переменной. Противоположное значение переменной называется дополнением этой переменной Символически для НЕ оно обозначается чертой над соответствующей переменной величиной: А=Q.

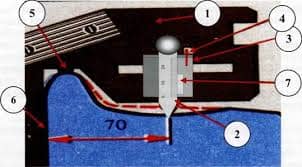

В простейшем случае элемент НЕ инвертор - может быть выполнен на биполярном (или полевом) транзисторе с общим эмиттером (рис. 7, а). Когда на входе А действует сигнал 0, транзистор VT тока" не проводит и напряжение на выходе Q максимально, практически равно напряжению источника питания и соответствует сигналу 1. Если на входе действует положительное напряжение, соответствующее сигналу 1, транзистор VT (n - p - n-типа) отпирается, переходит в режим насыщения и напряжение на выходе Q снижается до уровня 0,1—0,3 В, соответствующее сигналу 0. Таким образом, схема инвертирует входной сигнал. У рассмотренной схемы НЕ много недостатков: малы быстродействие и нагрузочная способность и весьма низка помехоустойчивость. Поэтому на практике используют более сложные схемы. В частности, на рис. 7, б приведена схема инвертора семейства ТТЛ на основе многоэмиттерного транзистора VT1. При напряжении логического 0 на входе А создаются условия для протекания тока в транзисторе VT1 только в цепи перехода эмиттер-база (на рис. 7, б указаны два параллельно соединенных эмиттера, работающих как один), а переход коллектор-база закрыт, вследствие чего нет тока в цепи базы транзистора VT2 и он заперт. При этом на его коллекторе имеется напряжение, близкое к напряжению источника питания. Это напряжение действует на базу транзистора VT3, что приводит к его полному отпиранию. В то же время транзистор VT4 заперт, поскольку на его базу не подается никакого напряжения, так как транзистор VT2 закрыт, ток через него не проходит и на резисторе R2 нет напряжения (которое могло бы открыть транзистор VT4). Таким образом, поскольку транзистор VT3 открыт, а VT4 закрыт, на выходе Q действует положительное напряжение, близкое к напряжению источника питания, что соответствует логической 1. Если на вход А подается напряжение логической 1, то переход эмиттер - база транзистора VT1 запирается, но создаются условия для протекания тока через его переход коллектор - база и тем самым для протекания тока через базу транзистора VT2, что приводит к его отпиранию и переходу в режим насыщения. При этом транзистор VT3 запирается (так как на коллекторе VT2 действует слишком низкое напряжение), а транзистор VT4 отпирается, так как на его базу подается с резистора R2 напряжение в положительной полярности. Таким образом, через малое сопротивление открытого транзистора VT4 выход соединяется с общей шиной «землей» и напряжение на нем оказывается почти нулевым и схема работает как инвертор. Диод VD, включенный на вход А, защищает схему от перегрузки по входу.

В простейшем случае элемент НЕ инвертор - может быть выполнен на биполярном (или полевом) транзисторе с общим эмиттером (рис. 7, а). Когда на входе А действует сигнал 0, транзистор VT тока" не проводит и напряжение на выходе Q максимально, практически равно напряжению источника питания и соответствует сигналу 1. Если на входе действует положительное напряжение, соответствующее сигналу 1, транзистор VT (n - p - n-типа) отпирается, переходит в режим насыщения и напряжение на выходе Q снижается до уровня 0,1—0,3 В, соответствующее сигналу 0. Таким образом, схема инвертирует входной сигнал. У рассмотренной схемы НЕ много недостатков: малы быстродействие и нагрузочная способность и весьма низка помехоустойчивость. Поэтому на практике используют более сложные схемы. В частности, на рис. 7, б приведена схема инвертора семейства ТТЛ на основе многоэмиттерного транзистора VT1. При напряжении логического 0 на входе А создаются условия для протекания тока в транзисторе VT1 только в цепи перехода эмиттер-база (на рис. 7, б указаны два параллельно соединенных эмиттера, работающих как один), а переход коллектор-база закрыт, вследствие чего нет тока в цепи базы транзистора VT2 и он заперт. При этом на его коллекторе имеется напряжение, близкое к напряжению источника питания. Это напряжение действует на базу транзистора VT3, что приводит к его полному отпиранию. В то же время транзистор VT4 заперт, поскольку на его базу не подается никакого напряжения, так как транзистор VT2 закрыт, ток через него не проходит и на резисторе R2 нет напряжения (которое могло бы открыть транзистор VT4). Таким образом, поскольку транзистор VT3 открыт, а VT4 закрыт, на выходе Q действует положительное напряжение, близкое к напряжению источника питания, что соответствует логической 1. Если на вход А подается напряжение логической 1, то переход эмиттер - база транзистора VT1 запирается, но создаются условия для протекания тока через его переход коллектор - база и тем самым для протекания тока через базу транзистора VT2, что приводит к его отпиранию и переходу в режим насыщения. При этом транзистор VT3 запирается (так как на коллекторе VT2 действует слишком низкое напряжение), а транзистор VT4 отпирается, так как на его базу подается с резистора R2 напряжение в положительной полярности. Таким образом, через малое сопротивление открытого транзистора VT4 выход соединяется с общей шиной «землей» и напряжение на нем оказывается почти нулевым и схема работает как инвертор. Диод VD, включенный на вход А, защищает схему от перегрузки по входу.

Существенно повысить быстродействие инвертора и снизить расход энергии питания позволяет применение диодов Шоттки, включаемых параллельно переходу коллектор - база биполярного транзистора (рис. 7, в). Такое соединение называется транзистором Шоттки и обозначается в электронных схемах, как показано на рис. 7, в. Среднее время задержки сигналов в логических элементах ТТЛШ порядка 1,5 нс при средней потребляемой мощности около 20 мВт на один логический элемент.

Применение МОП-транзисторов позволяет почти в 10 раз увеличить число активных элементов на кристалле интегральной микросхемы и более чем в 103 раз уменьшить потребление энергии питания по сравнению с биполярными транзисторами. Однако почти в 10—20 раз уменьшается быстродействие (в первую очередь, из-за больших емкостей на входе и выходе транзисторов и очень высоких входных сопротивлений).

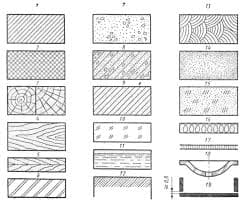

Инвертор на МОП-транзисторах с n-каналами может быть выполнен по схеме, приведенной на рис. 8, а. Транзистор VT1, на затвор которого подается напряжение в отпирающей полярности, выполняет роль резистора (сопротивление которого может быть сделано любым - в пределах от сотен омов до сотен кило-омов - в зависимости от технологии изготовления и напряжения на затворе). Если на входе А действует сигнал 0, то транзистор VT2 закрыт и напряжение на выходе Q практически равно напряжению источника питания, т. е. соответствует напряжению логической 1. Когда на вход А действует положительное напряжение, соответствующее напряжению логической 1, то транзистор VT2 открывается (его сопротивление при этом составляет всего 300 - 500 Ом) и напряжение на выходе Q становится весьма малым (десятые доли-единицы вольт), что соответствует логическому 0. Существенное повышение быстродействия (и снижение потребления энергии питания) достигается при использовании комплиментарной пары КМОП-транзисторов.

Инвертор на МОП-транзисторах с n-каналами может быть выполнен по схеме, приведенной на рис. 8, а. Транзистор VT1, на затвор которого подается напряжение в отпирающей полярности, выполняет роль резистора (сопротивление которого может быть сделано любым - в пределах от сотен омов до сотен кило-омов - в зависимости от технологии изготовления и напряжения на затворе). Если на входе А действует сигнал 0, то транзистор VT2 закрыт и напряжение на выходе Q практически равно напряжению источника питания, т. е. соответствует напряжению логической 1. Когда на вход А действует положительное напряжение, соответствующее напряжению логической 1, то транзистор VT2 открывается (его сопротивление при этом составляет всего 300 - 500 Ом) и напряжение на выходе Q становится весьма малым (десятые доли-единицы вольт), что соответствует логическому 0. Существенное повышение быстродействия (и снижение потребления энергии питания) достигается при использовании комплиментарной пары КМОП-транзисторов.

Схема КМОП-инвертора приведена на рис. 8, б. Если на входе А схемы действует напряжение логического нуля, то транзистор VT1, имеющий р-канал, полностью открыт, поскольку его затвор при этом соединен с общим проводом и поэтому на него подается напряжение в отпирающей полярности относительно истока, соединенного с плюсом источника питания. Транзистор VT2 имеющий n-канал, заперт, вследствие чего напряжение на выходе Q максимально и соответствует напряжению логической 1. Когда на вход А подается положительное напряжение логической 1, то транзистор VT1 запирается, а транзистор VT2 полностью отпирается, вследствие чего напряжение на входе Q становится нулевым. Быстродействие этой схемы по сравнению с предыдущей существенно увеличивается благодаря тому, что заряд-перезаряд паразитных емкостей происходит через весьма малые сопротивления полностью открытых транзисторов VT1 и VT2. Потребление энергии питания снижается до уровня десятых долей микроватта на один элемент потому, что схема потребляет ток, в сущности, только во время переключения, когда один транзистор открывается, другой закрывается. В остальное время — при 0 или 1 — всегда один из транзисторов закрыт и ток от источника питания не потребляется.

Схема КМОП-инвертора приведена на рис. 8, б. Если на входе А схемы действует напряжение логического нуля, то транзистор VT1, имеющий р-канал, полностью открыт, поскольку его затвор при этом соединен с общим проводом и поэтому на него подается напряжение в отпирающей полярности относительно истока, соединенного с плюсом источника питания. Транзистор VT2 имеющий n-канал, заперт, вследствие чего напряжение на выходе Q максимально и соответствует напряжению логической 1. Когда на вход А подается положительное напряжение логической 1, то транзистор VT1 запирается, а транзистор VT2 полностью отпирается, вследствие чего напряжение на входе Q становится нулевым. Быстродействие этой схемы по сравнению с предыдущей существенно увеличивается благодаря тому, что заряд-перезаряд паразитных емкостей происходит через весьма малые сопротивления полностью открытых транзисторов VT1 и VT2. Потребление энергии питания снижается до уровня десятых долей микроватта на один элемент потому, что схема потребляет ток, в сущности, только во время переключения, когда один транзистор открывается, другой закрывается. В остальное время — при 0 или 1 — всегда один из транзисторов закрыт и ток от источника питания не потребляется.

Рис. 7. Логический элемент НЕ, выполненный на обычном биполярном транзисторе (а); многоэмиттерном транзисторе с дополнительным усилителем (б); Транзистор Шоттки и его условное графическое изображение в электронных схемах (в).

Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б).

2020-05-21

2020-05-21 283

283